一种无外挂电容的驱动buffer电路及缓冲器

技术领域

1.本发明涉及驱动buffer电路,特别是涉及一种无外挂电容的驱动buffer电路及缓冲器。

背景技术:

2.图1是现有技术中一个典型的lcd_driver驱动电路的示意图。不失一般性,图中仅画出了一小部分像素点:每行只有2个pixel,一共4行;其中每个pixel有3个tft开关和电容(也就是液晶分子),分别对应r、g、b。每一行mos开关的gate由一根gck信号统一控制,这是一个高压控制信号,称为gate线,典型值是+/-12v。每一列mos开关的一端由一根s线控制,每根s线均由一个buffer驱动,称为data线。通过不停的发送数据,改变每根s线的电压,从而实现画面的显示和刷新。

3.所有pixel电容的另一端,全部连接到一起,称为vcom端(公共端),由一个大buffer驱动,称为vcom_buffer。毫无疑问,vcom具有最重的负载,因为整个面板的电容(有用电容和寄生电容)全部相对于vcom这个公共端。一般来说,小尺寸面板总电容大约是5-10nf左右,中等尺寸面板总电容50-100nf。当屏幕工作时,面板电容不停充放电,对vcom_buffer有很大抽电流和灌电流的行为,因此对vcom_buffer的带载能力和响应速度提出了很高的要求。一般来说,vcom_buffer必须要挂片外电容,以提供足够的瞬态响应能力,如图1所示,这是现在主流技术方案。

4.但是,片外电容带来了成本、可靠性、以及pcb布线及面积等问题,目前的技术潮流是朝着尽量少使用片外器件的方向发展。尤其是小尺寸可穿戴设备,空间非常紧张,需要尽可能精简物料,目标是做到“零电容”。因为总的面板电容相对较小,小尺寸屏也是最有可能实现“零电容”目标的。

5.图1仅以lcd_driver芯片中的vcom缓冲器为例说明问题,类似的例子还包括触控芯片中的vref_tp缓冲器,vcg_tp缓冲器等。例如在触摸屏的模拟前端检测电路,是由上百个ca放大器和积分器组成的阵列,ca放大器和积分器都是开关电容电路,它们使用同一个驱动buffer,因此buffer具有非常大的容性负载。

6.因此,迫切需要一种不使用片外电容的驱动buffer电路,并且能够解决稳定性和瞬态响应速度的问题。

技术实现要素:

7.针对现有技术中存在的缺陷,本发明的目的在于提供一种无外挂电容的驱动buffer电路及缓冲器,驱动很大的容性负载时,可以不使用片外电容,仍然能够保持很好的稳定性和响应速度。

8.为了达到上述目的,本发明所采用的具体技术方案如下:

9.一种无外挂电容的驱动buffer电路,包括运放、若干电阻和多路选择器,所述运放为二级结构,包括输入级和输出级,输出级设有若干输出端,每个输出端分别设有独立的使

能开关,分别连接有不同电阻值的电阻支路,所述多路选择器的输入引脚分别连接各个电阻支路,输出引脚与所述运放连接。

10.优选的,所述运放为class-ab运放。

11.优选的,所述电阻支路包括一条无电阻的支路。

12.优选的,所述多路选择器包括多个开关,开关与输入引脚连接,通过开关的关断选择不同的反馈点。

13.优选的,所述电阻的阻值相同。

14.优选的,所述电阻的阻值不同。

15.优选的,所述电阻的数量为n,运放的输出级有n个输出端,所述多路选择器的输入引脚设有n个。

16.一种缓冲器,包括任一项所述的无外挂电容的驱动buffer电路。

17.优选的,所述缓冲器为lcd_driver芯片中的vcom缓冲器或触控芯片中的vref_tp缓冲器、vcg_tp缓冲器。

18.本发明的有益效果在于:驱动很大的容性负载时,可以不使用片外电容,仍然能够保持很好的稳定性和响应速度。

附图说明

19.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

20.图1是现有技术中一个典型的lcd_driver驱动电路的示意图;

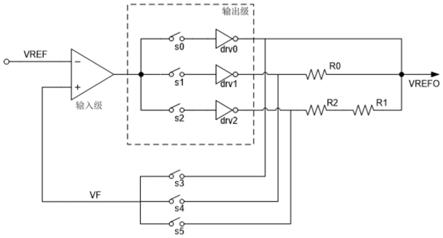

21.图2是本发明一种无外挂电容的驱动buffer电路一个实施例的结构示意图;

22.图3是具有3个输出端的class-ab运放的电路结构示意图;

23.图4是图2的其中一个开关策略的示意图及其对应的小信号等效电路示意图。

具体实施方式

24.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的其他实施例,都属于本发明保护的范围。

25.本发明提出了一种无外挂电容的驱动buffer电路,包括运放、若干电阻和多路选择器,所述运放为二级结构,包括输入级和输出级,输出级设有若干输出端,每个输出端分别设有独立的使能开关,分别连接有不同电阻值的电阻支路,所述多路选择器的输入引脚分别连接各个电阻支路,输出引脚与所述运放连接。

26.优选的,所述运放为class-ab运放。

27.优选的,所述电阻支路包括一条无电阻的支路。所述电阻的阻值相同或不同。电阻的数量为n,运放的输出级有n个输出端,所述多路选择器的输入引脚设有n个,n为大于1的整数。

28.优选的,所述多路选择器包括多个开关,开关与输入引脚连接,通过开关的关断选择不同的反馈点。

29.如图2-图3所示,以下举例对本发明进行详细阐述。

30.本发明提出了一种无外挂电容的驱动buffer的电路,它由一个3输出的class-ab的运放,以及一些电阻(图中的r0/r1/r2)和一个多路选择器构成。其中class-ab的运放为2级结构:输入级和输出级(又称为驱动级),输出级有3个输出,每个输出尺寸完全相同,且具有独立的使能开关,具体电路如图3所示。

31.输出级drv0的使能开关是s0,输出无电阻。

32.输出级drv1的使能开关是s1,输出串接电阻r0。

33.输出级drv2的使能开关是s2,输出串接电阻r1和r2。

34.s3/s4/s5构成一个3:1的多路选择开关,用于选择不同的反馈点。

35.输出路径上串联的电阻,目的是与负载电容(很大,但又比片外电容小2个数量级)形成左半平面的零点,实现零点补偿。这个零点能够增大相位裕度和带宽,解决无外挂电容条件下的稳定性问题。

36.因此3个开关s0/s1/s2用于选择输出级,3个开关s3/s4/s5用于选择不同的反馈点,这6个开关是完全独立的,可以实现灵活多变的配置方式,以适应于不同的负载电容大小和场合。举例来说,假设r0=r1=r2=30ohm:

37.对于本发明图2所示的结构,至少包含一条无电阻的支路,通过选择编号1的组合,

即s0+s3的开关组合,同样实现了无零点补偿,但是在此构型下功率管输出没有任何电阻,不存在功率管被电阻限流的问题,因此在同等功率管尺寸下,图2所示结构具有更快的充放电速度。

38.当觉得s0+s3的组合只有一组功率管drv0,充放电速度还不太够时,可以进一步选择s0+s1+s3或者s0+s1+s2+s3的组合。虽然drv1输出因为串联了电阻r0而导致过流能力有所下降,drv2输出也因为串联了电阻r1+r2而导致过流能力有所下降,但是这种下降只是相对的。将drv0+drv1+drv2全并联上,驱动能力还是能大大提高的,虽然没有3x的效果,>2x的效果是可以实现的。

39.同样的,当需要30ohm的零点补偿电阻方案时,图2可以选择编号4,即s1+s4。本发明没有多余的电阻串联在功率管路径上,过流能力更强,充放电速度更快。

40.下面对编号5的零点补偿电阻进行理论分析:

41.如图4(a)所示,是图2方案采用编号5的开关策略后的电路。图4(b)是相应的小信号等效电路,其中输入级的参数用标号“1”所表示,输出级的参数用标号“2”所表示。经过推导,环路增益表达式如下:

[0042][0043]

其中:

[0044]

a0=gm1

·

gm2

·

ro1

·

ro2

[0045][0046]

这里,p1是主极点,位于运放内部(输入级的输出);p2为次极点,位于运放外部(驱动级的输出)。ro2为驱动级功率管内阻,通常为几百ohm级别,而r为几十ohm级别。

[0047]

从表达式可以看到,整个效果相当于是2个功率管并联(因此输出阻抗减半:ro2/2),而零点补偿电阻相当于减半(r/2)。

[0048]

经过简单推导,可以证明相位裕度的表达式为:

[0049][0050]

假设对于编号4的组合(s1+s4)有:

[0051]

wz=2gbw,wp2=gbw/4,则pm=90

°

+atan(1/2)-atran(4)=40.6

°

[0052]

当切换到编号5的组合(s1+s0+s4)有:

[0053]

wz=4gbw,wp2=gbw/2,则pm=90

°

+atan(1/4)-atran(2)=40.6

°

[0054]

可见,当切换到编号5的组合后,虽然等效零点电阻减半了,导致零点频率加倍了,但相位裕度却没有降低,因为极点频率p2也同样的加倍了!

[0055]

图2中以3个输出支路为例说明了专利的核心思想,实际上不限于支路的个数,2个或者n个支路都是可以的,多路选择器需要相应的改变。

[0056]

本发明还提出了一种缓冲器,包括任一项所述的无外挂电容的驱动buffer电路。所述缓冲器为lcd_driver芯片中的vcom缓冲器或触控芯片中的vref_tp缓冲器、vcg_tp缓冲器。

[0057]

本发明的有益效果在于:

[0058]

1)实现了驱动buffer的“零电容”设计;

[0059]

2)可以非常灵活的控制零点的大小,以适应不同的负载电容大小;

[0060]

3)还可以非常灵活的控制驱动管的个数,以适应不同的建立速度要求;

[0061]

4)没有多余的电阻串联在功率管电流路径上,因此驱动能力无损失;

[0062]

5)方案简洁,易于实施,功耗/面积代价小。

[0063]

以上述依据本发明的理想实施例为启示,通过上述的说明内容,本领域技术人员完全可以在不偏离本发明技术思想的范围内,进行多样的变更以及修改。本发明的技术性范围并不局限于说明书上的内容,必须要根据权利要求书范围来确定其技术性范围。