1.本公开涉及显示技术领域,具体而言,涉及一种显示面板及显示装置。

背景技术:

2.相关技术中,像素驱动电路一般包括有存储电容和驱动晶体管,存储电容连接驱动晶体管的栅极,用于存储数据信号,以在发光阶段驱动驱动晶体管输出驱动电流。相关技术中,不同子像素的存储电容一般设置较大,用以弥补寄生电容造成的数据信号损失,致使显示面板的尺寸受限。

3.需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

技术实现要素:

4.本公开的目的在于克服上述现有技术的不足,提供一种显示面板及显示装置。

5.根据本公开的一个方面,提供一种显示面板,所述显示面板包括像素单元,所述像素单元包括多个子像素,所述子像素包括像素驱动电路,所述像素驱动电路包括存储电容和驱动晶体管,所述存储电容的第一电极连接所述驱动晶体管的栅极,所述存储电容的第二电极连接所述驱动晶体管的第一极;所述显示面板还包括:衬底基板;有源层,位于所述衬底基板的一侧,所述有源层包括多个有源部,所述有源部用于形成子像素中存储电容的第一电极;第一导电层,位于所述衬底基板和所述有源层之间,所述第一导电层包括多个导电部,所述导电部用于形成子像素中存储电容的第二电极,任意所述导电部在所述衬底基板的正投影与同一子像素中的所述有源部在所述衬底基板的正投影部分交叠,且与相邻子像素中的所述有源部在所述衬底基板的正投影分离;其中,同一像素单元中,任意两个子像素具有的所述交叠面积大小不同,且所述交叠面积较大的子像素中驱动晶体管沟道区的宽长比大于所述交叠面积较小的子像素中驱动晶体管沟道区的宽长比。

6.在本公开的一种示例性实施例中,所述多个子像素包括r子像素、g子像素、b子像素、w子像素;所述多个有源部包括第一有源部、第二有源部、第三有源部和第四有源部,所述第一有源部用于形成所述r子像素中存储电容的第一电极,所述第二有源部用于形成所述g子像素中存储电容的第一电极,所述第三有源部用于形成所述b子像素中存储电容的第一电极,所述第四有源部分别用于形成所述w子像素中存储电容的第一电极;所述多个导电部包括第一导电部、第二导电部、第三导电部、第四导电部,所述第一导电部用于形成所述r子像素中存储电容的第二电极,所述第二导电部用于形成所述g子像素中存储电容的第二电极,所述第三导电部用于形成所述b子像素中存储电容的第二电极,所述第四导电部用于形成所述w子像素中存储电容的第二电极;其中,所述第一导电部在所述衬底基板的正投影与所述第一有源部在所述衬底基板的正投影具有第一交叠面积,所述第二导电部在所述衬底基板的正投影与所述第二有源部在所述衬底基板的正投影具有第二交叠面积,所述第三导电部在所述衬底基板的正投影与所述第三有源部在所述衬底基板的正投影具有第三交

叠面积,所述第四导电部在所述衬底基板的正投影与所述第四有源部在所述衬底基板的正投影具有第四交叠面积,所述第一交叠面积、所述第二交叠面积、所述第三交叠面积、所述第四交叠面积依次减小。

7.在本公开的一种示例性实施例中,所述第一交叠面积与所述第四交叠面积之比大于1.5且小于2.5。

8.在本公开的一种示例性实施例中,所述第一交叠面积小于所述第三交叠面积与所述第四交叠面积之和。

9.在本公开的一种示例性实施例中,所述r子像素中驱动晶体管的沟道区具有第一宽长比,所述g子像素中驱动晶体管的沟道区具有第二宽长比,所述b子像素中驱动晶体管的沟道区具有第三宽长比,所述w子像素中驱动晶体管的沟道区具有第四宽长比,所述第一宽长比大于所述第三宽长比与所述第四宽长比之和,且所述第二宽长比小于所述第三宽长比与所述第四宽长比之和。

10.在本公开的一种示例性实施例中,所述显示面板包括多个所述像素单元,多个所述像素单元在第一方向和第二方向阵列分布,所述第一方向与所述第二方向相交,其中,同一像素单元中,所述第一有源部在所述衬底基板的正投影、所述第四有源部在所述衬底基板的正投影、所述第三有源部在所述衬底基板的正投影、所述第二有源部在所述衬底基板的正投影沿所述第一方向依次排列,所述第一导电部、所述第四导电部、所述第三导电部、所述第二导电部与所述第一有源部、所述第四有源部、第三有源部、所述第二有源部一一对应。

11.在本公开的一种示例性实施例中,所述显示面板还包括:第三导电层,位于所述有源层背离所述衬底基板的一侧,所述第三导电层包括:多个第五导电部,所述第五导电部在所述衬底基板的正投影与所述第一有源部在所述衬底基板的正投影部分交叠且具有第五交叠面积,所述第五导电部通过过孔电连接所述第一导电部;多个第六导电部,所述第六导电部在所述衬底基板的正投影与所述第二有源部在所述衬底基板的正投影部分交叠且具有第六交叠面积,所述第六导电部通过过孔电连接所述第二导电部;多个第七导电部,所述第七导电部在所述衬底基板的正投影与所述第三有源部在所述衬底基板的正投影部分交叠且具有第七交叠面积,所述第七导电部通过过孔电连接所述第三导电部;多个第八导电部,所述第八导电部在所述衬底基板的正投影与所述第四有源部在所述衬底基板的正投影部分交叠且具有第八交叠面积,所述第八导电部通过过孔电连接所述第四导电部;其中,所述第五交叠面积、所述第六交叠面积、所述第七交叠面积、所述第八交叠面积依次减小。

12.在本公开的一种示例性实施例中,所述第五交叠面积与所述第一交叠面积相同、所述第六交叠面积与所述第二交叠面积相同、所述第七交叠面积与所述第三交叠面积相同、所述第八交叠面积与所述第四交叠面积相同。

13.在本公开的一种示例性实施例中,所述像素单元包括与所述r子像素、所述g子像素、所述b子像素、所述w子像素一一对应的第一像素驱动电路、第二像素驱动电路、第三像素驱动电路和第四像素驱动电路,所述第一像素驱动电路包括第一驱动晶体管,所述第二像素驱动电路包括第二驱动晶体管、所述第三像素驱动电路包括第三驱动晶体管、所述第四像素驱动电路包括第四驱动晶体管;所述有源层还包括:多个第五有源部,所述第五有源部在所述衬底基板的正投影与所述第一导电部在所述衬底基板的正投影部分交叠,所述第

五有源部包括沿所述第二方向依次连接的第一子有源部、第二子有源部和第三子有源部,所述第二子有源部用于形成所述第一驱动晶体管的沟道区,所述第一子有源部位于所述第一有源部和所述第二子有源部之间且通过过孔电连接所述第五导电部;多个第六有源部,所述第六有源部在所述衬底基板的正投影与所述第二导电部在所述衬底基板的正投影部分交叠,所述第六有源部包括沿所述第二方向依次连接的第四子有源部、第五子有源部、第六子有源部,所述第五子有源部用于形成所述第二驱动晶体管的沟道区,所述第四子有源部位于所述第二有源部和所述第五子有源部之间且通过过孔电连接所述第六导电部;多个第七有源部,所述第七有源部在所述衬底基板的正投影与所述第三导电部在所述衬底基板的正投影部分交叠,所述第七有源部包括沿所述第二方向依次连接的第七子有源部、第八子有源部、第九子有源部,所述第八子有源部用于形成所述第三驱动晶体管的沟道区,所述第七子有源部位于所述第三有源部和所述第八子有源部之间且通过过孔电连接所述第七导电部;多个第八有源部,所述第八有源部在所述衬底基板的正投影与所述第四导电部在所述衬底基板的正投影部分交叠,所述第八有源部包括沿所述第二方向依次连接的第十子有源部、第十一子有源部、第十二子有源部,所述第十一子有源部用于形成所述第四驱动晶体管的沟道区,所述第十子有源部位于所述第四有源部和所述第十一子有源部之间且通过过孔电连接所述第八导电部;所述显示面板还包括:第二导电层,位于所述有源层和所述第三导电层之间,所述第二导电层包括:多个第九导电部,所述第九导电部在所述衬底基板的正投影覆盖所述第二子有源部在所述衬底基板的正投影,所述第九导电部的部分结构用于形成所述第一驱动晶体管的栅极;多个第十导电部,所述第十导电部在所述衬底基板的正投影覆盖所述第五子有源部在所述衬底基板的正投影,所述第十导电部的部分结构用于形成与所述第二驱动晶体管的栅极;多个第十一导电部,所述第十一导电部在所述衬底基板的正投影覆盖所述第八子有源部在所述衬底基板的正投影,所述第十一导电部的部分结构用于形成所述第三驱动晶体管的栅极;多个第十二导电部,所述第十二导电部在所述衬底基板的正投影覆盖所述第十一子有源部在所述衬底基板的正投影,所述第十二导电部的部分结构用于形成所述第四驱动晶体管的栅极。

14.在本公开的一种示例性实施例中,所述第九导电部在所述衬底基板的正投影与所述第三子有源部在所述衬底基板的正投影的交叠区域沿所述第一方向的宽度与沿所述第二方向的长度具有第一宽长比;所述第十导电部在所述衬底基板的正投影与所述第五子有源部在所述衬底基板的正投影的交叠区域沿所述第一方向的宽度与沿所述第二方向的长度具有第二宽长比;所述第十一导电部在所述衬底基板的正投影与所述第八子有源部在所述衬底基板的正投影的交叠区域沿所述第一方向的宽度与沿所述第二方向的长度具有第三宽长比;所述第十二导电部在所述衬底基板的正投影与所述第三子有源部在所述衬底基板的正投影的交叠区域沿所述第一方向的宽度与沿所述第二方向的长度具有第四宽长比;其中,所述第一宽长比、所述第二宽长比、所述第三宽长比、所述第四宽长比依次减小。

15.在本公开的一种示例性实施例中,所述第一驱动晶体管的第二极、所述第二驱动晶体管的第二极、所述第三驱动晶体管的第二极、所述第四驱动晶体管的第二极的均连接第一电源线;所述第一导电层还包括:多个第十三导电部,所述第十三导电部在所述衬底基板的正投影沿所述第一方向延伸,同一像素单元中,所述第十三导电部在所述衬底基板的正投影、所述第六有源部在所述衬底基板的正投影、所述第一有源部在所述衬底基板的正

投影沿所述第二方向依次分布;所述第三导电层还包括:多个第一电源线,所述第一电源线在所述衬底基板的正投影沿所述第二方向延伸,同一像素单元中,所述第一电源线在所述衬底基板的正投影位于所述第一导电部在所述衬底基板的正投影远离所述第四导电部在所述衬底基板的正投影的一侧,所述第一电源线通过过孔电连接所述第十三导电部;多个第十四导电部,所述第十四导电部连接所述第一电源线,所述第十四导电部在所述衬底基板的正投影沿所述第一方向延伸且与所述第三子有源部在所述衬底基板的正投影部分交叠,所述第十四导电部还通过过孔电连接所述第三子有源部;多个第十五导电部,多个所述第十五导电部在所述衬底基板的正投影沿所述第二方向延伸且沿所述第一方向间隔分布,同一像素单元中,所述第六子有源部在所述衬底基板的正投影、所述第九子有源部在所述衬底基板的正投影、所述第十二子有源部在所述衬底基板的正投影分别与对应所述第十五导电部在所述衬底基板的正投影部分交叠,且在交叠区域通过过孔电连接。

16.在本公开的一种示例性实施例中,所述第二导电层还包括:多个第十六导电部,在所述衬底基板的正投影沿所述第二方向延伸且沿所述第一方向间隔分布,同一像素单元中,所述第十六导电部在所述衬底基板的正投影位于所述第一导电部在所述衬底基板的正投影远离所述第四导电部在所述衬底基板的正投影的一侧,所述第十六导电部在所述衬底基板的正投影与所述第一电源线在所述衬底基板的正投影部分交叠,且所述第十六导电部通过过孔连接所述第一电源线。

17.在本公开的一种示例性实施例中,所述像素单元包括与所述r子像素、所述g子像素、所述b子像素、所述w子像素一一对应的第一像素驱动电路、第二像素驱动电路、第三像素驱动电路和第四像素驱动电路,所述第一像素驱动电路、所述第二像素驱动电路、所述第三像素驱动电路、所述第四像素驱动电路均包括第二晶体管和第三晶体管,所述第二晶体管的第一极连接数据信号线,第二极连接所述驱动晶体管的栅极,控制端连接第一栅极驱动信号线;所述第三晶体管的第一极连接所述驱动晶体管的第一极,第二极连接参考信号线,控制端连接第二栅极驱动信号线;所述有源层还包括:多个第九有源部,一一对应设置于所述第一像素驱动电路中,所述第九有源部用于形成所述第一像素驱动电路中所述第二晶体管的沟道区;多个第十有源部,一一对应设置于所述第二像素驱动电路中,所述第十有源部用于形成所述第二像素驱动电路中所述第二晶体管的沟道区;多个第十一有源部,一一对应地设置于所述第三像素驱动电路中,所述第十一有源部用于形成所述第三像素驱动电路中所述第二晶体管的沟道区;多个第十二有源部,一一对应地设置于所述第四像素驱动电路中,所述第十二有源部用于形成所述第四像素驱动电路中所述第二晶体管的沟道区;多个第十三有源部,所述第十三有源部连接于所述第九有源部与所述第一有源部之间;多个第十四有源部,所述第十四有源部连接于所述第十有源部与所述第二有源部之间;多个第十五有源部,所述第十五有源部连接于所述第十一有源部所述第三有源部之间;多个第十六有源部,所述第十六有源部连接于所述第十二有源部与所述第四有源部之间;多个第十七有源部,一一对应地设置于所述像素驱动电路中,所述多个第十七有源部在所述衬底基板的正投影沿所述第二方向延伸且沿所述第一方向间隔分布,所述第十七有源部包括沿所述第二方向依次连接的第十三子有源部、第十四子有源部和第十五子有源部,所述第十四子有源部用于形成所述第三晶体管的沟道区,同一像素单元中,多个所述第十三子有源部分别通过过孔与所述第一导电部、所述第二导电部、所述第三导电部和所述第四导电

部对应连接;所述第一导电层还包括:多个第十七导电部,所述第十七导电部在所述衬底基板的正投影沿所述第一方向延伸且间隔分布,所述第十七导电部在所述衬底基板的正投影位于所述第十七有源部在所述衬底基板的正投影远离所述第一导电部在所述衬底基板的正投影一侧,一个所述像素单元包括两个所述第十七导电部,所述第十七导电部分别通过过孔连接相邻两个所述第十五子有源部;所述显示面板还包括:第二导电层,位于所述有源层背离所述衬底基板的一侧,所述第二导电层包括:多个所述第一栅极驱动信号线,在所述衬底基板的正投影沿所述第一方向延伸且在所述第二方向间隔分布,所述第一栅极驱动信号线在所述衬底基板的正投影与所述第一导电部、所述第二导电部、所述第三导电部和所述第四导电部在所述衬底基板的正投影均不交叠,且所述第一栅极驱动信号线在所述衬底基板的正投影部分覆盖所述第九有源部在所述衬底基板的正投影、部分覆盖所述第十有源部在所述衬底基板的正投影、部分覆盖所述第十一有源部在所述衬底基板的正投影、部分覆盖所述第十二有源部在所述衬底基板的正投影,所述第一栅极驱动信号线的部分结构用于形成所述第二晶体管的栅极;多个所述第二栅极驱动信号线,在所述衬底基板的正投影沿所述第一方向延伸且在所述第二方向间隔分布,所述第二栅极驱动信号线在所述衬底基板的正投影部分覆盖所述第十四子有源部在所述衬底基板的正投影,所述第二栅极驱动信号线的部分结构形成所述第三晶体管的栅极,且所述第一导电部、所述第二导电部、所述第三导电部和所述第四导电部在所述衬底基板的正投影位于所述第一栅极驱动信号线在所述衬底基板的正投影和所述第二栅极驱动信号线在所述衬底基板的正投影之间;第三导电层,位于所述第二导电层背离所述衬底基板的一侧,所述第三导电层包括:多个所述数据信号线,多个所述数据信号线在所述衬底基板的正投影沿所述第二方向延伸且在所述第一方向间隔分布,多个所述数据信号线与所述r子像素、所述g子像素、所述b子像素、所述w子像素一一对应,且同一像素单元中,两个所述数据信号线在所述衬底基板的正投影位于所述第一有源部和所述第四有源部在所述衬底基板的正投影之间,两个所述数据信号线在所述衬底基板的正投影位于所述第二有源部和所述第三有源部在所述衬底基板的正投影之间,其中,所述第十三有源部、所述第十四有源部、所述第十五有源部、所述第十六有源部分别通过过孔电连接对应所述数据信号线。多个所述参考信号线,在所述衬底基板的正投影沿所述第二方向延伸且沿所述第一方向间隔分布,同一像素单元中,所述参考信号线在所述衬底基板的正投影位于所述第三导电部在所述衬底基板的正投影和所述第四导电部在所述衬底基板的正投影之间;多个第十八导电部,所述第十八导电部在所述衬底基板的正投影沿所述第一方向延伸,一个所述像素单元包括一个所述第十八导电部且所述第十八导电部与所述参考信号线相交,所述第十八导电部在所述衬底基板的正投影与所述第十七导电部在所述衬底基板的正投影部分交叠,且分别通过过孔连接相邻所述第十七导电部。

18.在本公开的一种示例性实施例中,所述第二导电层还包括:多个第十九导电部,在所述衬底基板的正投影沿所述第二方向延伸且在所述第一方向间隔分布,所述第十九导电部在所述衬底基板的正投影位于所述第三导电部在所述衬底基板的正投影和所述第四导电部在所述衬底基板的正投影之间,所述第十九导电部在所述衬底基板的正投影与所述参考信号线在所述衬底基板的正投影部分交叠,所述第十九导电部通过过孔连接所述参考信号线。

19.根据本公开的第二方面,还提供一种显示装置,包括本公开任一实施例所述的显

示面板。

20.本公开提供的显示面板,像素单元中各子像素的存储电容的面积大小不同,各子像素的存储电容的面积大小在匹配各子像素中驱动晶体管的沟道区的宽长比的同时,能够保证不同子像素间数据信号的损失量相同即可,从而无需按照驱动电流最大的子像素来确定存储电容的数值,由此可减小各子像素的存储电容的占用空间,提高了显示面板的空间利用率,从而有利于提高显示面板的分辨率。

21.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。

附图说明

22.此处的附图被并入说明书中并构成本说明书的一部分,示出了符合本公开的实施例,并与说明书一起用于解释本公开的原理。显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

23.图1为根据本公开一种实施方式显示面板中像素驱动电路的电路结构示意图;

24.图2为图1所示像素驱动电路的驱动时序图;

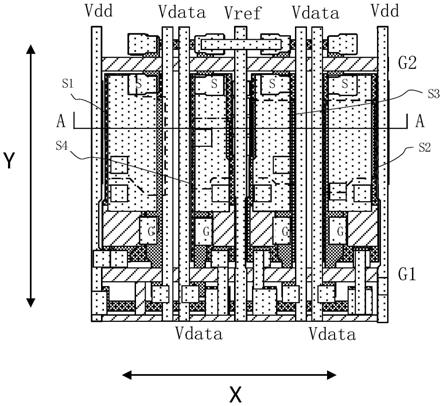

25.图3为根据本公开一种实施方式的显示面板的结构版图;

26.图4为图3中第一导电层的结构版图;

27.图5为图3中有源层的结构版图;

28.图6为图3中第一导电层和有源层的结构版图;

29.图7为图3中第二导电层的结构版图;

30.图8为图3中第三导电层的结构版图;

31.图9为图3中有源层和第二导电层的结构版图;

32.图10为图3中有源层和第三导电层的结构版图;

33.图11为根据本公开一种实施方式的仿真结果图;

34.图12为根据本公开一种实施方式的存储电容的剖视图;

35.图13为图3中沿aa方向的剖视图。

具体实施方式

36.现在将参考附图更全面地描述示例实施方式。然而,示例实施方式能够以多种形式实施,且不应被理解为限于在此阐述的实施方式;相反,提供这些实施方式使得本公开将全面和完整,并将示例实施方式的构思全面地传达给本领域的技术人员。图中相同的附图标记表示相同或类似的结构,因而将省略它们的详细描述。此外,附图仅为本公开的示意性图解,并非一定是按比例绘制。

37.虽然本说明书中使用相对性的用语,例如“上”“下”来描述图标的一个组件对于另一组件的相对关系,但是这些术语用于本说明书中仅出于方便,例如根据附图中所述的示例的方向。能理解的是,如果将图标的装置翻转使其上下颠倒,则所叙述在“上”的组件将会成为在“下”的组件。当某结构在其它结构“上”时,有可能是指某结构一体形成于其它结构上,或指某结构“直接”设置在其它结构上,或指某结构通过另一结构“间接”设置在其它结

构上。

38.用语“一个”、“一”、“该”、“所述”和“至少一个”用以表示存在一个或多个要素/组成部分/等;用语“包括”和“具有”用以表示开放式的包括在内的意思并且是指除了列出的要素/组成部分/等之外还可存在另外的要素/组成部分/等;用语“第一”、“第二”和“第三”等仅作为标记使用,不是对其对象的数量限制。

39.图1为根据本公开一种实施方式显示面板中像素驱动电路的电路结构示意图。该像素驱动电路可以包括:开关晶体管t2、驱动晶体管t1、存储电容c、开关晶体管t3。开关晶体管t2的第一极连接数据信号端data,栅极连接第一栅极驱动信号端g1;驱动晶体管t1的栅极连接开关晶体管t2第二极,第一极连接第一电源信号端vdd,第二极连接发光单元oled一电极;发光单元oled的另一电极连接第二电源端vss;存储电容c连接于驱动晶体管t1的栅极与第二极之间;开关晶体管t3的栅极连接第二栅极驱动信号端g2,第一极连接参考信号端vref,第二极连接驱动晶体管t1的第二极。其中,参考信号端vref可以用于在驱动晶体管t1导通时感测驱动晶体管t1的输出电流,以检测驱动晶体管t1的阈值电压和迁移率。图2为图1所示像素驱动电路的驱动时序图,在数据写入阶段t1:数据信号端data通过开关晶体管t2向驱动晶体管t1的栅极输入数据信号,并存储于存储电容c,同时,参考信号端vref还可以通过开关晶体管t3向驱动晶体管t1的源极输入初始信号。在发光阶段t4:驱动晶体管t1在存储电容c作用下导通,以通过电源信号端vdd驱动发光单元oled发光。需要说明的是,本公开各实施例中采用的晶体管均可以为薄膜晶体管或场效应管或其他特性相同的器件。在本技术中,第一极可以为漏电极、第二极可以为源电极,或者第一极可以为源电极、第二极可以为漏电极。

40.如图2所示,在data写入关断瞬间,g1电压由vgh瞬间转为vgl,通过cgs_s等电容耦合方式拉低g点电压,造成vg≠v

data

,数据信号损失量如公式(1)所示,

[0041][0042]

式中:

△

vp_s为第二节点s在数据写入阶段后的数据信号损失量,cgs_s为像素驱动电路中第二晶体管的栅源极间的等效电容,cgd_d为像素驱动电路中驱动晶体管的栅漏极间的等效电容,cgs_d为像素驱动电路中第二晶体管的栅漏极间的等效电容,cst为像素驱动电路中存储电容的电容值。

[0043]

在发光阶段,ioled流向oled进行发光,而voled逐渐抬升。由于电容自举作用,g点电压也会随之抬升,维持vgs稳定,但由于寄生耦合的作用,g点电压抬升与s点电压抬升的不同,并具有如下关系:

[0044][0045]

式中:

△

v_g为第一节点g在发光阶段的数据信号损失量,cgs_s为像素驱动电路中第二晶体管的栅源极间的等效电容,cgs_d为像素驱动电路中驱动晶体管的栅源极间的等效电容,cgd_d为像素驱动电路中驱动晶体管的栅漏极间的等效电容,cst为像素驱动电路中存储电容的电容值,

△

v_s为第二节点在发光阶段的数据信号损失量。

[0046]

由公式(1)、(2)可知,两方面因素对vgs的影响均与cst相关,cst越大,数据信号损失量越小。相关技术中,以像素驱动电流最大的子像素来确定cst数值,其他子像素保持相

同的cst数值,即各子像素都是预留最大的cst设计,以达到损失量最小的目的,但cst增大不利于像素空间利用。

[0047]

本公开提供一种显示面,以解决上述问题。该显示面板可以包括沿第一方向x和第二方向y阵列分布的像素单元,每个像素单元包括多个像素驱动电路,同一像素单元中的多个像素驱动电路沿第一方向x间隔分布,第一方向x和第二方向y相交,像素驱动电路包括存储电容c和驱动晶体管t1,存储电容c的第一电极连接驱动晶体管t1的栅极,存储电容c的第二电极连接驱动晶体管t1的第一极,该像素驱动电路可以如图1所示。图3为根据本公开一种实施方式的显示面板的结构版图,图4为图3中第一导电层的结构版图,图5为图3中有源层的结构版图,图6为图3中第一导电层和有源层的结构版图,如图4-图6所示,该显示面板可以包括:衬底基板、有源层20和第一导电层10,有源层20位于衬底基板的一侧,有源层20包括多个有源部,有源部用于形成子像素中存储电容c的第一电极;第一导电层10位于衬底基板和有源层20之间,第一导电层10包括多个导电部,导电部用于形成子像素中存储电容c的第二电极,任意导电部在衬底基板的正投影与同一子像素中的有源部在衬底基板的正投影部分交叠,且与相邻子像素中的有源部在衬底基板的正投影分离;其中,同一像素单元中,任意两个子像素具有的交叠面积大小不同,且交叠面积较大的子像素中驱动晶体管沟道区的宽长比大于交叠面积较小的子像素中驱动晶体管沟道区的宽长比。

[0048]

本公开提供的显示面板,像素单元中各子像素的存储电容c的面积大小不同,各子像素的存储电容c的面积大小在匹配各子像素中驱动晶体管的沟道区的宽长比的同时,能够保证不同子像素间数据信号的损失量相同即可,从而无需按照驱动电流最大的子像素来确定存储电容c的数值,由此可减小各子像素的存储电容c的占用空间,提高了显示面板的空间利用率,从而有利于提高显示面板的分辨率。

[0049]

本示例性实施例中,一个像素单元可以包括r子像素、g子像素、b子像素和w子像素,当然,在其他示例性实施例中,一个像素单元也可以包括r子像素、g子像素、b子像素等,这些都属于本公开的保护范围。以一个像素单元包括四个子像素为例,因为四个子像素的发光效率不同,因而各子像素所需要的驱动电流也不同,相应地,各子像素的驱动晶体管的沟道区的宽长比大小不同。r子像素中驱动晶体管的沟道区可具有第一宽长比,g子像素中驱动晶体管的沟道区可具有第二宽长比,b子像素中驱动晶体管的沟道区可具有第三宽长比,w子像素中驱动晶体管的沟道区可具有第四宽长比,本示例性实施例中,第一宽长比、第二宽长比、第三宽长比和第四宽长比可依次减小。在本公开的一些具体实施方式中,第一宽长比可大于第三宽长比与第四宽长比之和,并且且第二宽长比小于第三宽长比与第四宽长比之和。

[0050]

本示例性实施例中,一个像素单元可以包括为r子像素提供第一驱动电流的第一像素驱动电路、为g子像素提供第二驱动电流的第二像素驱动电路、为b子像素提供第三驱动电流的第三像素驱动电路以及为w子像素提供第四驱动电流的第四像素驱动电路。在此基础上,有源部可以包括第一有源部、第二有源部、第三有源部和第四有源部,第一有源部用于形成r子像素中存储电容的第一电极,第二有源部用于形成g子像素中存储电容的第一电极,第三有源部用于形成b子像素中存储电容的第一电极,第四有源部分别用于形成w子像素中存储电容的第一电极;导电部包括第一导电部、第二导电部、第三导电部、第四导电部,第一导电部用于形成r子像素中存储电容的第二电极,第二导电部用于形成g子像素中

存储电容的第二电极,第三导电部用于形成b子像素中存储电容的第二电极,第四导电部用于形成w子像素中存储电容的第二电极;其中,第一导电部在衬底基板的正投影与第一有源部在衬底基板的正投影具有第一交叠面积s1,第二导电部在衬底基板的正投影与第二有源部在衬底基板的正投影具有第二交叠面积s2,第三导电部在衬底基板的正投影与第三有源部在衬底基板的正投影具有第三交叠面积s3,第四导电部在衬底基板的正投影与第四有源部在衬底基板的正投影具有第四交叠面积s4。本示例性实施例中,各子像素的存储电容的大小正比于该子像素中驱动晶体管的沟道区的宽长比。如上所述,第一宽长比、第二宽长比、第三宽长比和第四宽长比依次减小,相应地,第一交叠面积s1、第二交叠面积s2、第三交叠面积s3、第四交叠面积s4依次减小,从而第一像素驱动电路中的存储电容值、第二像素驱动电路中的存储电容值、第三像素驱动电路中的存储电容值和第四像素驱动电路中的存储电容值依次减小。在本公开的一些具体实施方式中,第一交叠面积s1与第四交叠面积s4之比可介于1.5~2.5之间,例如可以为1.5,1.9,2.0,2.3,2.5等。并且第一交叠面积s1小于第三交叠面积s3和第四交叠面积s4之和。此外,为了弥补因为存储电容c尺寸变化所导致的数据信号损失量差异,本示例性实施例中,在满足第一交叠面积s1、第二交叠面积s2、第三交叠面积s3、第四交叠面积s4依次减小的前提下,可依据各子像素的数据信号损失量相同的原则来具体确定第一交叠面积s1、第二交叠面积s2、第三交叠面积s3和第四交叠面积s4的具体大小,使得各子像素实现one gamma匹配。具体而言,可依据公式(1)、(2)计算各子像素的δv_g和δvp_s,确保不同子像素的δv_g和δvp_s数值相同。

[0051]

如图3所示,本示例性实施例中,同一像素单元中,第一像素驱动电路、第四像素驱动电路、第三像素驱动电路和第二像素驱动电路可以沿第一方向x依次排列。第一有源部21、第一导电部11对应形成第一像素驱动电路中存储电容c的第一电极、第二电极,第二有源部22、第二导电部12对应形成第二像素驱动电路中存储电容c的第一电极、第二电极,第三有源部23、第三导电部13对应形成第三像素驱动电路中存储电容c的第一电极、第二电极,第四有源部24、第四导电部14对应形成第四像素驱动电路中的存储电容c的第一电极和第二电极。相应地,同一像素单元中,第一导电部11在衬底基板的正投影、第四导电部14在衬底基板的正投影、第三导电部13在衬底基板的正投影、第二导电部12在衬底基板的正投影可沿第二方向y延伸且在第一方向x依次间隔排列,第一有源部21在衬底基板的正投影、第四有源部24在衬底基板的正投影、第三有源部23在衬底基板的正投影和第二有源部22在衬底基板的正投影可以沿第二方向y延伸且在第一方向x依次间隔排列。其中的第一方向x可以为行方向,第二方向y可以为列方向。

[0052]

应该理解的是,本示例性实施例中所述的某一结构在衬底基板上的正投影沿某一方向延伸,可以理解为,该结构在衬底基板上的正投影整体沿该方向延伸,即该结构在衬底基板上的正投影可以沿该方向直线延伸或弯折延伸。

[0053]

本示例性实施例中,显示面板还可以包括第二导电层30和第三导电层40,其中,衬底基板、第一导电层10、有源层20、第二导电层30、第三导电层40依次层叠设置,上述功能层之间可以设置有绝缘层。如图7-11所示,图7为图3中第二导电层的结构版图,图8为图3中第三导电层的结构版图,图9为图3中有源层和第二导电层的结构版图,图10为图3中有源层和第三导电层的结构版图。

[0054]

如图3、4所示,本示例性实施例中,第一导电层10还可以包括多个第十三导电部

113和多个第十七导电部117,其中,第十三导电部113一方面通过过孔h9连接位于第三导电层40的第一电源线vdd,另一方面通过过孔h9连接位于第三导电层40的各第十五导电部415,各第十五导电部415连接对应像素驱动电路中形成驱动晶体管t1沟道区的有源部(包括第六有源部26、第七有源部27、第八有源部28),从而通过第十三导电部113将第二像素驱动电路的驱动晶体管t1的第一极、第三像素驱动电路的驱动晶体管t1的第一极、第四像素驱动电路的驱动晶体管t1的第一极连接至第一电源线vdd。如图4所示,第十七导电部117在衬底基板的正投影可以沿第一方向x延伸,一个像素单元中可以包括两个第十七导电部117,两个第十七导电部117在第一方向x间隔设置,其中的一个第十七导电部117用于连接形成第一像素驱动电路中第三晶体管t3沟道区的有源部和形成第四像素驱动电路中第三晶体管t3沟道区的有源部,另一个第十七导电部117则用于连接形成第三像素驱动电路中第三晶体管t3沟道区的有源部和形成第二像素驱动电路中第三晶体管t3沟道区的有源部,两个第十七导电部117再通过过孔h1连接位于第三导电层40的第十八导电部418,第十八导电部418连接与其同层的参考信号线vref,从而通过第十七导电部117将各像素驱动电路中第三晶体管t3的第二极连接至参考信号线vref。本示例性实施例中,第一导电层10一方面可以形成部分导电结构,另一方面还可以起到遮光作用,可遮挡衬底基板一侧的入射光照射至有源层20,从而可避免光线对晶体管的沟道区造成不良影响。

[0055]

如图3、5所示,本示例性实施例中,有源层20还可以包括第五有源部25、第六有源部26、第七有源部27、第八有源部28,其中,第五有源部25包括第一子有源部251、第二子有源部252和第三子有源部253,第二子有源部252用于形成第一驱动晶体管t1的沟道区,第一子有源部251、第三子有源部253沿第二方向y连接于第二子有源部252的两端,第五有源部25在衬底基板的正投影与第一导电层中的第一导电部11在衬底基板的正投影部分交叠,第一子有源部251可通过过孔h5电连接位于第三导电层40的第五导电部45,以实现第一像素驱动电路中驱动晶体管t1的第一极连接存储电容c的第二电极,第三子有源部253可通过过孔h7连接位于第三导电层40的第十四导电部414,用于实现第一像素驱动电路中驱动晶体管t1的第二极连接第一电源线vdd。第六有源部26包括第四子有源部261、第五子有源部262、第六子有源部263,第五子有源部262用于形成第二驱动晶体管t1的沟道区,第四子有源部261、第六子有源部263沿第二方向y连接于第五子有源部262的两端,第六有源部26在衬底基板的正投影与第一导电层中的第二导电部12在衬底基板的正投影部分交叠,第四子有源部261可通过过孔h5电连接位于第三导电层40的第六导电部46,以实现第二像素驱动电路中驱动晶体管t1的第一极连接存储电容c的第二电极,第六子有源部263可通过过孔h7连接位于第三导电层40的第十五导电部415,用于实现第二像素驱动电路中驱动晶体管t1的第二极连接第一电源线vdd。第七有源部27包括第七子有源部271、第八子有源部272、第九子有源部273,第八子有源部272用于形成第三驱动晶体管t1的沟道区,第七子有源部271、第九子有源部273沿第二方向y连接于第八子有源部272的两端,第七有源部27在衬底基板的正投影与第一导电层中的第三导电部13在衬底基板的正投影部分交叠,第七子有源部271可通过过孔h5连接位于第三导电层40的第七导电部47,以实现第三像素驱动电路中驱动晶体管t1的第一极连接存储电容c的第二电极,第九子有源部273可通过过孔h7连接位于第三导电层40的第十五导电部415,用于实现第三像素驱动电路中驱动晶体管t1的第二极连接第一电源线vdd。第八有源部28包括第十子有源部281、第十一子有源部282、第十二

子有源部283,第十一子有源部282用于形成第四驱动晶体管t1的沟道区,第十子有源部281、第十二子有源部283沿第二方向y连接于第十一子有源部282的两端,第八有源部28在衬底基板的正投影与第一导电层中的第四导电部14在衬底基板的正投影部分交叠,第十子有源部281可通过过孔h5电连接位于第三导电层40的第八导电部48,以实现第四像素驱动电路中驱动晶体管t1的第一极连接存储电容c的第二电极,第十二子有源部283可通过过孔h7连接位于第三导电层40的第十五导电部415,用于实现第四像素驱动电路中驱动晶体管t1的第二极连接第一电源线vdd。

[0056]

如图5所示,本示例性实施例中,有源层20还可以包括第九有源部29、第十有源部210、第十一有源部211、第十二有源部212、第十三有源部213、第十四有源部214、第十五有源部215、第十六有源部216,其中,第九有源部29设置于第一像素驱动电路中,第九有源部29用于形成第一像素驱动电路中第二晶体管t2的沟道区,第十三有源部213连接于第九有源部29与第一有源部21之间,第九有源部29远离第十三有源部213的一侧连接另一导电部291,该导电部291可通过过孔h8连接位于第三导电层40的数据信号线vdata,从而实现第一像素驱动电路中第二晶体管t2的第二极连接至存储电容c的第一电极、第一极连接数据信号线vdata。第十有源部210设置于第二像素驱动电路中,第十有源部210用于形成第二像素驱动电路中第二晶体管t2的沟道区,第十四有源部214连接于第十有源部210与第二有源部22之间,第十有源部210远离第十四有源部214的一侧连接有另一导电部219,该导电部219可通过过孔h8连接位于第三导电层40的数据信号线vdata,从而实现第二像素驱动电路中第二晶体管t2的第二极连接存储电容c的第一电极,第一极连接数据信号线vdata。第十一有源部211设置于第三像素驱动电路中,第十一有源部211用于形成第三像素驱动电路中第二晶体管t2的沟道区,第十五有源部215连接于第十一有源部211与第三有源部23之间,第十一有源部211远离第十五有源部215的一侧连接有另一导电部218,该导电部218可通过过孔h8连接位于第三导电层40的数据信号线vdata,从而实现第三像素驱动电路中第二晶体管t2的第二极连接存储电容c的第一电极,第一极连接数据信号线vdata。第十二有源部212设置于第四像素驱动电路中,第十二有源部212用于形成第四像素驱动电路中第二晶体管t2的沟道区,第十六有源部216连接于第十二有源部212与第四有源部24之间,第十二有源部212远离第十六有源部216的一侧连接有另一导电部217,该导电部217可通过过孔h8连接位于第三导电层40的数据信号线vdata,从而实现第四像素驱动电路中第二晶体管t2的第二极连接存储电容c的第一电极,第一极连接数据信号线vdata。如图9所示,本示例性实施例中,第十三有源部213中的部分结构被第二导电层中的第九导电部39遮挡形成半导体结构,第十三有源部213中未被遮挡的导电结构连接第九有源部29和第一有源部21。第十四有源部214、第十五有源部215、第十六有源部216具有类似结构,此处不再展开。

[0057]

如图5所示,本示例性实施例中,有源层20还可以包括第十七有源部217,其中,第十七有源部217在衬底基板的正投影可以沿第二方向y延伸,第十七有源部217可以包括第十三子有源部233、第十四子有源部232和第十五子有源部231,第十四子有源部232用于形成第三晶体管t3的沟道区,第十三子有源部233、第十五子有源部231连接于第十四子有源部232的两端,同一像素单元中,多个第十三子有源部233还通过过孔h2对应连接第一导电部11、第二导电部12、第三导电部13和第四导电部14,以实现像素单元中各像素驱动电路中第三晶体管t3的第一极连接存储电容c的第二电极。第十五子有源部231用于与位于第一导

电层10的第十七导电部117连接,从而实现各像素驱动电路中第三晶体管t3的第二极连接参考信号线vref。

[0058]

本示例性实施例中,显示面板可以以第二导电层30为掩膜对有源层20进行导体化处理,即被第二导电层30覆盖的区域形成晶体管的沟道区,未被第二导电层30覆盖的区域形成导体结构。

[0059]

本示例性实施例中,有源层20可以由多晶硅半导体材料形成,相应的,本公开显示面板中的晶体管可以为p型低温多晶硅薄膜晶体管。

[0060]

如图3、5、6所示,本示例性实施例中,第一导电部11的面积可大于第一有源部21的面积,从而可由第一有源部21的面积确定第一像素驱动电路中的存储电容c大小,其他的像素驱动电路可具有类似结构。本示例性实施例中,某一导电部的面积大于某一有源部的面积可以理解为,该有源部在衬底基板的正投影的边缘位于该导电部在衬底基板的正投影内。

[0061]

本示例性实施例中,可在确定各像素驱动电路中驱动晶体管t1的沟道区的宽长比后,通过调节第一有源部21、第二有源部22、第三有源部23和第四有源部24的面积来调节对应像素驱动电路的存储电容c大小,以弥补各像素驱动电路中因为寄生电容不同所导致的数据信号损失量差异。示例性的,表1为本公开一种实施方式提供的各子像素的存储电容值,其中,w/l表示驱动晶体管t1沟道区的宽长比,r子像素所需要的驱动电流最大,对应驱动晶体管t1的w/l值最大,相应地,r子像素的存储电容值最大;w子像素所需要的驱动电流最小,对应驱动晶体管t1的w/l值最小,相应地,w子像素的存储电容值最小,图11为根据表1所示尺寸对各子像素v

gs

的仿真结果,图中的纵坐标表示电压值,横坐标表示沟道长度,可以看出,r子像素、g子像素、b子像素和w子像素对应的像素驱动电路中g点和s点的压差v

gs

相同,均为4.3v,可见本公开提供的显示面板能够在占用较小空间的情况下保持各子像素的数据信号损失量相同,不会影响显示性能。

[0062]

表1

[0063] dr-rdr-gdr-bgr-ww/l(um)16/2212/228/226/22cst(pf)0.30.2450.1950.155

[0064]

如图3、7所示,本示例性实施例中,第二导电层30可以包括多个第九导电部39、多个第十导电部310、多个第十一导电部311、多个第十二导电部312,第九导电部39、第十导电部310、第十一导电部311、第十二导电部312一一对应地设置于第一像素驱动电路中、第二像素驱动电路中、第三像素驱动电路中和第四像素驱动电路中,其中,第九导电部39在衬底基板的正投影覆盖第二子有源部252在衬底基板的正投影,第九导电部39的部分结构用于形成第一驱动晶体管t1的栅极,第九导电部39还通过过孔h6电连接有源层20中的第十三有源部213形成第一像素驱动电路的g点;第十导电部310在衬底基板的正投影覆盖第五子有源部262在衬底基板的正投影,第十导电部310的部分结构用于形成与第二驱动晶体管t1的栅极,第十导电部310还通过过孔h6电连接有源层20中的第十四有源部214形成第二像素驱动电路的g点;第十一导电部311在衬底基板的正投影覆盖第八子有源部272在衬底基板的正投影,第十一导电部311的部分结构用于形成第三驱动晶体管t1的栅极,第十一导电部311还通过过孔h6电连接有源层20中的第十五有源部215形成第三像素驱动电路的g点;第

十二导电部312在衬底基板的正投影覆盖第十一子有源部282在衬底基板的正投影,第十二导电部312的部分结构用于形成第四驱动晶体管t1的栅极,第十二导电部312还通过过孔h6电连接有源层20中的第十六有源部216形成第四像素驱动电路的g点。如图7所示,第二导电层30还可以包括第一栅极驱动信号线g1和第二栅极驱动信号线g2,其中,第一栅极驱动信号线g1可以用于提供图1中的第一栅极驱动信号端,第二栅极驱动信号线g2可以用于提供图1中的第二栅极驱动信号端。第一栅极驱动信号线g1在衬底基板的正投影可以沿第一方向x延伸且部分覆盖第九有源部29在衬底基板的正投影、部分覆盖第十有源部210在衬底基板的正投影、部分覆盖第十一有源部211在衬底基板的正投影、部分覆盖第十二有源部212在衬底基板的正投影,第一栅极驱动信号线g1的部分结构用于形成各像素驱动电路中第二晶体管t2的栅极。此外,如图7所示,本示例性实施例中,一个像素单元中第一栅极驱动信号线g1可以包括子栅线301和子栅线302,两个子栅线可平行设置,子栅线301和子栅线302可通过沿第二方向y延伸的导电结构进行连接,这样设置的好处在于,当显示面板的某一子栅线损坏时,还可通过与之平行的另一个子栅线传输信号,从而保证显示面板还可以继续使用,由此可提高产品的良率。如图7所示,本示例性实施例中,第二栅极驱动信号线g2在衬底基板的正投影可以沿第一方向x延伸,第二栅极驱动信号线g2在衬底基板的正投影部分覆盖第十四子有源部232在衬底基板的正投影,第二栅极驱动信号线g2的部分结构形成第三晶体管t3的栅极。如图7所示,本示例性实施例中,第二导电层30还可以包括多个第十六导电部316和多个第十九导电部319,其中,多个第十六导电部316在衬底基板的正投影可以沿第二方向y延伸且沿第一方向x间隔分布,同一像素单元中,第十六导电部316在衬底基板的正投影可以位于第一导电部11在衬底基板的正投影远离第四导电部14在衬底基板的正投影的一侧,第十六导电部316在衬底基板的正投影与第一电源线vdd在衬底基板的正投影部分交叠,在一些实施例中,第十六导电部316在衬底基板的正投影可以位于第一电源线vdd在衬底基板的正投影内,且第十六导电部316通过过孔h3连接第一电源线vdd,由此可降低第一电源线vdd的线阻,从而有利于降低第一电源线vdd的压降损耗,提高发光单元的发光稳定性。第十九导电部319在衬底基板的正投影可以沿第二方向y延伸,同一像素单元中,第十九导电部319在衬底基板的正投影可以位于第三导电部13在衬底基板的正投影和第四导电部14在衬底基板的正投影之间,第十九导电部319在衬底基板的正投影与参考信号线vref在衬底基板的正投影部分交叠,例如第十九导电部319在衬底基板的正投影可以位于参考信号线vref在衬底基板的正投影内,第十九导电部319通过过孔h4连接参考信号线vref,同样地,第十九导电部319可以降低参考信号线vref的线阻,从而降低参考信号线vref的压降损耗。

[0065]

本示例性实施例中所述的某一结构a在衬底基板的正投影覆盖另一结构b在衬底基板的正投影可以理解为,b在衬底基板平面的投影的轮廓完全位于a在同一平面内投影的轮廓的内部。

[0066]

如图3、8所示,本示例性实施例中,第三导电层40可以包括第一电源线vdd、参考信号线vref和数据信号线vdata,第一电源线vdd在衬底基板的正投影、参考信号线vref在衬底基板的正投影、数据信号线vdata在衬底基板的正投影均可以沿第二方向y延伸,第一电源线vdd可以用于提供图1中的第一电源信号端vdd,参考信号线vref可以用于提供图1中的参考信号端vref,数据信号线vdata可以用于提供图1中的数据信号端data。如图8所示,本

示例性实施例中,同一像素单元中,第一电源线vdd在衬底基板的正投影位于第一导电部11在衬底基板的正投影远离第四导电部14在衬底基板的正投影的一侧,第一电源线vdd连接同层的第十四导电部414,第十四导电部414通过过孔h7连接第五有源部25,从而实现第一电源线vdd与第一像素驱动电路中驱动晶体管t1的第二极连接。如图8,第三导电层40还可以包括第十五导电部415,第十五导电部415在衬底基板的正投影可以沿第二方向y延伸,同一像素单元中,第六子有源部263在衬底基板的正投影、第九子有源部273在衬底基板的正投影、第十二子有源部283在衬底基板的正投影分别与对应第十五导电部415在衬底基板的正投影部分交叠,且在交叠区域通过过孔h7电连接,同时,第十五导电部415还通过过孔h9连接位于第一导电层10中的第十三导电部113,从而实现将第二像素驱动电路、第三像素驱动电路和第四像素驱动电路中的驱动晶体管t1的第二极连接至第一电源线vdd。如图8所示,本示例性实施例中,同一像素单元中,参考信号线vref在衬底基板的正投影位于第三导电部13在衬底基板的正投影和第四导电部14在衬底基板的正投影之间,第三导电层40还可以包括第十八导电部418,第十八导电部418在衬底基板的正投影可以沿第一方向x延伸,并且第十八导电部418在衬底基板的正投影位于第二栅极驱动信号线g2在衬底基板的正投影远离第一栅极驱动信号线g1在衬底基板的正投影的一侧,第十八导电部418与参考信号线vref同层设置且相交以实现第十八导电部418与参考信号线vref的电连接。如上所述,位于第一导电层10的第十七导电部117在衬底基板的正投影可以沿第一方向x延伸且通过过孔h1连接有源层20的第十七有源部217,第十七导电部117在衬底基板的正投影与第十八导电部418在衬底基板的正投影部分交叠,第十七导电部117通过过孔h1连接第三导电层40的第十八导电部418,从而将形成第三晶体管t3的沟道区的第十七有源部217连接至参考信号线vref,实现各像素驱动电路中第三晶体管t3的第二极连接参考信号线vref。

[0067]

如图8所示,数据信号线vdata在衬底基板的正投影可以沿第二方向y延伸,一个像素单元中包括有四个数据信号线vdata,四个数据信号线vdata与四个像素驱动电路中第二晶体管t2的第一极对应连接。数据信号线vdata两两相邻,两个数据信号线vdata在衬底基板的正投影位于第一有源部21在衬底基板的正投影和第四有源部24在衬底基板的正投影之间,用于分别通过过孔h8连接第九有源部29、第十二有源部212,实现第一像素驱动电路中第二晶体管t2的第一极和第四像素驱动电路中第二晶体管t2的第一极连接数据信号线vdata,另外两个数据信号线vdata在衬底基板的正投影位于第三有源部23在衬底基板的正投影和第二有源部22在衬底基板的正投影之间,用于分别通过过孔h8连接第十有源部210、第十一有源部211,实现第二像素驱动电路中第二晶体管t2的第一极和第三像素驱动电路中第二晶体管t2的第一极连接至参考信号线vref。

[0068]

图12为根据本公开一种实施方式的存储电容的剖视图,如图12所示,本示例性实施例中,有源层20中的部分导电结构形成存储电容c的一个电极,有源层20与第一导电层10之间、有源层20与第三导电层40之间具有绝缘层,第一导电层10和第三导电层40电连接,从而第一导电层10和第三导电层40分别在有源层20的两侧形成存储电容c的另一电极,形成双层存储电容结构,该结构可在不增加尺寸的情况下提高存储电容c的容值。具体而言,如图8、10所示,本示例性实施例中,第三导电层40还可以包括多个第五导电部45、多个第六导电部46、多个第七导电部47和多个第八导电部48,其中,第五导电部45在衬底基板的正投影与第一有源部21在衬底基板的正投影部分交叠且具有第五交叠面积s5,第五导电部45可在

第一像素驱动电路中对应第十三子有源部233的位置通过过孔h2电连接第一导电部11形成第一像素驱动电路中的s点;第六导电部46在衬底基板的正投影与第二有源部22在衬底基板的正投影部分交叠且具有第六交叠面积s6,第六导电部46可在对应该像素驱动电路的第十三子有源部233的位置通过过孔h2电连接第二导电部12形成第二像素驱动电路的s点;第七导电部47在衬底基板的正投影与第三有源部23在衬底基板的正投影部分交叠且具有第七交叠面积s7,第七导电部47可在第三像素驱动电路中对应于第十三子有源部233的位置通过过孔h2电连接第三导电部13形成第三像素驱动电路的s点;第八导电部48在衬底基板的正投影与第四有源部24在衬底基板的正投影部分交叠且具有第八交叠面积s8,第八导电部48可在第四像素驱动电路中对应第十三子有源部233的位置通过过孔h2电连接第四导电部14形成第四像素驱动电路的s点。如图10所示,本示例性实施例中,第五交叠面积s5、第六交叠面积s6、第七交叠面积s7、第八交叠面积s8依次减小。在本公开的一些实施方式中,第五交叠面积s5可与第一交叠面积s1相同、第六交叠面积s6可与第二交叠面积s2相同、第七交叠面积s7可与第三交叠面积s3相同、第八交叠面积s8可与第四交叠面积s4相同。示例性的,以第一像素驱动电路为例,第一导电部11和第五导电部45的面积可以设置为大于第一有源部21的面积,使得第一交叠面积s1与第五交叠面积s5相同。当然,在本公开的其他示例性实施例中,各像素驱动电路中第一导电层10中的导电部与对应有源部的交叠面积也可以与第三导电层40中的导电部与对应有源部的交叠面积不同。

[0069]

图13为图3中沿aa方向的剖视图,该显示面板还可以包括缓冲层2、第一绝缘层3、第二绝缘层4、第一介电层5,其中,衬底基板1、缓冲层2、第一导电层10、第一绝缘层3、有源层20、第二绝缘层4、第二导电层30、第一介电层5、第三导电层40依次层叠设置。第一导电层10、第二导电层30、第三导电层40可以采用金属材料,如银(ag)、铜(cu)、铝(al)和钼(mo)中的任意一种或多种,或上述金属的合金材料,如铝钕合金(alnd)或钼铌合金(monb),可以是单层结构,或者多层复合结构,如mo/cu/mo等。缓冲层2的材料可以为氧化硅、氮化硅等。第一绝缘层3、第二绝缘层4、第一介电层5可以采用硅氧化物(siox)、硅氮化物(sinx)和氮氧化硅(sion)中的任意一种或多种,可以是单层、多层或复合层。衬底基板1可以包括依次层叠设置的玻璃基板、阻挡层、聚酰亚胺层等,阻挡层可以为无机材料。

[0070]

此外,本公开还提供一种显示面板存储电容确定方法,该方法可包括如下步骤:

[0071]

s110、依据像素单元中各子像素的目标驱动电流确定对应子像素中驱动晶体管沟道区的宽长比;

[0072]

s120、依据各子像素中驱动晶体管沟道区的宽长比调节各子像素的存储电容值,以使得各子像素在发光阶段的数据信号损失量相同;

[0073]

s130、依据各子像素的存储电容值,确定像素单元中的第一交叠面积、第二交叠面积、第三交叠面积和第四交叠面积。

[0074]

步骤s110主要使得各子像素的像素驱动电路的驱动晶体管的沟道区的宽长比与该子像素的目标驱动电流相匹配。

[0075]

因为驱动晶体管的沟道区的宽长比变化后,会相应引起寄生电容发生改变,步骤s120是要依据各子像素的驱动晶体管沟道区的宽长比来调节对应子像素的存储电容值,本示例性实施例具体基于如下公式(1)和(2)来调节存储电容值,以使得各子像素间在数据写入阶段后的数据信号损失量分别相同,以及各子像素在发光阶段的数据信号损失量分别相

同:

[0076][0077][0078]

式中:

△

vp_s为第二节点s在数据写入阶段后的数据信号损失量,

△

v_g为第一节点g在发光阶段的数据信号损失量,cgs_s为像素驱动电路中第二晶体管的栅源极间的等效电容,cgs_d为像素驱动电路中驱动晶体管的栅源极间的等效电容,cgd_d为像素驱动电路中驱动晶体管的栅漏极间的等效电容,cst为像素驱动电路中存储电容的电容值,

△

v_s为第二节点在发光阶段的数据信号损失量。

[0079]

通过上述公式(1)和公式(2)计算出子像素的像素驱动电路的存储电容值,进而在版图中确定各子像素的交叠面积。

[0080]

此外,本公开还提供一种显示装置,包括本公开任意实施例的显示面板。

[0081]

本领域技术人员在考虑说明书及实践这里公开的发明后,将容易想到本公开的其他实施例。本技术旨在涵盖本公开的任何变型、用途或者适应性变化,这些变型、用途或者适应性变化遵循本公开的一般性远离并包括本公开未公开的本技术领域中的公知常识或惯用技术手段。说明书和实施例仅被视为示例性的,本公开的真正范围和精神由权利要求指出。