基于risc v自定义指令集拓展的音频降噪加速器系统、方法

技术领域

1.本发明属于集成电路技术领域,具体涉及到一种基于risc v自定义指令集拓展的音频降噪加速器系统及方法。

背景技术:

2.随着经济的发展和技术的不断进步,音频降噪系统的应用场景越来越多,例如车内降噪、燃气站内降噪、耳机降噪等。但是目前往往采取的还是物理隔绝噪声源等被动降噪的方式,采用主动降噪让声源信号叠加相消的方式往往具备硬件实现困难,改进的优良算法很难用fpga进行硬件实现,因此采用软件实现方式将会使得改进的算法能够实现,这将会是解决音频降噪算法实现困难的一种重要手段。

3.同时,risc v作为一种新兴的指令集架构,具备了开源和后发优势。针对嵌入式领域而言,采用这种指令集架构的软核能够自定义指令,针对算法中的乘积累加结构和卷积结构,能定制出专用的加速单元电路,实现音频降噪专用设计领域。随着国内对于risc v指令集架构的热烈推崇,这样的专用领域soc芯片设计将能得到更大的发展。

4.然后,随着国内aiot的兴起,针对处理器核的运行速度等问题,出现了很多不同类型的加速器,常见的如针对图像的神经网络加速器,其中又有很多的类型,但是传统的硬件fxlms算法实现并没有合适的加速器对其进行特定运算加速,乘法器和加法器随着算法的复杂度上去之后使硬件实现fxlms算法更具备挑战性,因此采用fpga+mcu架构的软硬件协同,用软件进行算法实现,硬件针对特定运算进行加速,将在音频降噪系统中展现新的方向和可能。

5.传统的降噪方式如提取多个噪声音频信号的幅度值角度值然后利用神经网络进行训练确定出一个纯净音频信号的复数谱,然后将得到的复数谱进行逆变换,最后根据这个逆变换去进行音频降噪。这样的方式往往不具备灵活性,针对不同的噪声源就需要进行重新训练,同时这样的方式也不具备采用软硬件协同处理的灵活性,因此本发明基于risc v自定义指令集拓展的音频降噪加速器系统将为音频降噪提供一种新的方法。

技术实现要素:

6.本发明旨在解决以上现有技术的问题。提出了一种基于risc v自定义指令集拓展的音频降噪加速器系统及方法,本发明能够实现算法的灵活可更改性,传输的稳定性,运算快速性、专用性强的音频降噪系统,本系统能够广泛用于汽车降噪、耳机降噪、高铁飞机降噪等声源降噪领域,本发明的技术方案如下:

7.一种基于risc v自定义指令集拓展的音频降噪加速器系统,其包括:e203_core(蜂鸟e203开源处理器内核)、nice_core(自定义协处理器)、nice_interface(主处理器与协处理器之间的接口电路)、e203_soc(以e203为内核搭建的片上系统)、音频编解码wm8731模块、音频降噪fxlms算法,其中,

8.所述e203_core通过nice_interface与nice_core相连接,e203_core、nice_core

与相关外设端口一同组成e203_soc,e203_soc与音频编解码wm8731模块相连接,音频降噪fxlms算法通过软件编程下载到risc v处理器核内运行;通过片外flash存储器保存可执行文件,系统启动之后,首先e203_core进行初始化,然后根据指令顺序执行访问外设总线上的iic接口电路,根据指令首先通过iic接口电路配置音频编解码模块wm8731,其后,通过参考麦克风采集声音信号和目标噪声叠加之后的声源信号,通过误差麦克风采集到残余噪声,将采集到的声源信号和残余噪声经过wm8731模块的audio_data_rx,通过wm8731模块内置的adc转换模块,将模拟信号转变成数字信号,之后通过wm8731模块内置的数字滤波器模块进行滤波处理,把滤波之后的数字信号通过iis接口电路传输到外设总线上,然后根据指令从外设总线上获取滤波后的数字信号并传输至e203_core内按照fxlms算法的软件实现流程进行处理,其中在处理乘积累加运算和卷积运算的时候,将被e230_core中的译码部分检测出为自定义指令,e203_core则通过nice_interface将自定义指令和源操作数传递给nice_core进行特定运算部分的加速,其中乘积累加运算将会调用mac指令电路,卷积运算则会调用conv指令电路,之后又根据指令执行将处理之后的数字信号传输至外设总线,将经过降噪fxlms算法处理之后的数字信号进行输出,再通过iis外设接口电路传输至wm8731音频编解码模块中进行dac转换,将处理之后的数字信号转变成模拟信号,通过audio_data_tx传输至次级声源得到反相噪声,最后得到的反相噪声与目标噪声干涉相消,从而进行音频的主动降噪,实现音频降噪系统。

9.进一步的,所述e203_soc由e203_core、nice_core、icb_apb、uart串口、iic接口及iis接口组成;其中,e203_core为处理器核用于运行指令并按照顺序执行指令,同时根据指令内容控制相应的模块对数据信息进行处理,在e203_core中的执行单元exu的通用寄存器reg则将协处理器传回的处理后的数据进行保存,在e203_core中的访存控制单元lsu中的数据紧耦合器dtcm则是提供源寄存器索引对应的数据传递给协处理器,使自定义指令能够进行数据的读写访问,nice_interface用于e203_core与nice_core之间通信传输,nice_core用于对处理器核中传来的数据进行加速处理,通过nice_interface获取到自定义指令,然后通过译码decode寻找到对应的自定义指令,指令即lbuf、sbuf、conv、mac,然后根据相应指令的功能进行数据访问存储或者数据处理并进行写回,其中lbuf指令则是进行数据的加载过程,从lsu中的dtcm中进行数据的获取并将其存储到buf,sbuf指令则是进行数据存储过程,将buf中的数据存储回到lsu中的dtcm中,conv指令则是从buf中获取权值系数和输入信号进行卷积运算,并将得到的运算结果写回至exu中的reg,mac指令则是从buf获取权值系数和误差分量进行乘积累加运算,并将运算结果暂存至buf,待运算结束之后将整个结果写回至exu中的reg,整个过程则是由一个有限状态机fsm进行状态转移的控制,icb_apb则用于处理器核与各个外设接口之间的通信传输,uart串口用于把adcdata和dacdata传输至上位机进行保存,便于用matlab对数据进行分析,iic接口用于处理器核对音频编解码wm8731模块进行寄存器的配置,及iis接口用于处理器核与音频编解码wm8731模块之间的数据传输。

10.进一步的,所述nice_core通过nice_interface将e203_core传递过来的自定义指令、源操作数寄存器地址在内的信号进行译码操作,通过对比其具体格式部分,译码得到相应的自定义指令,然后在状态机的调控下,进行相应自定义指令的执行。

11.进一步的,所述音频编解码模块wm8731的内部设置有一个内置的adc和一个dac以

及一个数字滤波器,通过mic传输采集模式,采集外部的待处理声源,经过其内置adc进行模拟信号到数字信号的转变,然后将得到的数字信号经过内置数字滤波器进行滤波处理,得到输出数据adcdata,然后通过risc v软核处理之后的数据dacdata输入到音频编解码模块中的dac,进行数字信号到模拟信号的转换,将转换之后的模拟信号通过mic进行输出。

12.进一步的,所述音频编解码模块wm8731内部设置iic接口电路,可以进行主从模式的配置、adc、dac使能选择及mic和line模式下音量大小和是否开启数字滤波在内的操作,由于anc音频降噪系统的原理是利用声波的相消干涉,因此这里将配置wm8731模块为从机模式、mic模式、adc、dac使能,寄存器配置信息将由e203_core通过iic接口总线进行寄存器的配置。

13.进一步的,所述音频降噪fxlms算法,编写以c语言为描述语言,内联汇编语言为辅助语言的形式,通过ide软件进行编译汇编链接下载可执行文件到risc v软核中,通过指令的执行以软件方式实现fxlms音频降噪算法。

14.进一步的,在音频降噪fxlms算法的软件实现中,将待处理数字信号降噪处理后得到的数字信号,采用如下公式进行降噪处理:

15.y(n)=y(n)+w(n)(k

‑

2)x(n)

16.e(n)=d(n)

‑

y

s

(n)

17.d(n)=p(n)*x(n)

18.y

s

(n)=s(n)*y(n)

[0019][0020][0021]

其中y(n):次级声源、w(n)(k):权值系数、x(n):声源信号、e(n):误差信号、d(n):残余噪声、y

s

(n):通过次级路径的次级声源、p(n):声源信号到误差麦克风的参考信号、s(n):次级声源到误差麦克风次级路径产生的信号、声源信号的估计值,其中对步长因子的约束具体为:

[0022][0023]

其中μ:fxlms算法的步长;λ

max

:自相关矩阵的特征值的最大值。

[0024]

一种基于所述系统的音频降噪方法,其包括以下步骤:

[0025]

首先通过片外flash存储器保存c语言程序编译汇编链接之后产生的可执行文件,系统启动之后,首先e203_core进行初始化,然后根据指令顺序执行访问外设总线上的iic接口电路,根据指令首先通过iic接口电路配置音频编解码模块wm8731;

[0026]

其次,通过参考麦克风采集声音信号和目标噪声叠加之后的声源信号,通过误差麦克风采集到残余噪声,将采集到的声源信号和残余噪声经过wm8731模块的audio_data_rx,通过wm8731模块内置的adc转换模块,将模拟信号转变成数字信号,之后通过wm8731模块内置的数字滤波器模块进行滤波处理,把滤波之后的数字信号通过iis接口电路传输到外设总线上;

[0027]

接着,根据指令从外设总线上获取滤波后的数字信号并传输至e203_core内按照

fxlms算法的软件实现流程进行处理,其中在处理乘积累加运算和卷积运算的时候,将被e203_core中的译码部分检测出为自定义指令,e203_core则通过nice_interface将自定义指令和源操作数传递给nice_core进行特定运算部分的加速,其中乘积累加运算将会调用mac指令电路,卷积运算则会调用conv指令电路;

[0028]

然后又根据指令执行将处理之后的数字信号传输回外设总线,将经过降噪fxlms算法处理之后的数字信号进行输出,再通过iis外设接口电路传输至wm8731音频编解码模块中进行dac转换,将处理之后的数字信号转变成模拟信号,通过音频数据发送端传输至次级声源得到反相噪声;

[0029]

最后,反相噪声与目标噪声干涉相消,从而进行音频的主动降噪,实现音频降噪系统。

[0030]

进一步的,在协处理器中定义自定义指令集编码格式,一共涉及到4条自定义指令,分别是lbuf指令、sbuf指令、conv指令、mac指令,其中lbuf指令和sbuf指令由于对同一个地址的buf进行操作,所以需要用其opcode字段做区别,分别由custom0、custom1所决定,即7`b0001011和7`b0101011,由于sbuf和lbuf指令只需要从dtcm进行读取和写入操作,并不需要进行数据的写回,因此只需要利用其源操作数1,即rs1,所以funct3字段定义为3`b 010格式,代表只对源操作数寄存器rs1进行操作,由于rd、rs2并未使用,因为可以将此部分定义为读取或者写入的数据的长度选择,funct7字段则是定义为buf中加载存储的起始地址,其中conv指令只需要目标寄存器进行数据的返回即可因此需要对其返回的目标寄存器进行操作,即rd,funct3funct7rs1rs2等部分则组合定义为其处理的数据x[9:0]和权值系数w[9:0],均由伪双口sram进行读取传递给conv电路部分进行运算,mac指令则需要调用目标寄存器和源操作进行其运算,所以其funct3字段定义为3`b111格式,funct7字段则没有定义要求,其中conv和mac指令的opcode定义为四种custom均可,本发明用的是custom3和custom4,即7`b1011011和7`b1111011。

[0031]

进一步的,通过lbuf指令能够加载待处理数据信息,之后将其存储在xbuf、qbuf两个伪双口sram中,wbuf则以初值形式进行定义一个空的伪双口sram。之后通过conv指令对xbuf、wbuf进行数据的读取,该指令是一个采用加法树结构的卷积运算单元电路,其数据长度由滤波器阶数所决定,即滤波器阶数为j时,其待处理信号x[j

‑

1:0]和权值系数w[j

‑

1:0],得到其运算结果后将其保存在ybuf进行fifo存储,其宽度和深度定义为数据宽度和滤波器的阶数长度。之后,通过mac指令进行qbuf与误差系数的乘积后与上一列的权值系数wbuf相加得到新的权值系数wbuf,通过mac自定义指令对其进行写入新的权值系数,进行权值的更新,其中误差系数的乘积部分由初级噪声信号dn与ybuf中存储的数据相减得到后乘上步长因子所得,然后一直重复上述步骤,直到将所有的输出将fifo的深度填满即可。

[0032]

本发明的优点及有益效果如下:

[0033]

1、本发明采用risc v软核soc,具有高度的可配置性,能够根据功能的不同需求进行配置不同的外设接口电路,同时删减掉电路中使用不到的一些接口外设,减少资源的浪费。

[0034]

2、本发明采用risc v指令集架构,能够根据算法中的运算关键步骤,自行定义指令,然后采用内联汇编的格式,进行硬件加速单元的设计,给特定运算关键步骤进行加速。使算法的运算速度更快,同时也能够更好的减少指令数和执行周期数。

[0035]

3、本发明采用硬件iis接口电路,能够稳定传输音频信号,并且可配置的fifo宽度和深度以及时钟单元等,可以满足不同的采样率和采样字节数的选择,其适用范围更加广阔。

[0036]

4、本发明采用四条自定义指令进行运算加速,其中conv指令仅仅使用乘法器和加法器采用加法树结构构成卷积运算单元,可以对算法中多次的卷积运算进行指令电路的复用,同时mac指令也可以给算法中的乘积累加部分进行多次的复用,降低整个协处理器开发所消耗的硬件资源,降低其颗粒度。

[0037]

5、本发明采用软件方式实现fxlms算法,利用雅可比公式求出矩阵的最大特征值,然后求倒数得到步长因子。相比纯硬件实现方式而言,软件实现更具有可行性,没有硬件实现那么困难,同时软件实现具有更好的灵活性,在risc v指令集体系下还可以利用硬件加速单元对其进行部分加速,采用软硬件协同的处理方式,将硬件和软件开发的优势都汇聚到一起。

附图说明

[0038]

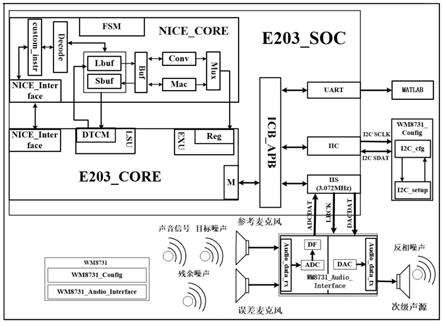

图1是本发明提供优选实施例音频降噪加速器系统架构图;

[0039]

图2为;nice_interface接口电路示意图;

[0040]

图3为;自定义指令集编码示意图;

[0041]

图4为;卷积运算和乘累加运算电路结构图;

[0042]

图5为;fxlms算法的硬件模型结构图;

[0043]

图6为;fxlms算法的c语言实现流程图;

[0044]

图7为;mac自定义指令集vivado联合仿真图。

具体实施方式

[0045]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、详细地描述。所描述的实施例仅仅是本发明的一部分实施例。

[0046]

本发明解决上述技术问题的技术方案是:

[0047]

本发明设计的一种基于risc v自定义指令集拓展的音频降噪加速器系统,如附图1所示,其结构包括:e203_core、nice_core、nice_interface、e203_soc、音频编解码wm8731模块、音频降噪fxlms算法;其中:

[0048]

所述e203_soc由e203_core、nice_core、icb_apb、uart串口、iic接口及iis接口组成;其中,通过片外flash存储器保存c语言程序编译汇编链接之后产生的可执行文件,系统启动之后,首先e203_core进行初始化,然后根据指令顺序执行访问外设总线上的iic接口电路,根据指令首先通过iic接口电路配置音频编解码模块wm8731,其后,通过参考麦克风采集声音信号和目标噪声叠加之后的声源信号,通过误差麦克风采集到残余噪声,将采集到的声源信号和残余噪声经过wm8731模块的audio_data_rx,通过wm8731模块内置的adc转换模块,将模拟信号转变成数字信号,之后通过wm8731模块内置的数字滤波器模块进行滤波处理,把滤波之后的数字信号通过iis接口电路传输到外设总线上,然后根据指令从外设总线上获取滤波后的数字信号并传输至e203_core内按照fxlms算法的软件实现流程进行处理,其中在处理乘积累加运算和卷积运算的时候,由于在c语言中采用内联汇编形式的自

定义指令,将被e203_core中的译码部分检测出为自定义指令,e203_core则通过nice_interface将自定义指令和源操作数传递给nice_core进行特定运算部分的加速,其中乘积累加运算将会调用mac指令电路,卷积运算则会调用conv指令电路,之后又根据指令执行将处理之后的数字信号传输至外设总线,将经过降噪fxlms算法处理之后的数字信号进行输出,再通过iis外设接口电路传输至wm8731音频编解码模块中进行dac转换,将处理之后的数字信号转变成模拟信号,通过audio_data_tx传输至次级声源得到反相噪声,最后得到的反相噪声与目标噪声干涉相消,从而进行音频的主动降噪,实现音频降噪系统。

[0049]

本发明为了使nice_core与e203_core之间具有良好的时序稳定性,采用了如图2所示的接口电路nice_interface,当exu执行模块检测出指令为自定义指令时,通过判断其opcode、funct3部分的编码情况,将指令和源操作数等信息传递给nice_core,nice_core在内部fsm状态机的控制下进行协处理器部分的运算加速,具体为卷积运算和乘积累加运算部分,当其需要访问lsu中的dtcm里的数据时,便给lsu发送地址读写请求和写数据等信息,待lsu返回读取结果,供nice_core进行处理,待其处理完毕之后根据自定义指令编码规则进行判断其是否需要返回目标寄存器,如果需要则将结果返回至exu中的通用寄存器中。

[0050]

本发明采用了risc v国际官方预留的自定义指令集定义,如图3所示,opcode字段、funct3字段、funct7字段决定了自定义指令集的不同,rd、rs1、rs2等分别代表了写回的目标寄存器、源操作数寄存器1、源操作数寄存器2。在本发明中,一共涉及到4条自定义指令,分别是lbuf指令、sbuf指令、conv指令、mac指令,其中lbuf指令和sbuf指令由于对同一个地址的buf进行操作,所以需要用其opcode字段做区别,分别由custom0、custom1所决定,即7`b0001011和7`b0101011,由于sbuf和lbuf指令只需要从dtcm进行读取和写入操作,并不需要进行数据的写回,因此只需要利用其源操作数1,即rs1,所以funct3字段定义为3`b 010格式,代表只对源操作数寄存器rs1进行操作,由于rd、rs2并未使用,因为可以将此部分定义为读取或者写入的数据的长度选择,funct7字段则是定义为buf中加载存储的起始地址,其中conv指令只需要目标寄存器进行数据的返回即可因此需要对其返回的目标寄存器进行操作,即rd,funct3funct7rs1rs2等部分则组合定义为其处理的数据x[9:0]和权值系数w[9:0],均由伪双口sram进行读取传递给conv电路部分进行运算,mac指令则需要调用目标寄存器和源操作数进行其运算,所以其funct3字段定义为3`b111格式,funct7字段则没有定义要求,其中conv和mac指令的opcode定义为四种custom均可,本发明用的是custom3和custom4,即7`b1011011和7`b1111011。

[0051]

本发明中涉及到的自定义指令运算部分如图4所示,通过lbuf指令能够加载待处理数据信息,之后将其存储在xbuf、qbuf两个伪双口sram中,wbuf则以初值形式进行定义一个空的伪双口sram。之后通过conv指令对xbuf、wbuf进行数据的读取,该指令下是一个采用加法树结构的卷积运算单元电路,其数据长度由滤波器阶数所决定,即滤波器阶数为j时,其待处理信号x[j

‑

1:0]和权值系数w[j

‑

1:0],得到其运算结果后将其保存在ybuf进行fifo存储,其宽度和深度定义为数据宽度和滤波器的阶数长度。之后,通过mac指令进行qbuf与误差系数的乘积后与上一列的权值系数wbuf相加得到新的权值系数wbuf,通过mac自定义指令对其进行写入新的权值系数,进行权值的更新,其中误差系数的乘积部分由初级噪声信号dn与ybuf中存储的数据相减得到后乘上步长因子所得,然后一直重复上述步骤,直到将所有的输出fifo的深度填满即可。

[0052]

本发明分析了典型fxlms算法的硬件模型如附图5所示,输入序列经过延迟器之后与权值系数进行乘积之后累加得到输出序列,同时权值系数进入lms之后进行权值系数的更新迭代,多次重复这个步骤将输入序列进行多次更新得到降噪算法处理之后的序列,同时通过fxlms算法的硬件模型,能够提取出如下运算公式:

[0053]

y(n)=y(n)+w(n)(k

‑

2)x(n)

[0054]

e(n)=d(n)

‑

y

s

(n)

[0055]

d(n)=p(n)*x(n)

[0056]

y

s

(n)=s(n)*y(n)

[0057][0058][0059]

之后对公式进行如附图6所示的c语言程序编写,同时针对算法中的特定运算部分加入我们特定的硬件加速单元电路,针对数字滤波器部分加入卷积运算单元,针对权值系数更新的部分加入乘积累加电路进行运算的加速,以此体现出risc v指令集架构的优势。

[0060]

最后如附图7所示,是采用mac自定义指令进行vivado联合仿真之后的结果,从图中可以看到具体的指令格式和加载进去的待处理数据和最后运算得到的数据等信息,可以知道整个系统的硬件加速部分完整。

[0061]

上述实施例阐明的系统、装置、模块或单元,具体可以由计算机芯片或实体实现,或者由具有某种功能的产品来实现。

[0062]

还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

[0063]

以上这些实施例应理解为仅用于说明本发明而不用于限制本发明的保护范围。在阅读了本发明的记载的内容之后,技术人员可以对本发明作各种改动或修改,这些等效变化和修饰同样落入本发明权利要求所限定的范围。