1.本技术涉及显示技术领域,具体涉及一种阵列基板及显示面板。

背景技术:

2.现有液晶面板主要包括阵列基板、彩膜基板和夹在阵列基板和彩膜基板之间的液晶。随着液晶显示器的应用领域不断扩展,对液晶显示器的可靠性要求也不断提高。现在的高温高湿动作(high temperature high humidity operation,hthho)规格条件变更为在温度为60℃、湿度为90%rh测试500小时,所以对面板的要求更高。

3.在对现有技术的研究和实践过程中,本技术的发明人发现,在60℃、90%rh的hthho可靠性测试中,显示面板周边存在不良(mura),具体表现为周边的位置较面板中心位置偏亮,影响到面板的品质。

技术实现要素:

4.本技术实施例提供一种阵列基板及显示面板,可以改善显示面板周边显示不均。

5.本技术实施例提供一种阵列基板,包括:

6.基板,所述基板上设置有多个像素单元;

7.多个阵列电极,至少一所述阵列电极对应设置在一所述像素单元内;其中,自所述基板中心向所述基板边缘的方向排列的所述像素单元中,至少部分所述像素单元对应的所述阵列电极的面积沿排列方向逐渐减小。

8.可选的,在本技术的一些实施例中,所述阵列基板包括第一显示子区与第二显示子区,所述第二显示子区设置在所述第一显示子区的至少一侧;所述第二显示子区中,不同所述像素单元对应的所述阵列电极的面积自所述基板中心向所述第二显示子区边缘逐渐减小。

9.可选的,在本技术的一些实施例中,所述第二显示子区至少设置在所述第一显示子区的第一侧和第二侧,所述第一侧与所述第二侧相交;设置在所述第一侧的所述第二显示子区中,不同所述像素单元对应的所述阵列电极的面积沿所述基板中心向所述第一侧的方向逐渐减小,设置在所述第二侧的所述第二显示子区中,不同所述像素单元对应的所述阵列电极的面积沿所述基板中心向所述第二侧的方向逐渐减小。

10.可选的,在本技术的一些实施例中,所述第二显示子区的宽度为10毫米至200毫米。

11.可选的,在本技术的一些实施例中,至少部分靠近所述基板边缘的所述像素单元中,不同所述像素单元对应的所述阵列电极的宽度相同,所述阵列电极的长度自所述基板中心向所述基板边缘逐渐减小。

12.可选的,在本技术的一些实施例中,至少部分靠近所述基板边缘的所述像素单元中,不同所述像素单元对应的所述阵列电极的长度相同,所述阵列电极的宽度自所述基板中心向所述基板边缘逐渐减小。

13.可选的,在本技术的一些实施例中,至少部分靠近所述基板边缘的所述像素单元中,不同所述像素单元对应的所述阵列电极的长度和宽度均自所述基板中心向所述基板边缘逐渐减小。

14.可选的,在本技术的一些实施例中,至少部分靠近所述基板边缘的所述像素单元中,所述像素单元中的所述阵列电极以长度和/或宽度为0.1微米至0.5微米的差值自所述基板中心向所述基板边缘逐渐减小。

15.可选的,在本技术的一些实施例中,所述阵列基板还包括绝缘层,所述绝缘层设置在所述基板上,所述阵列电极设置在所述绝缘层远离所述基板的一侧。

16.相应的,本技术实施例还提供一种显示面板,包括:

17.阵列基板,所述阵列基板为以上任一项所述的阵列基板;

18.对向基板,所述对向基板与所述阵列基板相对设置;

19.液晶层,所述液晶层设置在所述阵列基板与所述对向基板之间。

20.本技术实施例公开一种阵列基板及显示面板。本技术实施例提供的阵列基板中,至少部分靠近基板边缘的像素单元中的阵列电极的面积自基板中心向基板边缘逐渐减小。其中,可以将阵列电极面积逐渐减小的部分设置在显示面板的亮度偏亮的区域。阵列电极的面积减小,则像素单元的开口率减小。像素单元的开口率减小后,可以降低阵列基板边缘区域的光线穿透率。由此,使基板边缘光线偏亮的部分与基板中心的亮度相当,进而实现对显示面板的周边显示不均的改善。

附图说明

21.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

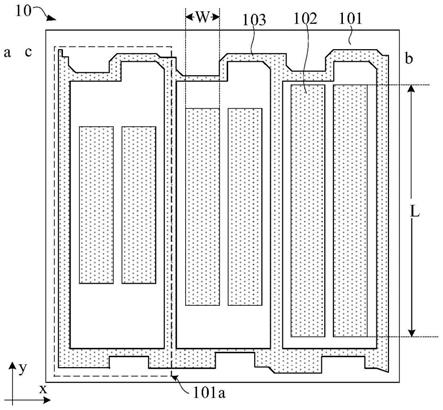

22.图1是本技术实施例提供的阵列基板的第一种结构示意图;

23.图2是本技术实施例提供的图1中a处的第一种放大示意图;

24.图3是本技术实施例提供的图1中a处的第二种放大示意图;

25.图4是本技术实施例提供的图1中a处的第三种放大示意图;

26.图5是本技术实施例提供的阵列基板的第一种阵列电极排布示意图;

27.图6是本技术实施例提供的阵列基板的第二种阵列电极排布示意图;

28.图7是本技术实施例提供的阵列基板的第二种结构示意图;

29.图8是本技术实施例提供的显示面板的一种结构示意图。

具体实施方式

30.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本技术,并不用于限制本技术。在本技术中,在未作相反说明的情况下,使用的方

位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

31.本技术实施例提供一种背光驱动电路及液晶显示装置。以下分别进行详细说明。需说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。

32.请参阅图1和图2,图1是本技术实施例提供的阵列基板的第一种结构示意图。图2是本技术实施例提供的图1中a处的第一种放大示意图。本技术实施例提供的阵列基板10包括基板101以及多个阵列电极102。基板101上设置有多个像素单元101a。至少一阵列电极102对应设置在一像素单元101a内。其中,自基板中心b向基板边缘a排列的像素单元101a中,至少部分像素单元101a对应的阵列电极102的面积沿排列方向逐渐减小。

33.其中,基板101可以采用柔性衬底制作。其中,柔性衬底采用的材料为聚合物材料,具体地,柔性衬底采用的材料可以为聚酰亚胺(polyimide,pi)、聚乙烯(polyethylene,pe)、聚丙烯(polypropylene,pp)、聚苯乙烯(polystyrene,ps)、聚对苯二甲酸乙二醇酯(polyethylene glycol terephthalate,pet)或聚萘二甲酸乙二醇酯(polyethylene naphthalate two formic acid glycol ester,pen)。聚合物材料的柔韧性好、质量轻、耐冲击,适用于柔性显示面板。其中,聚酰亚胺还能够实现良好的耐热性和稳定性。

34.在一些显示面板的阵列基板中,由于受到馈通(feedthrough)效应的影响,在显示面板发光时,显示面板的边缘会较中心区域偏亮。在实际制程中,阵列基板中的膜层边缘的厚度薄于膜层中心的厚度。例如,聚酰亚胺作为基板时,其膜层边缘的厚度会较中心偏薄约10%。根据feedthrough公式:

35.vft=cgs(vgh-vgl)/(cst+clc+cgs)

36.其中,vft是指馈通电压,cgs是指栅源寄生电容,cst是指存储电容,clc是指液晶电容,vgh是指栅极驱动走线打开时的电压,vgl是指栅极驱动走线关闭时的电压。

37.feedthrough效应具体是指由于制程导致阵列基板边缘较薄,进而导致边缘区域的存储电容cst降低。存储电容cst降低,则会使得馈通电压vft增加。由于显示面板是以阵列基板的中心点设定公共电压vcom,因此会导致边缘区域的公共电压偏离vcom,使得显示面板边缘位置偏亮。

38.因此,在本技术实施例提供的阵列基板10中,至少部分靠近基板边缘a的像素单元101a中,阵列电极102的面积沿基板中心b向基板边缘a的方向逐渐减小。其中,可以将阵列电极102面积逐渐减小的部分设置在显示面板的亮度偏亮的区域。阵列电极102的面积减小,则像素单元101a的开口率减小。像素单元101a的开口率减小后,可以降低阵列基板10边缘区域的光线穿透率。由此,使基板边缘a光线偏亮的部分与基板中心b的亮度相当,进而实现对显示面板的周边显示不均的改善。

39.可选的,请继续参阅图1,阵列基板10包括显示区10a和非显示区10b。非显示区10b围绕显示区10a设置。其中,显示区10a包括第一显示子区101a与第二显示子区102a。第二显示子区102a设置在第一显示子区101a的至少一侧。第二显示子区102a中,不同像素单元101a对应的阵列电极102的面积自基板中心b向第二显示子区102a的边缘c逐渐减小。另外,在图1中,是以第二显示子区102a围绕第一显示子区101a设置为例进行示意。

40.可选的,第二显示子区102a的宽度d为10毫米至200毫米。具体的,第二显示子区102a的宽度d为10毫米、20毫米、30毫米、40毫米、50毫米、60毫米、70毫米、80毫米、90毫米、

100毫米、110毫米、120毫米、130毫米、140毫米、150毫米、160毫米、170毫米、180毫米、190毫米或200毫米。第二显示子区102a的宽度d为10毫米至200毫米,即在阵列基板10显示区10a的边缘区域,距离边缘10毫米至200毫米的区域内,将阵列电极102设置为面积渐变式排列。这是由于阵列基板10的膜层厚度不均问题,主要产生在距离边缘10毫米至200毫米的区域内。根据制程工艺的精度不同,膜层偏薄的区域会有不同,因此,对第二显示子区102a的宽度d进行范围限定,具体的阵列电极102面积渐变的宽度可以根据具体显示面板的不同、制程工艺精度的区别进行调整,以得到最好的显示效果的显示面板。

41.请继续参阅图2,图2对图1中的第二显示子区102a进行了局部放大示意。图2所示出的是像素单元101a中的阵列电极102的面积沿基板中心b向第二显示子区边缘c的方向逐渐减小。

42.也就是在第二显示子区102a中,设置为像素单元101a中的阵列电极102的面积沿基板中心b向基板边缘a的方向逐渐减小。

43.可选的,请继续参阅图2,至少部分靠近基板边缘a的像素单元101a中,不同像素单元101a对应的阵列电极102的宽度w相同,阵列电极102的长度l自基板中心b向基板边缘a逐渐减小。

44.阵列电极102的长度减小后,能够增大阵列电极102周围的布线空间,可以在长度方向上节省出来的空间内设置电容器或其他电路元件,提高阵列电路的工作效率。例如在长度l减小后,在阵列电极102第二方向y上的两侧连接电容,再利用feedthrough公式减小馈通电压vft,进一步改善显示面板显示不均的问题。

45.可选的,请参阅图1和图3,图3是本技术实施例提供的图1中a处的第二种放大示意图。其中,至少部分靠近基板边缘a的像素单元101a中,不同像素单元101a对应的阵列电极102的长度l相同,阵列电极102的宽度w自基板中心b向基板边缘a逐渐减小。

46.阵列电极102的宽度减小,能够给周围的走线提供更大的布线空间,一方面,能够在保证走线宽度不变的情况下增大像素数量,提高分辨率。另一方面,可以在保证分辨率不变的情况下,增大周围走线的宽度,降低走线电阻。

47.可选的,请参阅图1和图4,图4是本技术实施例提供的图1中a处的第三种放大示意图。至少部分靠近基板边缘a的像素单元101a中,不同像素单元101a对应的阵列电极102的长度l和宽度w均自基板中心b向基板边缘a逐渐减小。

48.在阵列电极102的长度l和宽度w均减小的情况下,则可以在阵列电极102在长度方向上的两侧设置其他电路元件优化电路。同时,在宽度方向上增大了布线空间,可以增大周围布线的宽度,减小走线的电阻。

49.可选的,至少部分靠近基板边缘a的像素单元101a中,像素单元101a中的阵列电极102以长度l和/或宽度w为0.1微米至0.5微米的差值沿基板中心b向基板边缘a的方向逐渐减小。

50.需要说明的是,长度l和/或宽度w进行渐变设计可以根据显示面板的具体需求进行选择。渐变的差值选用0.1微米至0.5微米。具体的,像素单元101a中的阵列电极102以长度l和/或宽度w为0.1微米、0.15微米、0.2微米、0.25微米、0.3微米、0.35微米、0.4微米、0.45微米或0.5微米的差值沿基板中心b向基板边缘a的方向逐渐减小。

51.经过实验测定,阵列基板10上的膜厚差距基本处于10埃至100埃之间。因此,在这

样的膜厚差距下,根据膜厚的差值对阵列电极102的渐变梯度进行适应性设计。例如,当膜厚差距较小时,可以以10微米的梯度减小阵列电极的宽度w或长度l。当膜厚差距较大时,可以以200微米的梯度减小阵列电极的宽度w或长度l。

52.可以理解的是,在制程工艺允许的范围内,应选用较小的渐变差值对阵列电极102进行设置。由于阵列基板10上的膜厚不均是非常细微的,因此,阵列电极的渐变差值选用较小的数值可以对膜厚不均进行更匹配的补偿,也不会由于像素开口率梯度差距较大产生新的亮度不均问题。需要说明的是,本技术实施例提供的阵列电极102设置为渐变的区域是10毫米至200毫米的区域。因此,可以在渐变区域范围较大时,选择较大的渐变梯度,以降低制程难度。在渐变区域范围较小时,选择较小的渐变梯度,提升对显示面板显示的优化效果。

53.其中,在图2至在图4中,在阵列电极102的周围还设置有走线103。走线103可以是数据线、扫描线或者阵列基板10上的其他走线。在本技术实施例中,走线103可以表示数据线和扫描线,走线103交叉设置可以划定像素单元101a。

54.可选的,请参阅图5,图5是本技术实施例提供的阵列基板的第一种阵列电极排布示意图。图5中为了示意阵列电极102的排布方式,对基板101和阵列电极102的比例进行了夸大处理,图3中所示出的比例不作为对本技术实施例的限制。

55.可以理解的是,图5以第二显示子区102a设置在第一显示子区101a的两侧为示例进行说明。第二显示子区102a还可以仅设置在第一显示子区101a的一侧。

56.可选的,第二显示子区102a设置在第一显示子区101a的两侧。其中,阵列电极102的自基板中心b向第二显示子区102a的边缘面积逐渐减小,第二显示子区边缘c是指阵列电极102所处的第二显示子区102a的边缘。在第二显示子区102a中,由于阵列基板10的长边膜厚不均的问题较短边更严重,因此,可以选择将第二显示子区102a设置在第一显示子区101a的阵列基板10长边方向的两侧,则阵列电极102在阵列基板10长边的边缘区域自基板中心b向第二显示子区边缘c逐渐减小面积,可以改善阵列基板膜厚不均导致的显示不均问题。

57.具体的,请参阅图6,图6是本技术实施例提供的阵列基板的第二种阵列电极排布示意图。图6所示的实施例与图3所示的实施例的区别在于,第二显示子区102a至少设置在第一显示子区101a的第一侧d和第二侧e。第一侧d与第二侧e相交。设置在第一侧d的第二显示子区102a中,不同像素单元101a对应的阵列电极102的面积沿基板中心b向第一侧d的方向逐渐减小。设置在第二侧e的第二显示子区102a中,不同像素单元101a对应的阵列电极102的面积沿基板中心b向第二侧e的方向逐渐减小。

58.可选的,请参阅图7,图7是本技术实施例提供的阵列基板的第二种结构示意图。阵列基板10还包括绝缘层104。绝缘层104设置在基板101上。阵列电极102设置在绝缘层104远离基板101的一侧。

59.可选的,绝缘层104可以是栅极绝缘层、层间绝缘层或钝化层。在阵列基板10上,这些绝缘膜层通常是整面设置的,因此,更容易在边缘区域发生厚度不均的问题。例如,在制程中,栅极绝缘层的膜厚边缘会较中心偏薄约10%。

60.需要说明的是,图7中仅示出了基板10上的绝缘层104和阵列电极102。基板10上还设置有其他膜层,例如栅极层、源漏极层、平坦化层等。基板上的其他膜层及其装配是本领域技术人员所熟知的技术手段,在此不做赘述。

61.相应的,本技术实施例还提供一种显示面板。请参阅图8,图8是本技术实施例提供的显示面板的一种结构示意图。显示面板100包括阵列基板10、对向基板20以及液晶层30。阵列基板10为以上所述的阵列基板10。对向基板20与阵列基板10相对设置。液晶层30设置在阵列基板10与对向基板20之间。

62.其中,阵列基板10包括基板101,设置于基板101上的遮光层,设置在基板上并覆盖遮光层的缓冲层,从下到上依次层叠于缓冲层上的有源层、栅极绝缘层和栅极层,位于缓冲层上方并覆盖有源层、栅极绝缘层和栅极的层间介质层。有源层包括沟道区以及位于沟道区两侧的源极区和漏极区,位于层间介质层上的源极和漏极,源极与漏极分别和源极区和漏极区电性连接。源极和漏极上还覆盖有平坦化层。阵列基板10的具体膜层设置在附图中未示出,阵列基板10还可以包括其他结构,阵列基板10的结构及其具体设置是本领域常用的技术手段,在此不再赘述。

63.需要说明的是,本技术中不限制阵列基板10中形成的薄膜晶体管的结构,薄膜晶体管可以为顶栅型薄膜晶体管,也可以为底栅型薄膜晶体管,可以为双栅极型薄膜晶体管,也可以为单栅极型薄膜晶体管。对于薄膜晶体管的具体结构在本技术中不再赘述。

64.其中,阵列电极102可以是显示面板的公共电极或像素电极。例如,阵列电极102作为公共电极设置在像素单元101a内,用于调节液晶层的偏转方向。

65.以上对本技术实施例所提供的一种背光驱动电路及液晶显示装置进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。