一种dmd电路板及dlp光机模组

技术领域

1.本发明涉及数字光处理技术领域,特别涉及一种dmd电路板。本发明还涉及一种dlp光机模组。

背景技术:

2.dlp(digital light processing,数字光处理)技术是一种成像技术,主要通过对影像信号进行数字化处理,再通过dmd(digital micromirror device,数字微镜晶片)实现可视数字信息投影显示。

3.dmd是dlp光机模组的关键器件,dmd设计的优劣直接影响着dlp光机模组的电性能和光学性能。dmd是在芯片上布置由大量微镜片所组成的矩阵,每一个微镜片控制投影画面中的一个像素,且微镜片的数量与投影画面的分辨率相符。这些微镜片在数字驱动信号的控制下能够迅速改变角度,从而使入射光的反射方向改变。微镜片在两种状态间切换的频率是可以变化的,这使得dmd反射出的光线呈现出黑与白之间的各种灰度。

4.目前,为满足产品轻薄小型化的需求,dmd电路板多采用fpc(flexible printed circuit,柔性电路板)进行设计,但由于制程能力的限制,fpc的层面数量无法做到与常规pcb的层面数量相当,使得dmd电路板的叠构、板厚、板材等参数受到诸多限制,如此将对dmd电路板的抗esd(electro-static discharge,静电释放)性能、抗emi(electromagnetic interference,电磁干扰)性能等造成不利影响,最终导致dmd电路板的信号完整性较差。

5.在现有技术中,通常是通过在dmd电路板的外部包裹导电布或在表面额外贴装导电泡棉等导电材料的方式来提高产品的抗esd和抗emi性能,然而此种方法不仅工艺步骤多,而且生产成本较高,同时对dmd电路板的信号完整性存在不利影响,产品可靠性存在风险。

6.因此,如何高效、低成本地提高dmd电路板的信号完整性,是本领域技术人员面临的技术问题。

技术实现要素:

7.本发明的目的是提供一种dmd电路板,能够高效、低成本地提高信号完整性。本发明的另一目的是提供一种dlp光机模组。

8.为解决上述技术问题,本发明提供一种dmd电路板,包括基板体、设置于所述基板体的其中一侧表面的若干个电子元器件、设置于所述基板体的另一侧表面并与各所述电子元器件的位置对应的若干个补强板,各所述电子元器件与对应的所述所述补强板之间通过地属性的过孔相连,且各所述补强板均与dlp光机模组的接地壳体电性连接。

9.优选地,所述电子元器件包括dmd芯片,且所述dmd芯片对应的所述补强板上设置有散热器。

10.优选地,所述散热器为导体,且所述散热器与dlp光机模组的接地壳体电性连接。

11.优选地,所述散热器与对应的所述补强板之间连接有具有导电性的导热材料层。

12.优选地,所述基板体包括至少4层芯板,且非表层的其中一层所述芯板为高速信号板,各所述电子元器件的阻抗信号线均分布于所述高速信号板上。

13.优选地,各所述阻抗信号线的走线方向两侧均平行分布有地信号线。

14.优选地,与所述高速信号板相邻的两层所述芯板上与各所述阻抗信号线的对应区域均分布有地属性导体,且所述地属性导体的宽度大于对应的所述阻抗信号线的线宽。

15.优选地,各所述电子元器件均分布于所述基板体的同一侧表面,且所述基板体的对侧表面与各所述补强板的对应位置处均设置有地属性导体。

16.优选地,各所述电子元器件分别分布于所述基板体的两侧表面,且所述基板体的两侧表面与各所述补强板的对应位置处均设置有地属性导体。

17.本发明还提供一种dlp光机模组,包括接地壳体和设置于所述接地壳体内的dmd电路板,其中,所述dmd电路板具体为上述任一项所述的dmd电路板。

18.本发明所提供的dmd电路板,主要包括基板体、电子元器件、补强板和过孔。其中,基板体为dmd电路板的主体结构,主要用于安装各种电子元器件。各个电子元器件设置在基板体上,且设置在基板体的其中一侧表面(如顶部表面或底部表面)上。补强板也设置在基板体上,并具体位于基板体的另一侧表面,一般设置有多个,各个补强板在基板体的另一侧表面上的设置位置与跟其对应的电子元器件在基板体的其中一侧表面上的设置位置互相对应,主要用于增强电子元器件所处位置的基板体部位的结构强度,提高安装稳定性。过孔开设在基板体内,并且一端与各个电子元器件相连,另一端与跟各个电子元器件对应的补强板相连,同时,该过孔的电气属性为接地孔。并且,各个补强板还均与dlp光机模组的接地壳体保持电性连接。如此,本发明提供的dmd电路板,通过地属性的过孔将电子元器件与补强板相连,再通过补强板与dlp光机模组的接地壳体相连,使得dmd电路板直接通过补强板与接地壳体(整机)形成接地,相比于现有技术,无需额外使用导电布或导电泡棉等部件实现接地,且静电释放路程短、路径直接,因此能够增强dmd电路板的抗esd性能、抗emi性能,进而能够高效、低成本地提高dmd电路板的信号完整性。

附图说明

19.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

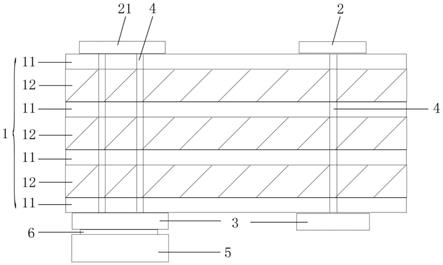

20.图1为本发明所提供的一种具体实施方式的整体结构示意图。

21.图2为各个电子元器件在基板体上的另一种分布情况示意图。

22.图3为阻抗信号线与地信号线在高速信号板上的分布情况示意图。

23.图4为阻抗信号线的阻抗设计示意图。

24.其中,图1—图4中:

25.基板体—1,电子元器件—2,补强板—3,过孔—4,散热器—5,导热材料层—6;

26.芯板—11,介质板—12,dmd芯片—21,阻抗信号线—22,地信号线—23。

具体实施方式

27.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

28.请参考图1,图1为本发明所提供的一种具体实施方式的整体结构示意图。

29.在本发明所提供的一种具体实施方式中,dmd电路板主要包括基板体1、电子元器件2、补强板3和过孔4。

30.其中,基板体1为dmd电路板的主体结构,主要用于安装各种电子元器件2,通常为多层复合板,包括多层芯板11和夹持在相邻两层芯板11之间的介质板12。

31.各个电子元器件2设置在基板体1上,且通常设置在基板体1的其中一侧表面(如顶部表面或底部表面)上。

32.补强板3也设置在基板体1上,并具体位于基板体1的另一侧表面,一般设置有多个,各个补强板3在基板体1的另一侧表面上的设置位置与跟其对应的电子元器件2在基板体1的其中一侧表面上的设置位置互相对应,主要用于增强电子元器件2所处位置的基板体1部位的结构强度,提高安装稳定性。

33.过孔4开设在基板体1内,并且一端与各个电子元器件2相连,另一端与跟各个电子元器件2对应的补强板3相连,同时,该过孔4的电气属性为接地孔。并且,各个补强板3还均与dlp光机模组的接地壳体保持电性连接。

34.如此,本实施例提供的dmd电路板,通过地属性的过孔4将电子元器件2与补强板3相连,再通过补强板3与dlp光机模组的接地壳体相连,使得dmd电路板直接通过补强板3与接地壳体(整机)形成接地,相比于现有技术,无需额外使用导电布或导电泡棉等部件实现接地,且静电释放路程短、路径直接,因此能够增强dmd电路板的抗esd性能、抗emi性能,进而能够高效、低成本地提高dmd电路板的信号完整性。

35.在关于电子元器件2与补强板3的一种优选实施例中,各个电子元器件2均分布在基板体1的同一侧表面,比如均分布在基板体1的顶部表面(top)或底部表面(bottom),相应的,各个补强板3均分布在基板体1的对侧(即另一侧)表面。比如,若各个电子元器件2均分布在基板体1的顶部表面,则各个补强板3均分布在基板体1的底部表面,反之亦然。此外,为便于实现基板体1与补强板3之间的电性连接,本实施例在基板体1的对侧表面上与各个补强板3相对应的位置处均设置有地属性导体,比如gnd属性的铜箔等。

36.如图2所示,图2为各个电子元器件2在基板体1上的另一种分布情况示意图。

37.在关于电子元器件2与补强板3的另一种优选实施例中,各个电子元器件2不均分布在基板体1的同一侧表面,而是分别分布在基板体1的两侧表面,即部分电子元器件2分布在基板体1的顶部表面(top),同时另一部分电子元器件2分布在基板体1的底部表面(bottom),相应的,各个补强板3同时分布在基板体1的两侧表面。当然,各个补强板3在基板体1的两侧表面上的分布位置仍然与各自对应的电子元器件2的分布位置互相正对。同理,为便于实现基板体1与补强板3之间的电性连接,本实施例在基板体1的两侧表面上与各个补强板3相对应的位置处均设置有地属性导体,比如gnd属性的铜箔等。

38.一般的,补强板3可采用钢板、铁板、铜合金板等。

39.在关于电子元器件2的一种优选实施例中,该电子元器件2主要包括dmd芯片21(ic)和连接器、flash等其余相关部件,根据前述两种分布情况,dmd芯片21与其余相关部件可以在基板体1上共面分布,也可以异面分布。

40.同时,考虑到dmd芯片21在运行时会产生大量的热,为保证dmd芯片21的散热性能,本实施例中增设了主要用于与dmd芯片21进行散热的散热器5。具体的,为便于安装,本实施例将该散热器5设置在dmd芯片21对应的补强板3上,并使散热器5的吸热面与补强板3的表面紧贴。如此设置,不仅能够利用补强板3实现散热器5的稳定安装,还能够利用补强板3作为热量传递链,使得dmd芯片21以及其余电子元器件2的热量通过基板体1、过孔4传递至补强板3上,便于散热器5吸收。

41.进一步的,为便于补强板3与dlp光机模组的接地壳体之间的电性连接,本实施例中的散热器5具体为导体,并且利用散热器5的散热片与dlp光机模组的接地壳体形成电性连接。如此设置,在产生静电时,即通过补强板3、散热器5释放至接地壳体上,进而释放至大地。

42.不仅如此,为提高散热器5的吸热效率和静电释放通路的稳定性,本实施例中,散热器5与对应的补强板3之间通过导热材料层6相连,并且该导热材料层6具有导电性。

43.在关于基板体1的一种优选实施例中,该基板体1包括至少4层芯板11,并且其中的非表层(顶部表层、底部表层)的其中一层内部芯板11具体为高速信号板,同时各个电子元器件2的阻抗信号线22均分布在该高速信号板上,专用于进行高速信号走线,比如差分信号线或单端信号线等。如此设置,由于高速信号板位于基板体1的内层位置,阻抗信号线22远离表层,因此不容易受到外界的电磁干扰,抗emi性能得到加强。

44.以基板体1包括4层芯板11为例,表层为top层芯板11和bottom芯板11,内部芯板11具有两层,可取与top层相邻的内部芯板11作为高速信号板,也可取与bottom层相邻的内部芯板11作为高速信号板。

45.如图3所示,图3为阻抗信号线22与地信号线23在高速信号板上的分布情况示意图。

46.同时,为进一步增强抗emi性能,本实施例还在高速信号板上于各个阻抗信号线22的走线方向的两侧位置均平行分布有地信号线23。比如在单端信号线的两侧一定距离处同时分布两条平行的地信号线23,或者在若干个成组的差分信号线的两侧一定距离处同时分布两条平行的地信号线23,从而通过地信号线23的包裹加强抗emi性能。

47.进一步的,考虑到阻抗信号线22需要搭配参考地而使用,在本实施例中,与高速信号板相邻的两层芯板11上与各阻抗信号线22的对应区域均分布有地属性导体,比如gnd铜箔等。同时,为确保阻抗信号线22的参考地的完整性,进而增强抗emi性能,在本实施例中,与高速信号板相邻的两层芯板11上分布的各个地属性导体的宽度,均大于对应的阻抗信号线22的线宽。一般的,地属性导体的宽度相比于阻抗信号线22要沿宽度方向单侧向外扩张2倍阻抗信号线22的线宽。比如阻抗信号线22的线宽为0.1mil,则地属性导体的单侧宽度需要增加0.2mil。

48.如图4所示,图4为阻抗信号线22的阻抗设计示意图。

49.另外,通过dmd电路板的试验可知,部分单端阻抗线的阻抗通常较低,为保证信号完整性,需要适当提高单端阻抗线的阻抗。通过特性阻抗z的计算公式:

[0050][0051]

可知,单端阻抗线的阻抗与其线宽w(反比)、介质板12的厚度h(正比)、芯板11的厚度t(反比)、基材介电常数er(反比)相关,因此可以通过增加h、减少t、减少w的方式提高阻抗,但h的增加会对基板体1的弯折效果有影响,且线宽太细在使用过程中会有断路的风险,经多次实验验证,考虑到fpc所使用的基材铜厚最薄的为1/3oz(约12um),因此,本实施例中优选h=0.05mm、t=12um、w=0.03mm的基板体1参数,同时对芯板11的厚度通过工艺方法进行消减处理,能够实现68

±

6.8ω的标准阻抗要求,且不会影响基板体1的弯折效果,也不会对长期使用造成可靠性方面的影响。

[0052]

本实施例还提供一种dlp光机模组,主要包括接地壳体和设置于接地壳体内的dmd电路板,其中,该dmd电路板的具体内容与上述相关内容相同,此处不再赘述。

[0053]

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。