1.本发明的实施例涉及显示装置及其驱动方法。

背景技术:

2.随着信息化技术的发展,使用者和信息间的连接媒体即显示装置的重要性日益凸显。响应于此,液晶显示装置(liquid crystal display device)以及有机发光显示装置(organic light emitting display device)等之类显示装置(display device)的使用正在增加。

3.显示装置包括像素,各个像素包括发光元件以及向发光元件供应驱动电流的驱动晶体管。各个像素被劣化,例如,驱动晶体管的阈值电压以及迁移率随时间变化,发光元件可能劣化。为了补偿像素的劣化,利用通过外部的补偿电路来感应像素(即,驱动晶体管以及发光元件)的特性信息的技术。

技术实现要素:

4.外部补偿电路通过缓冲放大器向像素施加感应电压,从像素接收感应信号,从而能够测定驱动晶体管的阈值电压。但是,与多个数据线的各个连接的缓冲放大器由于制造时工艺上的原因,可能存在增益(gain)之类配置上的差异,感应时可能发生沟道间偏差。

5.当发生沟道间偏差时,不能执行对显示装置的准确补偿,可能发生在屏幕上出现竖线等的不良。

6.本发明所要解决的技术问题是提供一种能够减少外部补偿电路的沟道偏差的显示装置。

7.本发明所要解决的另一技术问题是提供一种能够减少外部补偿电路的沟道偏差的显示装置的驱动方法。

8.但是,本发明的目的不限于上述的目的,可以在不脱离本发明的构思以及领域的范围内进行各种扩展。

9.用于解决所述技术问题的根据本技术发明的一实施例的显示装置包括:显示部,包括与数据线以及感应线连接的多个像素;数据驱动部,包括在第一感应时段期间向所述数据线供应第一感应电压的多个缓冲放大器以及在所述第一感应时段期间通过所述感应线从所述像素接收第一感应信号的感应部;以及一个格劳保放大器(global),在与所述第一感应时段不同的第二感应时段期间向所述数据线提供第二感应电压。

10.所述感应部在所述第二感应时段期间通过所述感应线从所述像素接收对应于所述第二感应电压的第二感应信号,并基于所述第一感应信号以及所述第二感应信号的差值生成补偿数据。

11.可以是,所述第二感应电压具有与所述第一感应电压相同的值。

12.可以是,所述第二感应信号具有比所述第一感应信号大的值。

13.可以是,所述第一感应信号是从所述第一感应电压减去包括在各个所述像素中的

驱动晶体管的阈值电压以及所述缓冲放大器的电压偏差的值,所述第二感应信号是从所述第二感应电压减去所述驱动晶体管的阈值电压的值。

14.可以是,各个所述像素包括:第一子像素,与所述数据线中的第一数据线连接;第二子像素,与所述数据线中的第二数据线连接;以及第三子像素,与所述数据线中的第三数据线连接。

15.可以是,所述第一子像素、所述第二子像素以及所述第三子像素与所述感应线中的一个感应线接通。

16.可以是,所述格劳保放大器的输出端通过第一开关与所述第一数据线连接,并通过第二开关与所述第二数据线连接,并且通过第三开关与所述第三数据线连接。

17.可以是,所述第一开关、所述第二开关以及所述第三开关各自在所述第一感应时段期间处于开路状态。

18.可以是,在所述第二感应时段期间,当所述第一开关处于闭路状态时,所述第二开关以及所述第三开关处于开路状态,与所述第一数据线连接的第一缓冲放大器处于高阻抗(hi-z)状态,与所述第二数据线连接的第二缓冲放大器以及与所述第三数据线连接的第三缓冲放大器输出对应于最低灰度的数据电压。

19.可以是,在所述第二感应时段期间,当所述第二开关处于闭路状态时,所述第一开关以及所述第三开关处于开路状态,所述第二缓冲放大器处于高阻抗(hi-z)状态,所述第一缓冲放大器以及所述第三缓冲放大器输出对应于最低灰度的数据电压。

20.可以是,在所述第二感应时段期间,当所述第三开关处于闭路状态时,所述第一开关以及所述第二开关处于开路状态,所述第三缓冲放大器处于高阻抗(hi-z)状态,所述第一缓冲放大器以及所述第二缓冲放大器输出对应于最低灰度的数据电压。

21.可以是,所述显示装置还包括:定时控制部,从外部接收第一数据,并将所述图像数据和所述补偿数据相加而生成第二数据,将所述第二数据向所述数据驱动部提供。

22.可以是,所述显示装置还包括:模数转换器,接通在所述感应部的输出端和所述定时控制部之间,并将所述感应电压从模拟形式转换成数字形式。

23.可以是,所述显示部还包括扫描线、感应控制线、第一电源线以及第二电源线,各个所述像素包括:第一晶体管,包括与所述第一电源线连接的第一电极、与第一节点连接的栅极电极以及与第二节点连接的第二电极;第二晶体管,包括与所述数据线连接的第一电极、与所述第一节点连接的第二电极以及与所述扫描线连接的栅极电极;第三晶体管,包括与所述第二节点连接的第一电极、与所述感应线连接的第二电极以及与所述感应控制线连接的栅极电极;存储电容器,连接在所述第一节点和所述第二节点之间;以及发光元件,连接在所述第二节点和所述第二电源线之间。

24.可以是,在所述第一感应时段以及所述第二感应时段中的至少一部分时段期间,所述第一晶体管以及所述第三晶体管导通。

25.可以是,所述感应部还包括:初始化开关,连接在初始化电源和所述感应线之间;以及感应电容器,连接在所述感应线和基准电源之间。

26.可以是,当所述初始化开关处于开路状态且所述第三晶体管导通时,利用通过所述第二节点提供的电流对所述感应电容器进行充电。

27.可以是,所述显示装置还包括:电源稳定化电容器,与连接于所述格劳保放大器的

输出端的第一电极以及基准电源连接。

28.根据本发明的一实施例的显示装置的驱动方法在具备包括与数据线以及感应线连接的多个像素的显示部的显示装置中包括:在数据驱动部中,通过多个缓冲放大器在第一感应时段期间向所述数据线供应第一感应电压的步骤;在所述数据驱动部中,由感应部在所述第一感应时段期间通过所述感应线从所述像素接收第一感应信号的步骤;在格劳保放大器中,在与所述第一感应时段不同的第二感应时段期间向所述数据线供应第二感应电压的步骤;在所述数据驱动部中,由所述感应部在所述第二感应时段期间通过所述感应线从所述像素接收对应于所述第二感应电压的第二感应信号的步骤;以及在所述数据驱动部中,由所述感应部基于所述第一感应信号以及所述第二感应信号的差值生成补偿数据的步骤。

29.可以是,所述第二感应电压具有与所述第一感应电压相同的值,所述第二感应信号具有比所述第一感应信号大的值。

30.可以是,各个所述像素包括:第一子像素,与所述数据线中的第一数据线连接;第二子像素,与所述数据线中的第二数据线连接;以及第三子像素,与所述数据线中的第三数据线连接,所述格劳保放大器的输出端通过第一开关与所述第一数据线连接,并通过第二开关与所述第二数据线连接,并且通过第三开关与所述第三数据线连接。

31.可以是,所述格劳保放大器的输出端通过第一开关与所述第一数据线连接,并通过第二开关与所述第二数据线连接,并且通过第三开关与所述第三数据线连接。

32.可以是,供应所述第二感应电压的步骤包括:在所述第二感应时段期间,所述第一开关导通,所述第二开关以及所述第三开关断开,与所述第一数据线连接的第一缓冲放大器处于高阻抗(hi-z)状态,通过与所述第二数据线连接的第二缓冲放大器以及与所述第三数据线连接的第三缓冲放大器输出对应于最低灰度的数据电压的步骤;在所述第二感应时段期间,所述第二开关导通,所述第一开关以及所述第三开关断开,所述第二缓冲放大器处于高阻抗(hi-z)状态,通过所述第一缓冲放大器以及所述第三缓冲放大器输出对应于最低灰度的数据电压的步骤;以及在所述第二感应时段期间,所述第三开关导通,所述第一开关以及所述第二开关断开,所述第三缓冲放大器处于高阻抗(hi-z)状态,通过所述第一缓冲放大器以及所述第二缓冲放大器输出对应于最低灰度的数据电压的步骤。

33.(发明效果)

34.根据本发明的实施例的显示装置通过格劳保放大器将相同的感应电压施加于像素,从而能够减小外部补偿电路的沟道偏差。

35.根据本发明的实施例的显示装置的驱动方法通过格劳保放大器将相同的感应电压施加于像素,从而能够减小外部补偿电路的沟道偏差。

36.但是,本发明的效果不限于上述的效果,可以在不脱离本发明的构思以及领域的范围内进行各种扩展。

附图说明

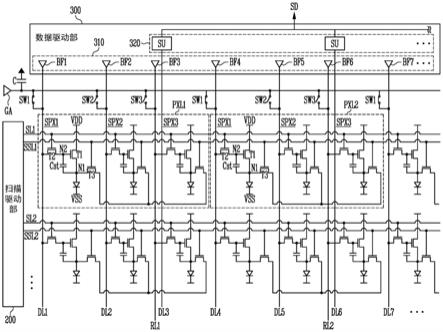

37.图1是示出根据本发明的一实施例的显示装置的图。

38.图2是示出包括在图1的显示装置中的子像素的一例的电路图。

39.图3是用于说明感应时段期间像素、数据驱动部以及格劳保放大器(global)间的

工作的图。

40.图4是具体示出根据本发明的一实施例的图3的数据驱动部的信号输出部的电路图。

41.图5是示出根据本发明的一实施例的图3的感应部的电路图。

42.图6a是示出在第一感应时段存储于感应电容器中的感应信号的电压值的波形图。

43.图6b是示出在第二感应时段存储于感应电容器中的感应信号的电压值的波形图。

44.图7是示出根据本发明的一实施例的显示装置的驱动方法的流程图。

45.图8是示出根据本发明的一实施例的定时控制部的接口信号的信号图。

具体实施方式

46.以下,参照所附附图,更详细地说明本发明的优选实施例。针对附图中的相同的构成要件使用相同的附图标记,省略针对相同的构成要件重复的说明。

47.图1是示出本发明的一实施例的显示装置的图。

48.参照图1,显示装置10可以包括显示部100、扫描驱动部200、数据驱动部300、定时控制部400以及格劳保放大器(global)ga。

49.显示部100可以包括扫描线sl、感应控制线ssl、数据线dl以及感应线rl(或者,读出线)以及子像素spx。

50.子像素spx可以位于被扫描线sl、感应控制线ssl、数据线dl以及感应线rl划分的区域。显示部100包括多个像素,例如,多个像素可以连接于一个数据线dl以及感应线rl。关于子像素spx的具体结构,参照图2来后述。

51.定时控制部400基于垂直同步信号vsync、水平同步信号hsync以及数据使能信号de等定时信号生成用于控制数据驱动部300的工作定时的数据控制信号ddc和用于控制扫描驱动部200的工作定时的扫描控制信号gdc。定时控制部400可以时间上分离执行图像显示的时段和执行外部补偿的时段(或者,感应时段),彼此不同地生成用于图像显示的控制信号ddc、gdc和用于外部补偿的控制信号ddc、gdc。

52.外部补偿是感应包括在子像素spx中的发光元件及/或驱动晶体管的驱动特性并根据其感应值校正输入数据(或者,第一数据data1)的技术。发光元件的驱动特性意指发光元件的工作点电压,驱动晶体管的驱动特性意指驱动晶体管的阈值电压以及驱动晶体管的电子迁移率。

53.另外,定时控制部400重新排列从外部(例如,图像处理器)提供的输入数据data1而生成帧数据(或者,第二数据data2)。根据一实施例,定时控制部400可以在帧数据中插入时钟训练信号(或者,时钟训练模式)而生成时钟嵌入数据。在此,时钟训练信号在数据驱动部300中用于恢复时钟信号,例如,时钟训练信号可以与时钟信号相同地包括与矩形波(square wave)对应的值。例如,定时控制部400可以将时钟训练信号插入在帧数据和相邻帧数据之间。

54.定时控制部400可以将第二数据data2提供于数据驱动部300。

55.扫描驱动部200以及数据驱动部300可以驱动显示部100。

56.扫描驱动部200可以从定时控制部400接收扫描控制信号gdc的供应,并基于扫描控制信号gdc生成扫描信号以及感应控制信号(或者,感应扫描信号)。扫描驱动部200可以

将扫描信号提供于扫描线sl,并将感应控制信号提供于感应控制线ssl。

57.数据驱动部300从定时控制部400接收数据控制信号ddc以及第二数据data2。数据驱动部300可以基于时钟嵌入数据的时钟训练信号恢复时钟信号,并基于时钟信号从时钟嵌入数据恢复帧数据。

58.另外,在显示部100显示图像的显示时段(或者,帧区间),数据驱动部300可以生成与第二数据data2对应的数据信号,并将数据信号提供于数据线dl。

59.在感应子像素spx的特性信息,例如包括在子像素spx中的驱动晶体管的阈值电压及/或迁移率等的感应时段中的第一感应时段,数据驱动部300可以通过缓冲放大器部(未图示)向子像素spx提供第一感应电压,并通过感应线rl从子像素spx中的至少一个像素接收与第一感应电压对应的第一感应信号。

60.例如,感应时段可以是相邻的显示时段(例如,不同帧区间)之间的垂直空白区间(或者,垂直边沿区间)。在感应时段期间,数据驱动部300可以从子像素spx接收感应信号(例如,驱动晶体管的迁移率,或者关于其的信号)。作为另一例,可以是,感应时段是显示装置10即将电源断开前的区间,数据驱动部300从包括子像素spx的像素以像素行为单位依次接收感应信号(例如,各个像素的驱动晶体管的阈值电压)。

61.格劳保放大器ga可以与位于显示部100和数据驱动部300之间的数据线dl接通。根据一实施例,格劳保放大器ga的输出端可以与多个数据线dl通过开关sw连接,并在与第一感应时段不同的第二感应时段,通过数据线dl向子像素spx提供第二感应电压。在此情况下,数据驱动部300可以通过感应线rl从子像素spx中的至少一个像素接收与第二感应电压对应的第二感应信号。

62.另一方面,定时控制部400可以从数据驱动部300接收根据外部补偿工作的补偿数据sd的提供。定时控制部400可以基于补偿数据sd校正第一数据data1而生成第二数据data2,以便补偿像素pxl间驱动晶体管的劣化偏差及/或像素pxl间发光元件的劣化偏差。定时控制部400可以将在用于图像显示的显示时段中被校正的第二数据data2向数据驱动部300传输。

63.补偿数据sd可以基于第一感应信号以及第二感应信号而生成。关于计算第一感应信号以及第二感应信号的具体方法,参照下面图3至图6b详细后述。

64.图2是示出包括在图1的显示装置中的子像素的一例的电路图。在图2中例示性示出包括在第n个像素行以及第k个像素列中的子像素spx(其中,n、k是正的整数)。

65.参照图2,子像素spx可以与第n扫描线sln、第k数据线dlk、第n感应控制线ssln以及第k感应线rlk连接。

66.子像素spx可以包括发光元件led、第一晶体管(驱动晶体管)t1、第二晶体管(开关晶体管)t2、第三晶体管(感应晶体管)t3以及存储电容器cst。

67.可以是,发光元件led的阳极电极与第二节点n2(或者,第一晶体管t1的第二电极)接通,阴极电极与被施加有第二电源电压vss的第二电源线pl2接通。发光元件led可以对应于从第一晶体管t1供应的电流量(或者,驱动电流)而生成预定亮度的光。发光元件led可以是有机发光二极管,但不限于此,也可以包括无机发光二极管。

68.另外,发光元件led也可以是混合包含有机物和无机物的元件。追加性地,虽然在图2中示出为子像素spx包括单个(single)发光元件led,但在其它实施例中,可以是,子像

素spx包括多个发光元件led,多个发光元件led彼此以串联、并联或者串并联接通。

69.可以是,第一晶体管t1的第一电极与被施加第一电源电压vdd的第一电源线pl1接通,第二电极与第二节点n2(或者,发光元件led的阳极电极)接通。第一晶体管t1的栅极电极可以与第一节点n1接通。第一晶体管t1对应于第一节点n1的电压来控制向发光元件led流动的电流量。

70.可以是,第二晶体管t2的第一电极与第k数据线dlk接通,第二电极与第一节点n1接通。第二晶体管t2的栅极电极可以与第n扫描线sln接通。当向第n扫描线sln供应扫描信号s[n]时,第二晶体管t2可以导通而将来自第k数据线dlk的数据电压vdata(或者,数据信号)向第一节点n1传递。此时,可以是,在第一感应时段期间,从缓冲放大器bf(参照图3)作为数据电压vdata输出第一感应电压,在第二感应时段期间,从格劳保放大器ga(参照图1)作为数据电压vdata输出第二感应电压。

[0071]

存储电容器cst可以接通在第一节点n1和发光元件led的阳极电极之间。存储电容器cst可以存储第一节点n1的电压。

[0072]

第三晶体管t3可以接通在第k感应线rlk和第二节点n2(或者,第一晶体管t1的第二电极)之间。第三晶体管t3的栅极电极可以与第n感应控制线ssln接通。当向第n感应控制线ssln供应感应控制信号sen[n]时,第三晶体管t3导通而第k感应线rlk和第二节点n2电连接。

[0073]

根据一实施例,可以与扫描信号s[n]同时施加感应控制信号sen[n]。在第一感应时段以及第二感应时段中的至少一部分时段期间,第二晶体管t2以及第三晶体管t3可以保持导通状态。第三晶体管t3可以响应于感应控制信号sen[n]而连接第二节点n2和第k感应线rlk。在此情况下,感应信号可以向第k感应线rlk提供。在此,感应信号可以设定为施加于第二节点n2的感应电压及/或向第二节点n2供应的感应电流。

[0074]

感应信号可以通过第k感应线rlk向数据驱动部300(参照图1)提供。

[0075]

在感应时段中,根据第一晶体管t1的栅源电压,子像素spx(或者,发光元件led)可能发光。尤其,在感应时段对应于在图1中说明的垂直空白区间的情况下,子像素spx可能在垂直空白区间以不希望的亮度发光。

[0076]

因此,显示装置10(参照图1)通过改变第二电源电压vss,例如提高第二电源电压vss的电压电平,从而可以抑制子像素spx的发光。但是,不限于此。

[0077]

另一方面,在本发明的实施例中,子像素spx不限于图2中示出的电路结构。作为一例,虽然在图2中第一晶体管t1、第二晶体管t2以及第三晶体管t3各自示出为n型晶体管,但是第一晶体管t1、第二晶体管t2以及第三晶体管t3中的至少一个可以以p型晶体管形成。

[0078]

图3是用于说明感应时段期间像素、数据驱动部以及格劳保放大器间的工作的图。此时,数据驱动部300可以包括一个以上的源极驱动ic(intergrated circuit;未图示)。在图3中,为了便于说明,假设源极驱动ic为一个而进行说明。

[0079]

参照图3,数据驱动部300可以包括信号输出部310以及感应部320。此时,感应部320是用于指称多个感应部su的附图标记,以下,指称为感应部su。

[0080]

根据本发明的一实施例,感应部su可以在第一感应时段期间对应于由缓冲放大器bf输出的第一感应电压,从像素pxl1、pxl2接收第一感应信号。另外,感应部su可以在第二感应时段期间对应于由格劳保放大器ga输出的第二感应电压,从像素pxl1、pxl2接收第二

感应信号。接收第一感应信号以及第二感应信号的感应部su可以基于第一感应信号以及第二感应信号的差值生成补偿数据sd。此时,第一感应时段以及第二感应时段只是用于区分输入到像素pxl1、pxl2的感应电压的不同,并不是用来定义时间的先后关系。即,第二感应时段可以比第一感应时段提前。

[0081]

第一像素pxl1可以包括与第一数据线dl1连接的第一子像素spx1、与第二数据线dl2连接的第二子像素spx2以及与第三数据线dl3连接的第三子像素spx3。另外,第二像素pxl2可以包括与第四数据线dl4连接的第一子像素spx1、与第五数据线dl5连接的第二子像素spx2以及与第六数据线dl6连接的第三子像素spx3。例如,可以是,第一子像素spx1是发出红光的红色像素,第二子像素spx2是发出绿光的绿色像素,第三子像素spx3是发出蓝光的蓝色像素。但是,像素pxl1、pxl2的结构不限于此。例如,像素pxl1、pxl2可以还包括发出白光的子像素。

[0082]

第一子像素spx1、第二子像素spx2以及第三子像素spx3可以与多个感应线中的一个感应线接通。根据一实施例,可以是,包括在第一像素pxl1中的第一子像素spx1、第二子像素spx2以及第三子像素spx3连接于一个感应线,即第一感应线rl1,包括在第二像素pxl2中的第一子像素spx1、第二子像素spx2以及第三子像素spx3连接于第二感应线rl2。即,构成相同的像素pxl1、pxl2的多个子像素spx1、spx2、spx3可以与彼此不同的感应线rl1、rl2独立连接。

[0083]

格劳保放大器ga的输出端可以通过第一开关sw1与第一数据线dl1连接,通过第二开关sw2与第二数据线dl2连接,通过第三开关sw3与第三数据线dl3连接。另外,格劳保放大器ga的输出端可以通过第一开关sw1与第四数据线dl4连接,通过第二开关sw2与第五数据线dl5连接,通过第三开关sw3与第六数据线dl6连接。根据本发明的一实施例,可以是,连接于第一子像素spx1的第一开关sw1同时执行开闭工作,连接于第二子像素spx2的第二开关sw2同时执行开闭工作,连接于第三子像素spx3的第三开关sw3同时执行开闭工作。

[0084]

感应部su可以对应于在第一感应时段期间由缓冲放大器bf输出的第一感应电压,从像素pxl1、pxl2接收第一感应信号。此时,第一开关sw1、第二开关sw2以及第三开关sw3全部可以在第一感应时段期间断开。即,在第一感应时段期间,第一开关sw1、第二开关sw2以及第三开关sw3全部处于开路状态,因此从格劳保放大器ga接收不到任何信号。

[0085]

感应部su可以对应于在第二感应时段期间由格劳保放大器ga输出的第二感应电压,从像素pxl1、pxl2接收第二感应信号。

[0086]

根据本发明的一实施例,可以以连接于相同像素行的第一子像素spx1、第二子像素spx2以及第三子像素spx3的顺序依次接收第二感应信号。

[0087]

例如,可以是,在第二感应时段期间,第一开关sw1导通(或者,闭路状态),第二开关sw2以及第三开关sw3断开(或者,开路状态)。此时,与第一数据线dl1连接的第一缓冲放大器bf1处于高阻抗(hi-z)状态,与第二数据线dl2连接的第二缓冲放大器bf以及与第三数据线dl3连接的第三缓冲放大器bf可以输出对应于最低灰度的数据电压(或者,黑色数据)。第一缓冲放大器b1f处于高阻抗(hi-z)状态,实质上是开路状态,因此仅能输入通过第一数据线dl1从格劳保放大器ga输出的第二感应电压。

[0088]

其次,可以是,在第二感应时段期间,第二开关sw2导通(或者,闭路状态),第一开关sw1以及第三开关sw3断开(或者,开路状态)。此时,与第二数据线dl2连接的第二缓冲放

大器bf处于高阻抗(hi-z)状态,与第一数据线dl1连接的第一缓冲放大器bf1以及与第三数据线dl3连接的第三缓冲放大器bf可以输出对应于最低灰度的数据电压(或者,黑色数据)。第二缓冲放大器bf处于高阻抗(hi-z)状态,实质上是开路状态,因此仅能输入通过第二数据线dl2从格劳保放大器ga输出的第二感应电压。

[0089]

之后,可以是,在第二感应时段期间,第三开关sw3导通(或者,闭路状态),第一开关sw1以及第二开关sw2断开(或者,开路状态)。与第三数据线dl3连接的第三缓冲放大器bf处于高阻抗(hi-z)状态,与第一数据线dl1连接的第一缓冲放大器bf1以及与第二数据线dl2连接的第二缓冲放大器bf可以输出对应于最低灰度的数据电压(或者,黑色数据)。第三缓冲放大器bf处于高阻抗(hi-z)状态,实质上是开路状态,因此仅能输入通过第三数据线dl3从格劳保放大器ga输出的第二感应电压。

[0090]

另一方面,可以还包括与连接于格劳保放大器ga的输出端的第一电极以及基准电源(或者,接地电压)连接的电源稳定化电容器c。电源稳定化电容器c可以保持格劳保放大器ga的输出端的电压。

[0091]

图4是具体示出根据本发明的一实施例的图3的数据驱动部的信号输出部的电路图。

[0092]

参照图4,信号输出部310可以具备移位寄存器部311、采样锁存部312、保持锁存部313、解码器314以及缓冲放大器部bf。

[0093]

移位寄存器部311可以响应于从定时控制部400输出的源起始脉冲ssp以及源移位时钟ssc而依次生成m(m是比0大的自然数)个采样信号。具体地,移位寄存器部311可以在源移位时钟ssc的每1周期移位源起始脉冲ssp的同时依次生成m个采样信号。移位寄存器部311可以实现m个移位寄存器3111~311m。

[0094]

采样锁存部312可以响应于从移位寄存器部311依次供应的采样信号而依次存储第二数据data2。采样锁存部312可以由用于存储m个第二数据data2的m个采样锁存3121~312m来实现。

[0095]

保持锁存部313可以响应于从定时控制部400输出的源输出使能soe信号而存储从采样锁存部312供应的第二数据data2。保持锁存部313可以将存储在自体中的第二数据data2向解码器314供应。保持锁存部313可以由m个保持锁存3131~313m来实现。

[0096]

解码器314可以将从保持锁存部313输出的第二数据data2转换成模拟信号,并将转换的模拟信号作为数据信号向缓冲放大器部bf输出。解码器314可以基于从保持锁存部313输出的第二数据data2,从最小灰度伽马电压vgal以及最大灰度伽马电压vgah中选择多个灰度电压。解码器314可以具备m个数模转换器(digital-analog converters)3141~314m。即,解码器314可以利用配置于每个沟道的数模转换器3141~314m而生成m个数据信号,并将生成的数据信号向缓冲放大器部bf供应。

[0097]

缓冲放大器部bf可以将从解码器314供应的m个数据信号向m个数据线dl1~dlm供应。缓冲放大器部bf可以由m个缓冲放大器bf1~bfm来实现。

[0098]

图5是示出本发明的一实施例的图3的感应部的电路图。图6a是示出在第一感应时段存储于感应电容器中的感应信号的电压值的波形图。

[0099]

图6b是示出在第二感应时段存储于感应电容器中的感应信号的电压值的波形图。在图5中以通过第k感应线rlk连接于像素pxl而感应像素pxl的特性的数据驱动部300的一

部分为中心简要示出。

[0100]

参照图1、图2、图4以及图5,像素pxl与参照图2来说明的子像素spx实质上相同,并与参照图4来说明的缓冲放大器部bf实质上相同,因此重复的说明将不予以反复。

[0101]

根据本发明的一实施例,可以是,缓冲放大器部bf在感应子像素spx的特性信息的感应时段中的第一感应时段,通过数据线dl向子像素spx提供第一感应电压,感应部su通过感应线rl从子像素spx中的至少一个像素接收与第一感应电压对应的第一感应信号。

[0102]

另外,可以是,格劳保放大器ga在第二感应时段,通过数据线dl向子像素spx提供第二感应电压,感应部su通过感应线rl从子像素spx中的至少一个像素接收与第二感应电压对应的第二感应信号。

[0103]

数据驱动部300可以包括缓冲放大器部bf以及感应部su。

[0104]

缓冲放大器部bf可以从解码器314的数模转换器3141~314m(参照图4)接收与包括在帧数据(或者,第二数据data2)中的数据值(或者,灰度数据)对应的数据电压。缓冲放大器部bf可以向第k数据线dlk提供数据电压。

[0105]

感应部su可以包括感应电容器csen、第一电容器c1、第二电容器c2、初始化开关sw_vinit、采样开关sw_spl、共享开关sw_share、复位开关sw_rst、输出开关sw_ch以及补偿数据计算部sdg。

[0106]

初始化开关sw_vinit可以连接在被施加初始化电压vinit的电源线和第k感应线rlk之间。在此,初始化电压vinit可以从另外的电源供应部提供,并具有比发光元件led的工作点低的电压电平。可以是,当初始化开关sw_vinit导通时,初始化电压vinit施加于第k感应线rlk,另外,当子像素spx的第三晶体管t3导通时,初始化电压vinit施加于子像素spx的第二节点n2。初始化电压vinit具有比发光元件led的工作点低的电压电平,因此即使第一晶体管t1导通,发光元件led也可以不发光。

[0107]

感应电容器csen可以连接在第k感应线rlk和基准电源之间。基准电源可以具有接地电压,但不限于此。当初始化开关sw_vinit断开且子像素spx的第三晶体管t3导通时,可以利用通过第二节点n2提供的电流对感应电容器csen进行充电。即,在感应电容器csen中可以存储通过第二节点n2提供的子像素spx的特性信息。

[0108]

参照图6a,在第一感应时段,存储在感应电容器csen的两端中的电压vsen1(或者,第一感应信号的电压)可以是从第一感应电压v1减去第一晶体管t1(或者,驱动晶体管)的阈值电压δvth以及缓冲放大器部bf的电压偏差δvdv的值。此时,缓冲放大器部bf的电压偏差δvdv可以意指因多个缓冲放大器bf1~bfm的配置上差异而产生的电压的偏差。例如,多个缓冲放大器bf1~bfm由于制造时工艺上的原因,在增益(gain)上可能存在差异,由此缓冲放大器bf1~bfm的输出电压可能增加或减少。

[0109]

另一方面,参照图6b,在第二感应时段,存储在感应电容器csen的两端中的电压vsen2(或者,第二感应信号的电压)可以是从第二感应电压v2减去第一晶体管t1(或者,驱动晶体管)的阈值电压δvth的值。当通过一个格劳保放大器ga将具有相同电平的第二感应电压向多个子像素spx供应时,与通过多个缓冲放大器bf1~bfm供应第一感应电压的情况不同,可以不产生电压的偏差。

[0110]

第一感应电压v1可以具有与第二感应电压v2相同的值。例如,缓冲放大器部bf和格劳保放大器ga可以接收从图4中示出的相同的解码器314中输出的相同的模拟信号。

[0111]

在第一感应电压v1和第二感应电压v2的大小相同的情况下,在第二感应时段存储在感应电容器csen的两端中的电压(或者,第二感应信号的电压)可以比在第一感应时段存储在感应电容器csen的两端中的电压(或者,第一感应信号的电压)大。

[0112]

采样开关sw_spl可以连接在第k感应线rlk和第三节点n3之间。第一电容器c1可以连接在第三节点n3和基准电源之间。在采样开关sw_spl导通的期间,第一电容器c1可以采样存储在感应电容器csen中的子像素spx(或者,第一晶体管t1)的特性信息。即,数据驱动部300可以通过采样开关sw_spl以及第一电容器c1采样感应信号。

[0113]

可以是,共享开关sw_share连接在第三节点n3和第四节点n4之间,复位开关sw_rst连接在第四节点n4和基准电源之间,第二电容器c2连接在第四节点n4和基准电源之间。若共享开关sw_share导通,第一电容器c1以及第二电容器c2共享电荷,则第四节点n4的节点电压(以及第三节点n3的节点电压)可以变动。根据共享开关sw_share以及复位开关sw_rst的工作,共享开关sw_share、复位开关sw_rst以及第二电容器c2可以作为缓冲器发挥功能。在此,虽然根据第一电容器c1以及第二电容器c2的静电容量比率而不同,但缓冲器的增益可以是n(其中,n是比1大的整数)。即,共享开关sw_share、复位开关sw_rst以及第二电容器c2可以放大第三节点n3的节点电压。

[0114]

补偿数据计算部sdg可以连接在第四节点n4和输出开关sw_ch之间,并在第一感应时段接收存储在感应电容器csen的两端中的电压(或者,第一感应信号的电压),在第二感应时段接收存储在感应电容器csen的两端中的电压(或者,第二感应信号电压)。补偿数据计算部sdg可以计算所接收的第一感应信号的电压和第二感应信号的电压的差值。

[0115]

输出开关sw_ch可以连接在补偿数据计算部sdg的输出端和模数转换器adc之间,并将补偿数据计算部sdg的输出端与模数转换器adc的输入端连接。在此情况下,第一感应信号的电压和第二感应信号的电压的差值可以施加于模数转换器adc。

[0116]

虽然未图示,也可以还包括连接在模数转换器adc的输入端和基准电源之间而保持向模数转换器adc提供的第四节点n4的节点电压的电容器以及初始化模数转换器adc的输入端(或者,电容器)的初始化电路(例如,电容器初始化电源以及将其与模数转换器adc的输入端连接的开关)。

[0117]

模数转换器adc可以将提供于输入端的电压转换成数据值(例如,数字代码)。即,数据驱动部300可以通过模数转换器adc将采样的感应信号从模拟形式转换成数字形式。数字形式的感应信号(或者,补偿数据sd)可以向定时控制部400提供。

[0118]

另一方面,虽然在图5中示出为感应部su包括电容器csen、c1、c2以及开关sw_vinit、sw_spl、sw_share、sw_rst、sw_ch来构成,但其是例示性的,并不限于此。例如,只要感应部su能够检测出子像素spx的第二节点n2的节点电压(或者,对应于其的电流),作为感应部su可以适用各种电路(例如,利用放大器将感应电流转换成感应电压,并采样以及保持被转换的感应电压的感应电路)。

[0119]

根据本发明的实施例,利用一个格劳保放大器ga,可以仅计算与包括在显示部100中的多个像素pxl的阈值电压δvth相关的信息,因此可以单独管理与多个像素pxl的阈值电压δvth相关的信息和与数据驱动部300的缓冲放大器bf的电压偏差δvdv相关的信息。因此,能够分别执行针对多个像素pxl的阈值电压δvth的补偿以及针对数据驱动部300的缓冲放大器bf的电压偏差δvdv的补偿。由此,能够使感应沟道间偏差减小,因此能够针对

显示装置10执行更准确的补偿。

[0120]

图7是示出根据本发明的一实施例的显示装置的驱动方法的流程图。图8示出根据本发明的一实施例的定时控制部的接口信号的信号图。

[0121]

首先,参照图1以及图8,定时控制部400可以将时钟嵌入数据向数据驱动部300提供。定时控制部400可以利用串联接口(或者,高速串联接口)将时钟嵌入数据以数据包形式向数据驱动部300传送。

[0122]

定时控制部400可以对应于垂直同步信号vsync的周期将帧转换。此时,“h”意指一个水平时段的起点,“hbp”意指一个水平时段的终点。可以是,“像素数据”包括在显示时段关于第二数据data2的信息,“帧协议”包括决定在感应时段是否利用缓冲放大器bf来执行感应或者利用格劳保放大器ga来执行感应的信息。“h协议”可以包括与显示装置10是否以显示模式工作还是以感应模式工作有关的信息。

[0123]

在时钟训练时段期间,定时控制部400可以向帧数据插入时钟训练信号(或者,时钟训练模式)而生成时钟嵌入数据。

[0124]

感应时段可以是相邻的显示时段(例如,不同帧区间)之间的垂直空白区间(或者,垂直同步信号的低电平区间)。在感应时段期间,数据驱动部300可以从像素pxl接收感应信号(例如,驱动晶体管的迁移率,或者关于其的信号)。作为另一例,可以是,感应时段是显示装置10即将电源关闭之前的区间,数据驱动部300从包括子像素spx的像素以像素行为单位依次接收感应信号(例如,各个像素的驱动晶体管的阈值电压)。

[0125]

以下,为了便于说明,参照图1至图7,假设在相邻的显示时段(例如,不同帧区间)之间的垂直空白区间(或者,垂直同步信号的低电平区间)执行感应模式而进行说明。

[0126]

具备包括与数据线dl以及感应线rl连接的多个像素pxl的显示部100的显示装置10的驱动方法首先在数据驱动部300中通过多个缓冲放大器bf在第一感应时段期间向数据线dl供应第一感应电压v1(s10)。

[0127]

第一像素pxl1可以包括与第一数据线dl1连接的第一子像素spx1、与第二数据线dl2连接的第二子像素spx2以及与第三数据线dl3连接的第三子像素spx3。

[0128]

第一子像素spx1、第二子像素spx2以及第三子像素spx3可以与多个感应线中的一个感应线接通。

[0129]

格劳保放大器ga的输出端可以通过第一开关sw1与第一数据线dl1连接,并通过第二开关sw2与第二数据线dl2连接,并且通过第三开关sw3与第三数据线dl3连接。

[0130]

在第一感应时段期间,可以从缓冲放大器bf作为数据电压vdata输出第一感应电压v1。在第一感应时段,可以是,第二晶体管t2响应于扫描信号s[n]而导通,第三晶体管t3响应于感应控制信号sen[n]而导通。此时,在第一感应时段,根据像素pxl的第一晶体管t1的栅源电压,像素pxl(或者,发光元件led)可能发光。尤其,在感应时段对应于在图1中说明的垂直空白区间的情况下,像素pxl可能在垂直空白区间以不希望的亮度发光。

[0131]

因此,显示装置10通过在第一感应时段期间改变第二电源电压vss,例如提高第二电源电压vss的电压电平,从而可以抑制像素pxl的发光。

[0132]

之后,在数据驱动部300中,由感应部su在第一感应时段期间通过感应线rl从像素pxl接收第一感应信号(s20)。

[0133]

感应部su可以在第一感应时段期间,对应于由缓冲放大器bf输出的第一感应电压

v1,从像素pxl1、pxl2接收第一感应信号。此时,第一开关sw1、第二开关sw2以及第三开关sw3全部可以在第一感应时段期间断开。即,在第一感应时段期间,第一开关sw1、第二开关sw2以及第三开关sw3全部处于开路状态,因此从格劳保放大器ga接收不到任何信号。

[0134]

其次,从格劳保放大器ga在与第一感应时段不同的第二感应时段期间向数据线dl供应第二感应电压v2(s30)。

[0135]

参照图3,在第二感应时段期间,可以从格劳保放大器ga作为数据电压vdata输出第二感应电压v2。在第二感应时段,可以是,第二晶体管t2响应于扫描信号s[n]而导通,第三晶体管t3响应于感应控制信号sen[n]而导通。此时,显示装置10通过在第二感应时段期间改变第二电源电压vss,例如提高第二电源电压vss的电压电平,从而可以抑制像素pxl的发光。

[0136]

供应第二感应电压v2的步骤可以包括:在第二感应时段期间,第一开关sw1导通,第二开关sw2以及第三开关sw3断开,与第一数据线dl1连接的第一缓冲放大器bf1处于高阻抗(hi-z)状态,通过与第二数据线dl2连接的第二缓冲放大器bf2以及与第三数据线dl3连接的第三缓冲放大器bf3输出对应于最低灰度的数据电压的步骤;在第二感应时段期间,第二开关sw2导通,第一开关sw1以及第三开关sw3断开,第二缓冲放大器bf2处于高阻抗(hi-z)状态,通过第一缓冲放大器bf1以及第三缓冲放大器bf3输出对应于最低灰度的数据电压的步骤;以及在第二感应时段期间,第三开关sw3导通,第一开关sw1以及第二开关sw2断开,第三缓冲放大器bf3处于高阻抗(hi-z)状态,通过第一缓冲放大器bf1以及第二缓冲放大器bf2输出对应于最低灰度的数据电压。

[0137]

之后,在数据驱动部300中,由感应部su在第二感应时段期间通过感应线rl从像素pxl接收对应于第二感应电压v2的第二感应信号(s40)。感应部su可以在第二感应时段期间,对应于由格劳保放大器ga输出的第二感应电压v2,从像素pxl1、pxl2接收第二感应信号。

[0138]

此时,第一感应时段以及第二感应时段只是用于区分输入到像素pxl1、pxl2的感应电压的不同,并不是用来定义时间的先后关系。即,第二感应时段可以比第一感应时段提前。

[0139]

其次,在数据驱动部300中,由感应部su基于第一感应信号以及第二感应信号的差值生成补偿数据(s50)。

[0140]

感应部su的感应电容器csen可以在第一感应时段期间,存储与第一感应电压v1对应的第一感应信号的电压,并在第二感应时段期间,存储与第二感应电压v2对应的第二感应信号的电压。

[0141]

在第一感应时段,存储在感应电容器csen的两端中的电压vsen1(或者,第一感应信号的电压)可以是从第一感应电压v1减去第一晶体管t1(或者,驱动晶体管)的阈值电压δvth以及缓冲放大器部bf的电压偏差δvdv的值。

[0142]

在第二感应时段,存储在感应电容器csen的两端中的电压vsen2(或者,第二感应信号的电压)可以是从第二感应电压v2减去第一晶体管t1(或者,驱动晶体管)的阈值电压δvth的值。

[0143]

此时,第一感应电压v1可以具有与第二感应电压v2相同的值。例如,缓冲放大器部bf和格劳保放大器ga可以接收从图4中示出的相同的解码器314输出的相同的模拟信号。

[0144]

在第一感应电压v1和第二感应电压v2的大小相同的情况下,在第二感应时段存储在感应电容器csen的两端中的电压(或者,第二感应信号的电压)可以比在第一感应时段存储在感应电容器csen的两端中的电压(或者,第一感应信号的电压)大。

[0145]

补偿数据计算部sdg可以连接在第四节点n4和输出开关sw_ch之间,并在第一感应时段接收存储在感应电容器csen的两端中的电压(或者,第一感应信号的电压),在第二感应时段接收存储在感应电容器csen的两端中的电压(或者,第二感应信号的电压)。补偿数据计算部sdg可以计算所接收的第一感应信号的电压和第二感应信号的电压的差值。

[0146]

模数转换器adc可以将第一感应信号的电压和第二感应信号的电压的差值转换成数据值(例如,数字代码)。即,数据驱动部300可以通过模数转换器adc将采样的感应信号从模拟形式转换成数字形式。数字形式的感应信号(或者,补偿数据sd)可以向定时控制部400提供。

[0147]

定时控制部400可以从数据驱动部300接收基于外部补偿工作的补偿数据sd的提供。定时控制部400可以基于补偿数据sd校正第一数据data1而补偿像素pxl间驱动晶体管的劣化偏差,或者补偿像素pxl间有机发光二极管的劣化偏差。定时控制部400可以将用于图像显示的在显示时段被校正的第二数据data2向数据驱动部300传送。

[0148]

根据本发明的实施例,利用一个格劳保放大器ga,可以仅计算与包括在显示部100中的多个像素pxl的阈值电压δvth相关的信息,因此可以单独管理与多个像素pxl的阈值电压δvth相关的信息和与数据驱动部300的缓冲放大器bf的电压偏差δvdv相关的信息。因此,能够分别执行针对多个像素pxl的阈值电压δvth的补偿以及针对数据驱动部300的缓冲放大器bf的电压偏差δvdv的补偿。由此,能够使感应沟道间偏差减小,因此能够针对显示装置10执行更准确的补偿。

[0149]

以上,参照本发明的实施例进行了说明,但是本技术领域的熟练的人员可以理解能够在不脱离权利要求书中记载的本发明的构思以及领域的范围内对本发明进行各种修改及变更。