1.本公开涉及一种转换速率增强(slew rate enhancement,sre)电路,且更具体来说,涉及一种改善缓冲电路的转换速率的电路。

背景技术:

2.在显示面板系统中,常常需要面板系统的源极驱动器以低功耗实现高驱动能力。由于转换速率限制了源极驱动器中的缓冲电路对输入信号的突变作出响应的能力,因此增强缓冲电路的转换速率是理想的。同样,传统的sre电路将判断面板系统是否被接通且产生增强的电流,以通过面板系统的阈值电压(threshold voltage,vht)增强转换速率。由于产生增强的电流的传统方法是通过sre电路中的金属氧化物半导体场效晶体管(metal

–

oxide

–

semiconductor field-effect transistor,mosfet)的跨导能力且增强的电流本质上是呈指数分布,因此增强的电流难以控制。由于sre电路中的mosfet易受工艺、电压及温度(process,voltage and temperature,pvt)变化的影响,因此所产生的增强的电流变得更加不可预测且不受控制。

3.不受控制的增强的电流将导致缓冲电路操作异常并生成异常输出波形,且缓冲电路进入线性区,此使得sre无效。过多的电流增强导致功耗增大且电磁干扰(electromagnetic interference,emi)问题增多,此使得传统的sre电路不可预测且难以设计。另外,传统上使用不同的器件检测输出波形的上升沿及下降沿,来自传统的sre电路的输出波形的上升沿及下降沿可发生变化且输出波形可为不对称的。随着显示面板分辨率提高及充电时间缩短,波形的上升沿与下降沿之间的对称性变得更加重要。如果波形变得不对称,则面板系统的电流恢复率将大大降低,从而导致过多的功耗以及非理想的emi及触摸面板(touch panel,tp)噪声。

4.因此,需要一种能够线性地增强及设定不会随着pvt的变化而发生变化的转换速率的电路及方法,以独立地增强输出波形的上升沿及下降沿,使得可解决输出波形对称性且使转换速率随着功率模式的切换而发生变化。

技术实现要素:

5.本公开涉及一种转换速率增强(sre)电路,且更具体来说,涉及一种改善缓冲电路的转换速率的电路。

6.本公开提供一种转换速率增强装置,所述转换速率增强装置连接到运算放大器,所述运算放大器接收输入信号并根据所述输入信号产生输出信号以用于驱动像素。所述转换速率增强装置包括信号边沿检测器、比较器、调整单元。所述信号边沿检测器耦合到所述运算放大器,且被配置成检测信号边沿且输出与所述输入信号和所述输出信号之间的差值对应的差值信号。所述比较器耦合到所述信号边沿检测器,以接收所述差值信号且被配置成根据所述差值信号产生控制信号。所述调整单元耦合到所述比较器以接收所述控制信号,且被配置成根据所述控制信号将由电流源产生的补偿信号耦合到所述运算放大器以增

强所述运算放大器的转换速率。

7.本公开提供一种具有转换速率增强的显示面板。所述显示面板包括控制器、显示面板、栅极驱动电路及源极驱动电路。所述控制器接收显示数据,以显示图像。所述显示面板包括多条源极线、多条栅极线及位于所述源极线与所述栅极线的交叉部位处的多个像素。所述栅极驱动电路耦合到所述栅极线中的每一者。所述源极驱动电路被配置成根据所述显示数据驱动所述显示面板,所述源极驱动电路包括多个运算放大器、转换速率增强电路。所述多个运算放大器分别耦合到所述源极线。所述运算放大器中的每一者被配置成接收输入信号并根据所述输入信号产生输出信号,以用于驱动连接到对应的所述源极线的所述像素。所述转换速率增强电路被配置成将电源耦合到所述运算放大器中的至少一者,以增强所述运算放大器中的所述至少一者的转换速率。

8.为使上述内容更容易理解,以下将详细阐述随附有图式的若干实施例。

附图说明

9.本公开包括附图以提供对本公开的进一步理解,且附图并入本说明书中并构成本说明书的一部分。图式示出本公开的实施例且与说明一同用于阐释本公开的原理。

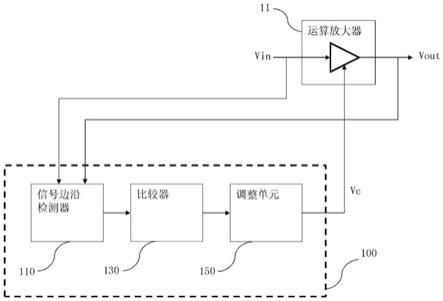

10.图1是示出根据本公开实施例中的一个实施例的具有转换速率增强(sre)电路的运算放大器11的方块图。

11.图2是示出根据本公开实施例中的一个实施例的显示器件的方块图。

12.图3是示出根据本公开实施例中的一个实施例的sre电路的示意图。

13.图4是示出根据本公开实施例中的一个实施例的sre电路的示意图。

14.图5是示出根据本公开实施例中的一个实施例的运算放大器的示意图。

15.图6是示出根据本公开实施例中的一个实施例的运算放大器的示意图。

16.图7是示出根据本公开实施例中的一个实施例的具有全局调整单元的sre电路的示意图。

17.图8示出根据本公开实施例的sre电路的方块图。

具体实施方式

18.以下公开提供用于实施本公开的不同特征的许多不同示例性实施例或实例。应理解,在不背离本公开的范围的条件下可利用其他实施例且可作出结构改变。另外,应理解,本文中所使用的措词及术语是出于说明的目的而不应被视为进行限制。在本文中使用“包括(including)”、“包含(comprising)”或“具有(having)”及其变型意在囊括在其后所列出的项及其等效形式以及附加项。除非另有限制,否则在本文中广泛使用用语“连接”、“耦合”及“安装”及其变型,且囊括直接连接、直接耦合及直接安装以及间接连接、间接耦合及间接安装。除非上下文清楚地另外指明,否则本文中所使用的单数形式“一(a及an)”及“所述(the)”也旨在包括复数形式。在说明书通篇及图式中,相同的编号可指代相同的元件。另外,本公开可能在各种实例中重复使用参考编号和/或字母。这种重复使用是出于简洁及清晰的目的,而不是自身指示所论述的各种实施例和/或配置之间的关系。

19.在本公开的实施例中,转换速率增强装置根据输入信号与输出信号之间的差值产生控制信号。控制信号用于分别控制多个电流源的切换,从而分别控制输出波形的上升沿

及下降沿。以此种方式,所产生的增强的电流不会受到pvt变化的影响。通过数字控制用于产生增强的电流的电流源,可分别地且线性地增强输出波形的上升沿及下降沿,且可针对不同的功率模式灵活地调整增强的电流。

20.图1是示出根据本公开实施例中的一个实施例的具有转换速率增强(sre)电路100的运算放大器11的方块图。在实施例中,运算放大器11可为用于驱动显示面板的源极驱动器的缓冲电路。运算放大器11可表示多个运算放大器,其中运算放大器中的每一者电连接到显示面板的数据线。作为另外一种选择,运算放大器11可表示电连接到显示面板的数据线(也可被称为通道)的一个运算放大器11。参照图1,输入信号vin耦合到运算放大器11的输入。在实施例中,输入信号vin可为表示像素数据的电压或电流,且可从源极驱动电路的数模转换器(digital-to-analog converter,dac)接收输入信号vin。从运算放大器11输出的输出信号vout电连接到显示面板的数据线,输出信号vout可为电压或电流。

21.在实施例中,sre电路100电耦合到运算放大器11,以用于增强运算放大器11的转换速率。详细来说,运算放大器11的输入信号vin及输出信号vout耦合到sre电路100作为回馈,且sre电路100的输出耦合到运算放大器11。sre电路100基于运算放大器11的输入信号vin及输出信号vout产生补偿信号vc(其可为电压或电流),从而增强输出信号vout的转换速率。

22.参照图1,sre电路100包括信号边沿检测器110、比较器130及调整单元150。信号边沿检测器110接收运算放大器11的输入信号vin及输出信号vout。信号边沿检测器110检测输入信号vin及输出信号vout的上升沿及下降沿。由于运算放大器11的输出响应于接收到输入信号vin而花费时间进行充电,因此运算放大器11的输出信号vout将缓慢攀升到运算放大器11的输出处的期望电压电平(即,转换速率),此会导致运算放大器11的输出处的状态之间的转变(例如,低状态与高状态之间的转变)发生转变延迟。因此,每当输入信号vin的状态(低或高)发生改变时,信号边沿检测器110将检测输入信号vin与输出信号vout之间的差值或改变。响应于输入信号vin与输出信号vout之间的差值,信号边沿检测器110输出边沿检测信号。在实施例中,输入信号vin与输出信号vout之间的差值可由差值信号idiff表示,稍后将对差值信号idiff进行详细阐述。比较器130从信号边沿检测器110接收信号边沿检测信号,且输出用于启动调整单元150的控制信号。调整单元150耦合到供电电压(例如,vdd或vss)及运算放大器11。当从比较器130接收到控制信号时,调整单元150通过将运算放大器耦合到供电电压来增强运算放大器11,以使运算放大器11的输出可具有更快的响应时间。如上所述,在传统的缓冲电路或源极驱动电路中,通过调整运算放大器的增益(gm)来增强转换速率,转换速率取决于运算放大器的跨导能力。然而,此种传统方法受运算放大器的物理能力(例如,制作运算放大器的过程中的缺陷)及运行环境(例如,温度、电源供应器的电压电平等)的限制。与传统的转换速率增强不同,本公开的转换速率增强电路根据运算放大器11的输入信号vin与输出信号vout之间的差值将电源供应器耦合到运算放大器11。以此种方式,sre电路可精确地且线性地控制运算放大器11的输出(即,线性转换速率增强)。

23.图2是示出根据本公开实施例中的一个实施例的显示器件1的方块图。显示器件1包括源极驱动电路10、栅极驱动电路20、控制器30及显示面板40。

24.控制器30接收红-绿-蓝(red-green-blue,rgb)视频信号r、g及b以及控制信号,例

如垂直同步信号、水平同步信号、主时钟信号及数据使能信号。控制器30可基于控制信号产生源极控制信号及栅极控制信号。因此,控制器30可将栅极控制信号传输到栅极驱动电路20且将源极控制信号及像素数据data(例如r、g、b)传输到源极驱动电路10。

25.源极驱动电路10包括多个源极驱动集成电路(integrated circuit,ic)(未示出)。栅极驱动电路20包括多个栅极驱动集成电路(ic)(未示出)。像素数据data可针对每一像素确定灰度等级。源极驱动电路10可将源极信号施加到排列在显示面板40上的源极线sl1到sln,且栅极驱动电路20可将栅极信号施加到排列在显示面板40上的栅极线gl1到glm。

26.详细来说,源极驱动电路10可包括输出缓冲电路12、数模转换器(dac)13、数据锁存电路14及移位寄存器15。输出缓冲电路12包括多个运算放大器11_1到11_n及转换速率增强(sre)电路100,其中n是正整数。sre电路100被配置成基于输入信号vin与输出信号vout之间的差值产生补偿信号vc。补偿信号vc向运算放大器11_1到11_n提供补偿电流,以减少运算放大器11的输出信号vout的转变时间。因此,输出缓冲电路12的每一输出信号vout可具有短的转变时间及高的转换速率。

27.在实施例中,移位寄存器15基于时钟信号clk及输入/输出控制信号产生脉冲信号。数据锁存电路14可接收像素数据data(例如可从控制器30接收的r、g、b数据)。数据锁存电路14可根据移位寄存器15的移位序列锁存数据并输出数据。数模转换器13产生输入电压信号vin_1到vin_n,输入电压信号vin_1到vin_n是使用灰度电压gma的数据锁存电路14的模拟信号d1到dn。输出缓冲电路12可增强转换速率且对输入电压信号vin_1到vin_n进行缓冲,以产生用于驱动显示面板40的源极信号。显示面板40包括多条源极线sl1到sln、多条栅极线gl1到glm以及排列在源极线与栅极线的每一交叉部位处的多个像素(例如薄膜晶体管(thin film transistor,tft))41_11到41_nm。显示面板40的每一像素41通过栅极线gl1到glm从栅极驱动电路20接收栅极信号(也可被称为扫描信号),且通过源极线sl1到sln从源极驱动电路10接收源极信号(也可被称为数据信号)。栅极驱动电路20可通过根据栅极控制信号对接通电压von与关断电压voff进行组合来生成栅极信号且栅极信号被施加到栅极线gl1到glm。源极驱动电路10根据被施加到数据锁存电路14的数据的序列将源极信号输出到每一源极线sl1到sln。

28.在图2中所示的实施例中,源极驱动电路10可包括多个sre电路100_1到100_n,且运算放大器11_1到11_n中的每一者可由sre电路100_1到100_n中的一者增强。然而,本公开并不仅限于此。在其他实施例中,多个运算放大器(例如,2个、3个、4个等)可共享一个sre电路,以用于转换速率增强。此可被称为用于转换速率增强的全局偏压控制。在图2中所示的实施例中,sre电路100_1到100_n包括在输出缓冲电路12中。然而,本公开并不仅限于此。在替代实施例中,sre电路100_1到100_n可位于输出缓冲电路12外部。

29.在下文中,将详细阐释sre电路100_1到100_n以及运算放大器11_1到11_n的转换速率增强。

30.图3是示出根据本公开实施例中的一个实施例的sre电路100的示意图。参照图3,信号边沿检测器110包括输入/输出信号比较器111、上拉控制电路(pull-up control circuit)113及下推控制电路(push-down control circuit)115。输入/输出信号比较器111将分别从运算放大器11的输入及输出接收的输入信号vin与输出信号vout进行比较。输

入/输出信号比较器111产生与运算放大器11的输入信号vin和输出信号vout之间的差值对应的差值信号idiff,并将差值信号idiff输出到上拉控制电路113及下推控制电路115。举例来说,上拉控制电路113在输入信号vin及输出信号vout的上升沿处被使能。下推控制电路115在输入信号vin及输出信号vout的下降沿处被使能。比较器130包括耦合到上拉控制电路113的第一比较器131及耦合到下推控制电路115的第二比较器133。第一比较器131将由上拉控制电路113输出的差值信号idiff进行比较,且接着输出第一控制信号vctrl1以对转换速率增强进行使能。相似地,第二比较器133将由下推控制电路115输出的差值信号idiff进行比较,且接着输出第二控制信号vctrl2以对转换速率增强进行使能。

31.输入/输出信号比较器111包括第一n型晶体管srnt1及第一p型晶体管srpt1。第一n型晶体管srnt1具有耦合到运算放大器11的输入信号vin的控制端子(例如,栅极)、耦合到上拉控制电路113的第一端子(例如,漏极)、以及耦合到运算放大器11的输出信号vout的第二端子(例如,源极)。第一p型晶体管srpt1具有耦合到运算放大器11的输入信号vin的控制端子(例如,栅极)、耦合到下推控制电路115的第一端子(例如,漏极)、以及耦合到运算放大器11的输出信号vout的第二端子(例如,源极)。

32.在实施例中,上拉控制电路113及下推控制电路115可由电流镜实施,其中表示差值信号idiff的电流可由上拉控制电路113及下推控制电路115进行镜面反射,且输出到比较器130。上拉控制电路113可包括第二p型晶体管srpt2及第三p型晶体管srpt3。第二p型晶体管srpt2包括第一端子(例如,漏极)、耦合到第一供电电压vdd的第二端子(例如,源极)、以及控制端子(例如,栅极),其中第一端子与控制端子共同耦合到输入/输出信号比较器111的第一n型晶体管srnt1的第一端子,以用于接收差值信号(可被称为第一差值信号idiff1)。第三p型晶体管srpt3包括耦合到比较器130的第一端子(例如,漏极)、耦合到第一供电电压vdd的第二端子(例如,源极)、以及与第二p型晶体管srpt2的控制端子耦合的控制端子(例如,栅极),其中第三p型晶体管srpt3的第一端子将与输入信号vin和输出信号vout之间的第一差值信号idiff1对应的被镜面反射的第一差值信号输出到第一比较器131。

33.相似地,下推控制电路115包括第二n型晶体管srnt2及第三n型晶体管srnt3,第二n型晶体管srnt2与第三n型晶体管srnt3连接以形成电流镜。第二n型晶体管srnt2包括第一端子(例如,漏极)、耦合到第二供电电压vss的第二端子(例如,源极)、以及控制端子(例如,栅极),其中第一端子与控制端子共同耦合到输入/输出信号比较器111的第一p型晶体管srpt1的第一端子,以用于接收差值信号(可被称为第二差值信号idiff2)。第三n型晶体管srnt3包括耦合到比较器130的第一端子(例如,漏极)、耦合到第二供电电压vss的第二端子(例如,源极)、以及与第二n型晶体管srnt2的控制端子耦合的控制端子(例如,栅极),其中第三n型晶体管srnt3的第一端子将与输入信号vin和输出信号vout之间的第二差值信号idiff2对应的被镜面反射的第二差值信号输出到第二比较器133。

34.在实施例中,第一供电电压vdd可被称为在电路中界定高电势的供电电压,例如1v、3.3v、5v或基于设计要求的任何电压。第二供电电压vss可被称为在电路中界定低电势的供电电压,例如地电压、0v、0.1v或基于设计要求的任何电压。

35.在实施例中,第一比较器131及第二比较器133是各自包括电流源的电流比较器。第一比较器131包括与第三p型晶体管srpt3的第一端子耦合的第一端子以及耦合到第二供电电压vss的第二端子。如上所述,第三p型晶体管srpt3的第二端子耦合到第一供电电压

vdd。第一比较器131将由第二p型晶体管srpt2及第三p型晶体管srpt3进行镜面反射的第一差值信号idiff1与第一比较器131的电流源的恒定电流进行比较。当第一差值信号idiff1具有比电流源的恒定电流大的电流时,第一控制信号vctrl1将为高的。另一方面,当第一差值信号idiff1具有比电流源的恒定电流小的电流时,第一控制信号vctrl1将为低的。第二比较器133包括与第三n型晶体管srnt3的第一端子耦合的第一端子以及耦合到第一供电电压vdd的第二端子。第一比较器131将由第三n型晶体管srnt3镜面反射的第二差值信号idiff2与电流源的恒定电流进行比较。当第二差值信号idiff2具有比电流源的恒定电流大的电流时,第二控制信号vctrl2将为低的。另一方面,当第二差值信号idiff2具有比电流源的恒定电流小的电流时,第二控制信号vctrl2将为高的。

36.在实施例中,调整单元150包括来源部151及吸收部153。来源部151耦合到来自第一比较器131的第一控制信号vctrl1,且被配置成输出第一补偿信号vc1(也被称为ic1),以用于在输出信号vout的上升沿处对运算放大器11的输出信号vout进行上拉。吸收部153耦合到来自第二比较器133的第二控制信号vctrl2,且被配置成输出第二补偿信号vc2(也被称为ic2),以用于在输出信号vout的下降沿处对运算放大器11的输出信号vout进行下推。因此,可增强运算放大器11的转换速率。

37.来源部151及吸收部153各自包括多个按比例缩放通道,所述多个按比例缩放通道将第一供电电压vdd、第二供电电压vss耦合到运算放大器11,以用于在上升沿或下降沿处对输出信号vout进行上拉或下推。按比例缩放通道的数目由预先设定的第一比例控制信号sdg1[2:0]、第二比例控制信号sdg2[2:0]进行使能,以对第一补偿信号vc1、第二补偿信号vc2进行按比例缩放。举例来说,调整单元150可被预先配置成接通3个按比例缩放通道中的2个按比例缩放通道,以增强转换速率。在其他实施例中,第一比例控制信号sdg1[2:0]、第二比例控制信号sdg2[2:0]仅对1个通道或所有三个通道进行使能,以对补偿信号vc(即,vc1,vc2)进行按比例缩放。示出三个通道作为实例。然而,此并不旨在限制本公开。在替代实施例中,调整单元可包括各种数目的按比例缩放通道,例如1个、2个、4个、5个等。此外,能够用于转换速率增强的按比例缩放通道的数目在来源部151与吸收部153之间可不同。在一些实施例中,第一比例控制信号sdg1[2:0]可被预先配置成对3个通道进行使能以在上升沿处增强运算放大器11,而第二比例控制信号sdg2[2:0]可被预先配置成对2个通道进行使能以在下降沿处增强运算放大器11。“[2:0]”的说明表示第一控制信号及第二控制信号是3个位的信号,其中每一按比例缩放通道可被独立地控制。举例来说,第一比例控制信号sdg1[2:0]可为具有三个不同的控制信号的总线信号。

[0038]

在实施例中,来源部151及吸收部153的每一按比例缩放通道包括串联连接的电流源、第一开关及第二开关。在来源部151中,按比例缩放通道被配置成将电流从第一供电电压vdd源送到运算放大器11,而吸收部153的按比例缩放通道被配置成将电流从运算放大器11吸收到第二供电电压vss。详细来说,来源部151中的第一通道1510-1、第二通道1510-2、第三通道1510-3中的每一者均包括耦合到第一供电电压vdd的第一端以及耦合到调整单元150的输出端子的第二端,调整单元150的输出端子是sre电路100的耦合到运算放大器11的输出端子。另一方面,吸收部153中的按比例缩放通道1530-1、1530-2、1530-3中的每一者包括与调整单元150的输出端子耦合的第一端以及耦合到第二供电电压vss的第二端,调整单元150的输出端子是sre电路100的耦合到运算放大器11的输出端子。每一按比例缩放通道

包括在第一供电电压vdd或第二供电电压vss中的一者与运算放大器之间串联连接的第一开关、第二开关及电流源。

[0039]

举例来说,来源部151的第一通道1510-1包括第一开关1511-1、第二开关1513-1及电流源1515-1。详细来说,第一开关1511-1包括耦合到运算放大器11的第一端子、与第二开关1513-1的第一端子耦合的第二端子、以及耦合到接收第一控制信号vctrl1的第一比较器131的控制端子。第二开关1513-1还包括与电流源1515-1的第一端子耦合的第二端子以及耦合到第一比例控制信号sdg1[2:0]的控制端子。电流源1515-1还包括耦合到第一供电电压vdd的第二端子。如图3中所示的来源部151的第二通道1510-2及第三通道1510-3将具有与所述的第一通道1510-1中的结构相同的结构,且因此为简明起见不再对其予以赘述。

[0040]

参照图3,调整单元150的吸收部153还包括在运算放大器11与第二供电电压vss之间串联连接的缩放通道1530-1、1530-2及1530-3。吸收部153的缩放通道1530-1包括第一开关1531-1、第二开关1533-1及电流源1535-1。第一开关1531-1包括耦合到运算放大器11的第一端子、与第二开关1533-1的第一端子耦合的第二端子以及耦合到接收第二控制信号vctrl2的第二比较器133的控制端子。第二开关1533-1还包括与电流源1535-1的第一端子耦合的第二端子以及耦合到第二比例控制信号sdg2[2:0]的控制端子。电流源1535-1还包括耦合到第二供电电压vss的第二端子。如图3中所示的缩放通道1530-2及缩放通道1530-3将具有与所述的缩放通道1530-1中的结构相似的结构,且因此为简明起见不再对其予以赘述。

[0041]

在实施例中,来源部151及吸收部153中的每一通道的第一开关及第二开关可由例如mosfet等晶体管实施。

[0042]

第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]可为具有足以接通及关断来源部151及吸收部153的每一通道中的第二开关的电势的电压信号。在实施例中,第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]中的每一者可为3个位的信号或任何数目个位的信号,第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]中的每一者独立地控制来源部151及吸收部153的每一通道。举例来说,第一比例控制信号sdg1[2:0]可为总线信号,其中来源部151的每一按比例缩放通道中所包括的控制端子可耦合到总线上的线(或信号)。因此,可独立地控制或数字地控制来源部151的第一通道1510-1、第二通道1510-2、第三通道1510-3中的每一者中的第二开关,以对第一补偿信号vc1进行按比例缩放。相似地,对于吸收部153,第二比例控制信号sdg2[2:0]可为总线信号,其中吸收部153的每一按比例缩放通道中所包括的控制端子可耦合到总线上的线(或信号)。因此,可独立地控制或数字地控制吸收部153的缩放通道1530-1、1530-2、1530-3中的每一者中的第二开关,以对第二补偿信号vc2进行按比例缩放。在实施例中,第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]是预定的,其中总线信号可源自sre电路100或显示面板的源极驱动电路。在其他实施例中,第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]的预定或配置可在显示面板的定时控制器中进行配置。本公开并不旨在限制第一比例控制信号sdg1[2:0]及第二比例控制信号sdg2[2:0]的实施或来源。

[0043]

在sre电路100的运行中,运算放大器11的输入信号vin及运算放大器11的输出信号vout被馈送到sre电路100的输入/输出信号比较器111中。在其中输出信号vout的状态变化慢于输入信号vin(例如,上升沿)的情形中,第一n型晶体管srnt1将被使能且产生第一差

值信号idiff1。上拉控制电路113将第一差值信号idiff1输出到第一比较器131,其中第一比较器131将输出第一控制信号vctrl1,以用于对调整单元150的来源部151进行使能。第一控制信号vctrl1将通过输出第一补偿信号vc1对转换速率增强进行使能。第一补偿信号vc1的大小或比例将取决于预定的第一比例控制信号sdg1。

[0044]

在其中输出信号vout的状态变化快于输入信号vin(例如,下降沿)的情形中,第一p型晶体管srpt1将被使能且产生第二差值信号idiff2。下推控制电路115将第二差值信号idiff2输出到第二比较器133,其中第二比较器133将输出第二控制信号vctrl2,以用于对调整单元150的吸收部153进行使能。第二控制信号vctrl2将通过输出第二补偿信号vc2来对转换速率增强进行使能。第二补偿信号vc2的大小或比例将取决于预定的第二比例控制信号sdg2。

[0045]

图4是示出根据本公开实施例中的一个实施例的比较器330的示意图。在实施例中,信号边沿检测器110将与图3中所示的实施例相同。图2中所示的实施例与图3中所示的实施例之间的区别之一在于,图4所示实施例利用电压比较器代替电流比较器。

[0046]

参照图4,上拉控制电路113及下推控制电路115分别耦合到第一比较器331及第二比较器333。在实施例中,第一比较器331包括运算放大器3311及电阻器3313。运算放大器3311包括耦合到上拉控制电路113的输出与电阻器3313的一端之间的共用节点的第一端子(例如,反相端子)以及耦合到参考电压vref的第二端子(例如,非反相端子)。电阻器3313的另一端耦合到第二供电电压vss。第二比较器333包括运算放大器3331及电阻器3333。运算放大器3331包括耦合到参考电压vref的第一端子(例如,反相端子)以及耦合到下推控制电路115的输出与电阻器3333的一端之间的共用节点的第二端子(例如,非反相端子)。电阻器3333的另一端耦合到第一供电电压vdd。参考电压vref可为预定的恒定电压且被配置成基于设计要求输出第一控制信号vctrl1、第二控制信号vctrl2。在实施例中,比较器330将上拉控制电路113的输出处的电压及下推控制电路115的输出处的电压与参考电压vref进行比较,以根据输入信号vin及输出信号vout输出第一控制信号vctrl1及第二控制信号vctrl2。与图3中所示的实施例相似,第一控制信号vctrl1及第二控制信号vctrl2将根据输入信号vin与输出信号vout之间的差值信号idiff来启动调整单元150的来源部151及吸收部153。

[0047]

图5是示出根据本公开实施例中的一个实施例的运算放大器的示意图。应注意,图5仅示出运算放大器11的简化示意图作为实例。所属领域中的技术人员将认识到,除图5中所示的组件之外,各种电子组件(例如,晶体管、电容器、电阻器等)还可包括在运算放大器11中或从运算放大器11移除。参照图5,运算放大器11包括n型晶体管mn1到mn7、p型晶体管mp1到mp7、第一偏压电路101、第二偏压电路102、第一电容器c1及第二电容器c2。在运算放大器11的输入级中,第一输入级包括耦合到第二供电电压vss的n型晶体管mn1、mn2及第一偏压电路101,且第二输入级包括耦合到第一供电电压vdd的p型晶体管mp1、mp2及第二偏压电路102。

[0048]

在第一输入级中,n型晶体管mn1包括耦合到运算放大器11的输出电压vout的控制端子、耦合到运算放大器11的负载级(即,输入级的后续级)的第一端子、以及与第一偏压电路101的第一端子耦合的第二端子。n型晶体管mn2包括耦合到输入电压vin的控制端子、耦合到负载级的第一端子、以及与第一偏压电路101的第一端子耦合的第二端子。第一偏压电

路101还包括耦合到第二供电电压vss的第二端子。第一偏压电路101可由基于第二供电电压vss产生恒定电流的晶体管或其他组件来实施。在实施例中,在n型晶体管mn1、mn2的第二端子与第一偏压电路101的第一端子的交叉部位处形成有共用节点,共用节点也可被称为第一上部节点na1。

[0049]

在第二输入级中,p型晶体管mp1包括耦合到运算放大器11的输出电压vout的控制端子、耦合到负载级的第一端子、以及与第二偏压电路102的第一端子耦合的第二端子。p型晶体管mp2包括耦合到输入电压vin的控制端子、耦合到负载级的第一端子、以及与第二偏压电路102的第一端子耦合的第二端子。第二偏压电路102还包括耦合到第一供电电压vdd的第二端子。第二偏压电路102可由基于第一供电电压vdd产生恒定电流的晶体管或其他组件来实施。在实施例中,在p型晶体管mp1、mp2的第二端子与第二偏压电路102的第一端子的交叉部位处形成有共用节点,共用节点也可被称为第一底部节点nb1。

[0050]

运算放大器11的负载级包括n型晶体管mn3到mn6及p型晶体管mp3到mp6。p型晶体管mp3、mp4形成第一电流镜。p型晶体管mp3包括耦合到第一输入级(即,n型晶体管mn1的第一端子)的第一端子、耦合到第一供电电压vdd的第二端子以及与p型晶体管mp4的第一端子及控制端子耦合的控制端子。p型晶体管mp4还包括耦合到第一输入级(即,n型晶体管mn2的第一端子)的第一端子及耦合到第一供电电压vdd的第二端子。在p型晶体管mp3、mp4的控制端子与p型晶体管mp3的第一端子之间形成有共用节点,共用节点也可被称为第二上部节点na2。

[0051]

n型晶体管mn3、mn4形成第二电流镜。n型晶体管mn3包括耦合到第二输入级(即,p型晶体管mp1的第一端子)的第一端子、耦合到第二供电电压vss的第二端子、以及与n型晶体管mn4的第一端子及控制端子耦合的控制端子。n型晶体管mn4还包括耦合到第二输入级(即,p型晶体管mp2的第一端子)的第一端子以及耦合到第二供电电压vss的第二端子。在n型晶体管mn3、mn4的控制端子与n型晶体管mn3的第一端子之间形成有共用节点,共用节点也可被称为第二底部节点nb2。

[0052]

运算放大器11的负载级还包括耦合在第一电流镜与第二电流镜之间的第一连接电路及第二连接电路。在实施例中,第一连接电路包括p型晶体管mp5及n型晶体管mn5。p型晶体管mp5包括耦合到第二电流镜(即,n型晶体管mn3的第一端子)的第一端子、耦合到第一电流镜(即,p型晶体管mp3的第一端子)的第二端子、以及耦合到第一偏压电压v1的控制端子。n型晶体管mn5包括与p型晶体管mp5的第二端子及第一电流镜(即,p型晶体管mp3的第一端子)耦合的第一端子、与p型晶体管mp5的第一端子及第二电流镜(即,n型晶体管mn3的第一端子)耦合的第二端子、以及耦合到第二偏压电压v2的控制端子。

[0053]

第二连接电路包括p型晶体管mp6及n型晶体管mn6。p型晶体管mp6包括耦合到第二电流镜(即,n型晶体管mn4的第一端子)的第一端子、耦合到第一电流镜(即,p型晶体管mp4的第一端子)的第二端子以及耦合到第一偏压电压v1的控制端子。n型晶体管mn6包括与p型晶体管mp6的第二端子及第一电流镜(即,p型晶体管mp4的第二端子)耦合的第一端子、与p型晶体管mp6的第一端子及第二电流镜(即,n型晶体管mn4的第一端子)耦合的第二端子、以及耦合到第二偏压电压v2的控制端子。

[0054]

在实施例中,第一偏压电压v1及第二偏压电压v2是用于控制第一连接电路及第二连接电路的偏压电压。基于第一偏压电压v1控制p型晶体管mp5、mp6,且基于第二偏压电压

v2控制n型晶体管mn5、mn6。

[0055]

运算放大器11的输出级包括p型晶体管mp7及n型晶体管mn7。p型晶体管mp7包括耦合到负载级(即,p型晶体管mp4的第一端子)的控制端子、通过第一电容器c1耦合到负载级(即,p型晶体管mp4的第一端子)的第一端子、以及耦合到第一供电电压vdd的第二端子。n型晶体管mn7包括耦合到负载级(即,n型晶体管mn4的第一端子)的控制端子、通过第二电容器c2耦合到负载级(即,n型晶体管mn4的第一端子)的第一端子、以及耦合到第二供电电压vss的第二端子。运算放大器的输出端子将是形成在p型晶体管mp7的第一端子与n型晶体管mn7的第一端子之间的共用节点。

[0056]

参照图2及图4,可通过将第一补偿信号vc1及第二补偿信号vc2耦合到运算放大器11来改变运算放大器的输出通过率,以增强运算放大器11的转换速率。在实施例中的一个实施例中,来自调整单元150的第一补偿信号vc1可耦合到第一上部节点na1,以对运算放大器11的输出进行上拉,以用于增强上升沿处的转换速率。来自调整单元150的第二补偿信号vc2可耦合到第一底部节点nb1,以对运算放大器11的输出进行下推,以用于增强下降沿处的转换速率。

[0057]

在其他实施例中,来自调整单元150的第一补偿信号vc1可耦合到第二上部节点na2,以对运算放大器的输出进行上拉,以用于增强上升沿处的转换速率。来自调整单元150的第二补偿信号vc2可耦合到第二底部节点nb2,以对运算放大器11的输出进行下推,以用于增强下降沿处的转换速率。

[0058]

图6是示出根据本公开实施例中的一个实施例的运算放大器11a的示意图。图4中所示的实施例与图5中所示的实施例之间的区别在于在运算放大器的负载级中增加了晶体管mp3_1、mp4_1、mp5_1、mp6_1、mn3_1、mn4_1、mn5_1及mn6_1。在实施例中,也可通过将如图3中所示的sre电路100耦合到运算放大器11a来实现转换速率增强。与图5中所示的实施例相似,来自调整单元150的第一补偿信号vc1可耦合到第一上部节点na1或第二上部节点na2,以对运算放大器11a的输出进行上拉,以用于增强上升沿处的转换速率。来自调整单元150的第二补偿信号vc2可耦合到第一底部节点nb1或第二底部节点nb2,以对运算放大器11的输出进行下推,以用于增强下降沿处的转换速率。

[0059]

在实施例中的一个实施例中,第一补偿信号vc1可耦合到第一上部节点na1,而第二补偿信号vc2可耦合到第二底部节点nb2。在其他实施例中,第一补偿信号vc1可耦合到第二上部节点na2,而第二补偿信号vc2可耦合到第一底部节点nb1。本公开并不旨在限制sre电路与运算放大器之间的耦合关系。

[0060]

图7是示出根据本公开实施例中的一个实施例的具有全局调整单元750的sre电路700的示意图。在实施例中,全局调整单元750用于将第一补偿信号vc1、第二补偿信号vc2供应到多个运算放大器11_1到11_k,其中k大于1且小于n。返回参照图3及图4中所示的实施例,比较器130及330基于由信号边沿检测器110检测到的信号边沿来对调整单元150进行使能。调整单元150可被称为局部调整单元,局部调整单元将补偿信号vc提供到一个运算放大器11。参照图7,sre电路700包括信号边沿检测器110_1到110_k(每一源极线通道中的一者)、比较器130_1到130_k(每一源极线通道中的一者)及全局调整单元750。信号边沿检测器110_1到110_k及比较器130_1到130_k实质上与图3所示实施例相同。由于全局调整单元750是全局的(即,在不同的源极线通道之间共享),因此所述结构将不同于图3中所示的实

施例。然而,全局调整单元750与图3中所示的调整单元150的概念将是相似的,即增强全局调整单元750所连接的运算放大器11_1到11_k的转换速率。

[0061]

参照图7,全局调整单元750用于对分别耦合到多条源极线sl1到slk的多个运算放大器11_1到11_k进行补偿,所述多条源极线sl1到slk可被称为源极线通道。全局调整单元750包括来源部751、第一偏压产生电路752、吸收部753、第二偏压产生电路754及多个补偿使能电路755_1到755_k。来源部751耦合在第二供电电压vss与第一偏压产生电路752之间。吸收部753耦合在第一电源电压vdd与第二偏压产生电路754之间。补偿使能电路755_1到755_k中的每一者均耦合在第一偏产压生电路752与第二偏压产生电路754之间,且由比较器130_1到130_k提供的第一控制信号vctrl1及第二控制信号vctrl2控制。变量k可为1与n之间的任何数字。举例来说,如果k=3,则全局调整单元750用于将补偿信号(例如补偿电压或电流)提供到三个源极线通道。

[0062]

来源部751包括用于以三个不同的电平对补偿信号进行按比例缩放的三个按比例缩放通道,所述三个按比例缩放通道并联地连接在第一偏压控制电路752与第二供电电压vss之间。应注意,按比例缩放通道的数目可为基于设计要求的大于零的任何数目。举例来说,在替代实施例中,运算放大器需要更精细(或高分辨率)的台阶补偿信号,按比例缩放通道的数量可增加,此会增大转换速率增强中的电平数目。每一按比例缩放通道包括由第一预定按比例缩放控制信号sdg1[2:0]控制的开关及与所述开关串联连接的电流源。每一按比例缩放通道的开关可由三个不同的按比例缩放控制信号(即,sdg1[2:0],3个位的信号)独立地控制。按比例缩放通道中的任何一者的开关的使能将此按比例缩放通道的电流源耦合到第一偏压控制电路752,第一偏压控制电路752产生用于增强上升沿处的转换速率的补偿信号。对更多的按比例缩放通道进行使能将增加补偿信号的电平。吸收部753还包括并联地连接在第二偏压控制电路754与第一供电电压vdd之间的三个按比例缩放通道。吸收部753的按比例缩放通道中的每一者包括由第二预定按比例缩放控制信号sdg2[2:0]控制的开关及与所述开关串联连接的电流源。每一按比例缩放通道的开关可由三个不同的按比例缩放控制信号(即,sdg2[2:0],3个位的信号)独立地控制。按比例缩放通道中的任何一者的开关的使能将此按比例缩放通道的电流源耦合到第二偏压控制电路754,第二偏压控制电路754产生用于增强下降沿处的转换速率的补偿信号。对更多的按比例缩放通道进行使能将增加补偿信号的电平。应注意,在其他实施例中,吸收部753可包括与来源部751不同数目的按比例缩放通道。在一些实施例中,来源部751及吸收部753中的按比例缩放通道的开关可由晶体管实施。

[0063]

在实施例中,第一偏压控制电路752及第二偏压控制电路754可由电流镜实施。第一偏压控制电路752可包括p型晶体管mp8及多个p型晶体管mp9_1到mp9_k。p型晶体管mp8包括耦合到来源部751的第一端子、耦合到第一供电电压vdd的第二端子、以及耦合到第二端子及p型晶体管mp9_1到mp9_k中的每一者的控制端子。p型晶体管mp9_1到mp9_k中的每一者包括与p型晶体管mp9的控制端子耦合的控制端子,p型晶体管mp9与p型晶体管mp8形成电流镜。p型晶体管mp9_1到mp9_k中的每一者还包括耦合到对应的补偿使能电路755_1到755_k的第一端子以及耦合到第一供电电压vdd的第二端子。第二偏压控制电路754可包括n型晶体管mn8及多个n型晶体管mn9_1到mn9_k。n型晶体管mn8包括耦合到吸收部753的第一端子、耦合到第二供电电压vss的第二端子、以及耦合到第二端子及n型晶体管mn9_1到mn9_k中的

每一者的控制端子。n型晶体管mn9_1到mn9_k中的每一者包括与n型晶体管mn9的控制端子耦合的控制端子,n型晶体管mn9与n型晶体管mn8形成电流镜。n型晶体管mn9_1到mn9_k中的每一者还包括耦合到对应的补偿使能电路755_1到755_k的第一端子以及耦合到第二供电电压vss的第二端子。

[0064]

补偿使能电路755_1到755_k中的每一者耦合在第一偏压控制电路752及第二偏压控制电路754与运算放大器11_1到11_k中的一者之间,且由对应的比较器130_1到130_k基于信号边沿检测器110_1到110_k的输出来控制。补偿使能电路755_1到755_k中的每一者可包括来源开关及吸收开关。来源开关耦合在p型晶体管mp9_1与运算放大器11_1之间,且由来自比较器130_1的第一补偿信号vc1_1响应于上升沿处的信号边沿检测进行控制。吸收开关耦合在n型晶体管mn9_1与运算放大器11_1之间,且由来自比较器130_1的第二补偿信号vc2_1响应于下降沿处的信号边沿检测进行控制。755_2到755_k的结构与补偿使能电路755_1相同,且因此为简明起见不再对其予以赘述。

[0065]

在运行中,来源部751及吸收部753基于预定按比例缩放控制信号sdg1[2:0]、sdg2[2:0]而被使能,产生来源电流及吸收电流。第一偏压控制电路752及第二偏压控制电路754分别将来源电流及吸收电流耦合到补偿使能电路755_1到755_k中的每一者。在信号边沿检测器110_1到110_k检测到输入信号vin的上升沿时,比较器130_1到130_k将通过输出第一补偿信号vctrl1_1到vctrl1_k来对补偿使能电路755_1到755_k进行使能。补偿使能电路755_1到755_k的来源开关将响应于第一补偿信号vctrl1_1到vctrl1_k而被使能,此将来源电流从第一偏压控制电路752耦合到对应的运算放大器11_1到11_k,以对运算放大器11_1到11_k执行转换速率增强。另一方面,当信号边沿检测器110_1到110_k检测到输入信号vin的下降沿时,比较器130_1到130_k将通过输出第二补偿信号vctrl2_1到vctrl2_k来对补偿使能电路755_1到755_k进行使能。补偿使能电路755_1到755_k的吸收开关将响应于第二补偿信号vctrl2_1到vctrl2_k而被使能,此将吸收电流从第二偏压控制电路754耦合到对应的运算放大器11_1到11_k,以对运算放大器11_1到11_k执行转换速率增强。

[0066]

图8示出根据本公开实施例的sre电路800的方块图。sre电路800与图1中所示的sre电路100之间的区别之一在于增加了耦合到调整单元850的图案检测器870。图案检测器870用于在显示面板的节电模式期间增强一些运算放大器。举例来说,在节电模式期间,仅显示面板的一部分(即,一些像素)需要清晰的图像显示。在一些实施例中,仅显示面板的一部分显示图像,而显示面板的其他部分是黑色的或不变的。所述实施例是对显示面板的对应部分的运算放大器11选择性地执行转换速率增强。举例来说,当进入节电模式时,当指示特定通道需要维持在高转换速率时,图案检测器被配置成动态地调整调整单元850,呈现独立地控制特定通道的转换速率并实现更精确的节电状态的能力。此也可被称为动态转换速率增强(dynamic slew rate enhancement,dsre)。

[0067]

详细来说,sre电路800可耦合到控制器30,以用于获得节电信息。节电信息可包括在节电模式期间需要转换速率增强的源极线通道(即,由连接到源极线的运算放大器形成的通道)。节电信息被提供到图案检测器870。图案检测器870可根据节电信息对调整单元850进行使能或去能。因此,sre800能够动态地且选择性地对特定源极线通道的转换速率增强进行使能或去能。

[0068]

鉴于以上内容,在本公开的实施例中,转换速率增强电路根据输入信号与输出信

号之间的差值产生控制信号。控制信号用于选择性地将多个电流源耦合到运算放大器,从而分别控制输出波形的上升沿及下降沿。换句话说,通过将电流源耦合到运算放大器,可输出用于转换速率增强的补偿信号。依据检测出输入信号的上升沿或下降沿而定,sre电路可根据补偿信号对输出信号进行上拉或下推。此外,可通过选择性地对耦合到运算放大器的电流源的数目进行使能来数字地控制补偿信号,以对耦合到运算放大器的补偿信号进行按比例缩放。

[0069]

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,他们可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对其作出各种改变、代替及变更。

[0070]

附图标记列表

[0071]

1:显示器件

[0072]

10:源极驱动电路

[0073]

11、11a、11_1~11_n、3311、3331:运算放大器

[0074]

12:输出缓冲电路

[0075]

13:数模转换器(dac)

[0076]

14:数据锁存电路

[0077]

15:移位寄存器

[0078]

20:栅极驱动电路

[0079]

30:控制器

[0080]

40:显示面板

[0081]

41、41_11~41_nm:像素

[0082]

100、100_1~100_n、700、800:转换速率增强(sre)电路

[0083]

101:第一偏压电路

[0084]

102:第二偏压电路

[0085]

110:信号边沿检测器

[0086]

110_1~110_k:信号边沿检测器

[0087]

111:输入/输出信号比较器

[0088]

113:上拉控制电路

[0089]

115:下推控制电路

[0090]

130:比较器

[0091]

130_1~130_k:比较器

[0092]

131、331:第一比较器

[0093]

133、333:第二比较器

[0094]

150、850:调整单元

[0095]

151、751:来源部

[0096]

153、753:吸收部

[0097]

330:比较器

[0098]

750:全局调整单元

[0099]

752:第一偏压产生电路

[0100]

754:第二偏压产生电路

[0101]

755_1~755_k:补偿使能电路

[0102]

870:图案检测器

[0103]

1510-1:第一通道

[0104]

1510-2:第二通道

[0105]

1510-3:第三通道

[0106]

1511-1、1531-1:第一开关

[0107]

1513-1:第二开关

[0108]

1515-1、1535-1:电流源

[0109]

1530-1:按比例缩放通道

[0110]

1530-2:按比例缩放通道

[0111]

1530-3:按比例缩放通道

[0112]

1533-1:第二开关

[0113]

3313、3333:电阻器

[0114]

c1:第一电容器

[0115]

c2:第二电容器

[0116]

clk:时钟信号

[0117]

d1~dn:模拟信号

[0118]

data:像素数据

[0119]

gl1~glm:栅极线

[0120]

gma:灰度电压

[0121]

idiff:差值信号

[0122]

idiff1:第一差值信号

[0123]

idiff2:第二差值信号

[0124]

mn1、mn2、mn3、mn4、mn5、mn6、mn7、mn8、mn9、mn9_1~mn9_k:n型晶体管

[0125]

mn3_1、mn4_1、mn5_1、mn6_1、mp3_1、mp4_1、mp5_1、mp6_1:晶体管

[0126]

mp1、mp2、mp3、mp4、mp5、mp6、mp7、mp8、mp9、mp9_1~mp9_k:p型晶体管

[0127]

na1:第一上部节点

[0128]

na2:第二上部节点

[0129]

nb1:第一底部节点

[0130]

nb2:第二底部节点

[0131]

sdg1:第一比例控制信号

[0132]

sdg1[2:0]:第一比例控制信号

[0133]

sdg2:第二比例控制信号

[0134]

sdg2[2:0]:第二比例控制信号

[0135]

sl1~sln:源极线

[0136]

srnt1:第一n型晶体管

[0137]

srnt2:第二n型晶体管

[0138]

srnt3:第三n型晶体管

[0139]

srpt1:第一p型晶体管

[0140]

srpt2:第二p型晶体管

[0141]

srpt3:第三p型晶体管

[0142]

v1:第一偏压电压

[0143]

v2:第二偏压电压

[0144]

vc:补偿信号

[0145]

vc1:第一补偿信号

[0146]

vc2:第二补偿信号

[0147]

vc1_1:第一补偿信号

[0148]

vc2_1:第二补偿信号

[0149]

vctrl1:第一控制信号

[0150]

vctrl1_1~vctrl1_k:第一补偿信号

[0151]

vctrl2:第二控制信号

[0152]

vctrl2_1~vctrl2_k:第二补偿信号

[0153]

vdd:第一供电电压

[0154]

vss:第二供电电压

[0155]

vin:输入信号

[0156]

vin_1~vin_n:输入电压信号

[0157]

voff:关断电压

[0158]

von:接通电压

[0159]

vout:输出信号

[0160]

vref:参考电压