1.本发明涉及显示技术领域,尤其涉及一种像素电路以及其制造方法。

背景技术:

2.液晶显示(liquid crystal display,lcd)面板具有节能、轻薄、以及画面精致等优点,因此在显示技术领域获得了广泛的应用。通常,液晶显示面板的结构包括上基板、下基板、以及配置于所述上基板以及所述下基板之间的液晶层(liquid crystal layer)。所述上基板上设置有彩色滤光片,所述下基板上设置有薄膜晶体管(thin-film transistor,tft)阵列层。所述上基板以及所述下基板采取分别制造的方式,再经过对位组合以及使用边框胶在所述上基板以及所述下基板周边封闭所述液晶层,最后形成所述液晶显示面板所需要的液晶盒(liquid crystal cell)。

3.然而,所述液晶显示面板的边框的宽度会受到液晶盒的封装技术、所述液晶显示面板的像素电路的走线设计、或是所述液晶显示面板的制程需求而影响。一旦所述液晶显示面板的所述边框的所述宽度越大,所述液晶显示面板实际能显示的面积就越小。

4.近年来,随着所述显示技术领域不断地发展,人们对于所述液晶显示面板的要求越来越严格。所述液晶显示面板的屏占比,即所述液晶显示面板屏幕的显示面积占所述液晶显示面板的比例,必须越来越高。诸如窄边框电视以及全面屏手机,为了提高屏占比、增大显示面积,就必须将所述液晶显示面板的所述边框极尽所能地缩小、窄化,使得所述液晶显示面板取得更简洁、更细致、更美观的造型。

5.现有的所述液晶显示面板的像素电路,是通过垂直交错的数据线以及扫描线提供驱动的。在所述数据线的一侧边需要预留出覆晶薄膜封装(chip-on-film,cof)绑定的空间。在所述扫描线的一侧边虽然可以通过栅极驱动电路阵列(gate-on-array,goa)而去除覆晶薄膜封装所需要的绑定空间,但是由于所述栅极驱动电路阵列的电路复杂,所述扫描线的所述侧边仍然需要保留一定的空间。由于所述扫描线的所述侧边以及所述扫描线的所述侧边都无法进一步的缩减空间,则所述液晶显示面板所述边框仍然会具有一定的宽度,使得所述液晶显示面板的屏占比无法提升。

技术实现要素:

6.本发明提供液晶显示面板的一种像素电路以及其制造方法,能够缩减所述液晶显示面板的像素电路对应的扫描线的一侧边的边框宽度,进而使得所述液晶显示面板的屏占比提升。

7.本发明的所述像素电路包括薄膜晶体管、第一扫描线、第二扫描线、以及数据线。所述第一扫描线沿第一方向设置。所述第一扫描线电性连接所述薄膜晶体管。所述第二扫描线沿第二方向设置。所述第二扫描线电性连接所述第一扫描线。所述第二方向与所述第一方向垂直。所述数据线沿所述第二方向设置。所述数据线电性连接所述薄膜晶体管。

8.在一实施例中,所述像素电路还包括辅助扫描线。所述辅助扫描线沿第二方向设

置。所述辅助扫描线的两端电性连接所述第二扫描线。

9.在一实施例中,所述辅助扫描线与所述第一扫描线设置在第一走线层。所述辅助扫描线与所述第一扫描线于所述第一走线层中彼此绝缘。

10.在一实施例中,所述数据线与所述第二扫描线设置在第二走线层。所述数据线与所述第二扫描线于所述第二走线层中彼此绝缘。

11.在一实施例中,所述像素电路还包括像素电极。所述像素电极设置在所述数据线与所述第二扫描线以及所述辅助扫描线之间。所述像素电极电性连接所述薄膜晶体管。

12.本发明的所述像素电路的制造方法,其特征在于,包括以下步骤:

13.沿第一方向形成第一扫描线以及栅极,所述栅极电性连接所述第一扫描线;

14.在所述栅极上形成栅极绝缘层;

15.在所述栅极绝缘层上形成有源层;

16.在所述有源层上形成源极以及漏极,所述源极以及所述漏极电性连接所述有源层;

17.沿第二方向形成第二扫描线,所述第二方向与所述第一方向垂直,所述第二扫描线电性连接所述第一扫描线;以及

18.沿第二方向形成数据线,所述数据线电性连接所述源极。

19.在一实施例中,所述像素电路的制造方法还包括以下步骤:

20.沿第二方向形成辅助扫描线,所述辅助扫描线两端电性连接所述第二扫描线。

21.在一实施例中,所述辅助扫描线与所述第一扫描线由第一走线层形成。所述辅助扫描线与所述第一扫描线于所述第一走线层中彼此绝缘。

22.在一实施例中,所述数据线与所述第二扫描线由第二走线层形成。所述数据线与所述第二扫描线于所述第二走线层中彼此绝缘。

23.在一实施例中,所述像素电路的制造方法还包括以下步骤:

24.在所述数据线与所述第二扫描线以及所述辅助扫描线之间形成像素电极,所述像素电极电性连接所述漏极。

25.在习知技术中,驱动液晶显示面板的垂直交错输入的数据线以及扫描线会造成所述液晶显示面板的两个相邻边具有较宽的边框。本发明的所述像素电路以及其制造方法通过沿着所述第一方向设置的所述第一扫描线以及沿着所述第二方向设置的所述第二扫描线的设计,将所述薄膜晶体管的扫描信号输入端与数据信号输入端设置在所述液晶显示面板的同一侧。因此,应用本发明的液晶显示面板能够有效节省所述液晶显示面板的布线空间、并且缩减习知技术的所示液晶显示面板的所述边框的空间,使得应用本发明的所述像素电路的所述液晶显示面板的屏占比相较习知技术的所述液晶显示面板的屏占比提升。并且,本发明的所述像素电路以及其制造方法进一步设置与所述第二扫描线并联的所述辅助扫描线,使得所述第一扫描线以及所述第二扫描线的电阻降低,同时减低所述第一扫描线以及所述第二扫描线与其他走线或是所述像素电极之间的寄生电容,进而维持所述液晶显示面板的预期效能。

附图说明

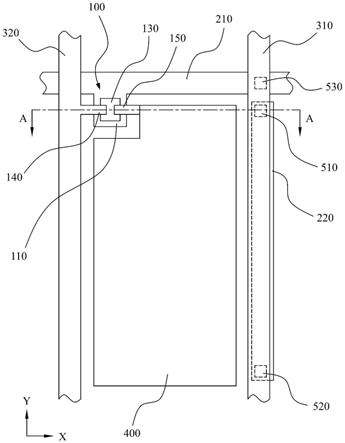

26.图1为本发明的像素电路的结构图。

27.图2为应用本发明的所述像素路的液晶显示面板沿图1的a-a线剖切的部分剖面图。

28.图3为应用本发明的所述像素电路的所述液晶显示面板的部分电路图。

29.图4至图8为本发明的所述像素电路在各个制造过程的结构图。

具体实施方式

30.为了让本发明之上述及其他目的、特征、优点能更明显易懂,下文将特举本发明优选实施例,并配合附图,作详细说明如下。

31.本发明提供液晶显示面板的一种像素电路。请参照图1,其为本发明的像素电路的结构图。本发明的所述像素电路包括薄膜晶体管100、第一扫描线210、第二扫描线310、以及数据线320。

32.本发明如图1所示的所述像素电路对应所述液晶显示面板的一个像素。因此,所述液晶显示面板在应用本发明的所述像素电路时,可以依据实际需求设置与多个所述像素相同数量的多个所述像素电路。

33.所述薄膜晶体管100基本包括源极140、漏极150、以及栅极110。所述源极140用以接收所述液晶显示面板的数据信号。所述栅极110用以接收所述液晶显示面板的扫描信号,并且通过所述扫描信号控制所述源极140以及所述漏极150之间的通路以及断路,以达成所述液晶显示面板的所述像素的图像显示。

34.如图1所示,所述第一扫描线210沿第一方向x设置,并且所述第一扫描线210电性连接所述薄膜晶体管100的所述栅极110。所述第二扫描线310沿第二方向y设置,并且所述第二扫描线310通过第三通孔530电性连接所述第一扫描线210。所述数据线320沿第二方向y设置,并且所述数据线320电性连接所述薄膜晶体管100。在本实施例中,所述第二方向y与所述第一方x向垂直。

35.如图1所示,所述像素电路还包括像素电极400。所述像素电极400设置在所述数据线320与所述第二扫描线310以及所述辅助扫描线220之间。所述像素电极400电性连接所述薄膜晶体管100的所述漏极150。当所述液晶显示面板的所述扫描信号通过所述第二扫描线310以及所述第一扫描线210输入至所述薄膜晶体管100的所述栅极110时,所述薄膜晶体管100便会开启,使得所述液晶显示面板的所述数据信号能够经由所述数据线320、所述源极140、以及所述漏极150输入至所述像素电极400中。

36.在本实施例中,所述数据线320以及所述第二扫描线310具有一定的间隔距离。如此,除了能够有效进行像素的电路走线配置,以维持所述像素的开口率之外,还能够防止所述数据线320以及所述第二扫描线310产生寄生电容,进而维持所述像素电路应有的运作效能。

37.在一实施例中,如图1所示,所述像素电路还包括辅助扫描线220。所述辅助扫描线220沿第二方向y设置。所述辅助扫描线220的两端分别通过第一通孔510以及第二通孔520电性连接所述第二扫描线310。

38.当所述液晶显示面板的所述扫描信号在传递时,需要通过所述第二扫描线310以及所述第一扫描线210才能输入进所述薄膜晶体管100的所述栅极110,因此,本发明的所述像素电路中的所述扫描信号的走线路径大于习知技术的像素电路的扫描信号的走线路径。

由于较长的所述扫描信号的所述走线路径将会伴随走线电阻的提升,因此会造成所述扫描信号的延迟、或是所述薄膜晶体管100的充电不足,最终减损所述液晶显示面板的显示效果。

39.本发明的所述像素电路考量到上述问题,故设置与所述第二扫描线310并联的所述辅助扫描线220,以增加所述扫描信号的所述走线路径的等效截面积,进而降低所述走线电阻。在所述第一通孔510以及所述第二通孔520之间,所述扫描信号的所述走线路径的所述等效截面积大大的提升,因此所述走线电阻减低、所述扫描信号不会延迟、并且维持所述薄膜晶体管100的应有充电能力,最终维持所述液晶显示面板的显示效果。

40.请参照图2,其为应用本发明的所述像素路的所述液晶显示面板沿图1的a-a线剖切的部分剖面图。本发明通过所述液晶显示面板的部分剖面图,示例性地说明所述像素电路中的各个元件之间的相对关系。

41.本发明的所述像素电路设置于所述液晶显示面板的基板600上。在所述基板600上设置有所述像素电路的第一走线层200。所述第一走线层200包括所述薄膜晶体管100的所述栅极110、所述第一扫描线210(图中未示)、以及所述辅助扫描线220。所述栅极110、所述第一扫描线210、以及所述辅助扫描线220由铜(cu)或是铜钼(cumo)合金在同一道制程形成。所述栅极110、所述第一扫描线210、以及所述辅助扫描线220的厚度范围在2500埃(angstrom,)至8000埃,并且较佳地为7000埃。

42.需要注意的是,在所述第一走线层200中,所述辅助扫描线220与所述第一扫描线210彼此绝缘,即所述辅助扫描线220与所述第一扫描线210在同一水平面上互不相连接。

43.如图2所示,所述第一走线层200上覆盖有栅极绝缘层120。所述栅极绝缘层120设置的目的除了是为了隔绝所述薄膜晶体管100后续叠层中的有源层130、所述源极140、以及所述漏极150之外,同时也扮演著平坦化所述辅助扫描线220区域的目的。

44.在图2中,所述栅极绝缘层120对应所述辅助扫描线220的上方的区域开设有所述第一通孔510。所述第一通孔510用以电性连接所述辅助扫描线220以及其上设置的所述第二扫描线310。在所述栅极绝缘层120对应所述栅极110的区域设置有所述有源层130。在所述有源层130的两侧设置有所述源极140以及所述漏极150。所述有源层130由氧化铟镓锌(indium gallium zinc oxide,igzo)或是非晶硅(a-si)材料制成。

45.在所述栅极绝缘层120上还设置有所述像素电路的第二走线层300。所述第二走线层300包括所述数据线320以及所述第二扫描线310。所述源极140电性连接所述数据线320。所述数据线320以及所述第二扫描线310由铜(cu)或是铜钼(cumo)合金在同一道制程形成。所述数据线320以及所述第二扫描线310的厚度范围在2500埃(angstrom,)至8000埃,并且较佳地为7000埃。

46.需要注意的是,在所述第二走线层300中,所述数据线320与所述第二扫描线310彼此绝缘,即所述数据线320与所述第二扫描线310在同一水平面上互不相连接。

47.如图2所示,所述第二走线层300上覆盖有钝化层700。所述钝化层700设置的目的除了是为了隔绝所述薄膜晶体管100、所述数据线320、以及所述第二扫描线310之外,同时也扮演著平坦化的目的,为后续叠层的所述像素电极400形成基底。

48.所述钝化层700对应所述薄膜晶体管100的所述漏极150上的区域开设有第四通孔540。所述第四通孔540用以电性连接所述漏极150以及其上设置的所述像素电极400。

49.图2所示的所述液晶显示面板的部分剖面图仅是示例性地表示应用本发明的所述像素电路的所述液晶显示面板的部分结构,图2并非用以限制本发明的所述像素电路。另外,所述液晶显示面板用以达成显示画面的其馀必要元件并未示出于图2中,在显示技术领域的技术人员应当能通过本领域的习知技术理解上述实施例的所述液晶显示面板的所述其馀必要元件的设置。

50.请参照图3,其为应用本发明的所述像素电路的所述液晶显示面板的部分电路图。配合参照图1的所述像素电路,图3示出的所述液晶显示面板的部分电路图包括4行以及4列的所述像素电路。换句话说,图3示出了具有16个所述像素电极400控制的16个所述像素。在图1以及图3中,所述第一方向x为所述液晶显示面板的水平方向,并且所述第二方向y为所述液晶显示面板的垂直方向。

51.由于电性连接所述薄膜晶体管100的所述第一扫描线210沿着所述第一方向x设置,并且所述第一扫描线210进一步地电性连接沿着所述第二方向y设置的所述第二扫描线310,因此所述液晶显示面板的所述扫描信号的输入端scan可以设置在所述第二方向y的正方向或是负方向。在本实施例中,所述扫描信号的所述输入端scan可以设置在所述液晶显示面板的上侧。

52.另外,由于电性连接所述薄膜晶体管100所述像素电路的所述数据线320沿着所述第二方向y设置,因此所述液晶显示面板的所述数据信号的输入端data可以设置在所述第二方向y的正方向或是负方向。在本实施例中,所述数据信号的所述输入端data可以设置在所述液晶显示面板的所述上侧,即,所述扫描信号的所述输入端scan与所述数据信号的所述输入端data设置在同一个侧边。

53.如图3所示,虽然所述扫描信号的所述输入端scan到每一个所述像素电路的所述薄膜晶体管100的所述走线路径距离相较习知技术的所述走线路径较长,但是本发明将所述第二扫描线310并联设置了所述辅助扫描线220,以增加所述扫描信号的所述走线路径的所述等效截面积,进而降低所述走线电阻。

54.由图3的范例可以得知,得益于本发明的所述像素电路的结构设计,所述液晶显示面板的所述扫描信号的所述输入端scan以及所述数据信号的所述输入端data能够设置在所述液晶显示面板的同一侧。因此,所述液晶显示面板的边框的三个侧边便无须作为任何输入端而设置驱动芯片或是作为绑定端等,进而有效节省所述液晶显示面板的布线空间、并且缩减边框的空间,使得所述液晶显示面板的屏占比得以提升。

55.本发明还提供液晶显示面板的一种像素电路的制造方法。请参照图4至图8,其为本发明的所述像素电路在各个制造过程的结构图。

56.本发明如图4至图8所示制造出的所述像素电路对应所述液晶显示面板的一个像素。因此,所述液晶显示面板在应用本发明的所述像素电路时,可以依据实际需求设置与多个所述像素相同数量的多个所述像素电路。在本实施例中,图4至图8示例性地示出2行以及2列的所述像素电路,即4个所述像素电路阵列地排列在各个制造过程的结构图。

57.以下将配合参照前述实施例的图2说明所述像素电路的制造方法。本发明通过图2所示的所述液晶显示面板的部分剖面图,示例性地说明所述像素电路在各个制造过程中的各个元件之间的相对关系。

58.请参照图2以及图4,在此步骤中,首先在所示液晶显示面板所需要的基板600上形

成第一走线层200,并且通过曝光、显影、以及蚀刻等图案化的方法形成第一扫描线210以及栅极110。在此步骤中,所述第一扫描线210以及所述栅极110沿第一方向x形成,并且所述栅极110电性连接所述第一扫描线210。在一实施例中,此步骤还可以包括由所述第一走线层沿第二方向y形成辅助扫描线220。在本实施例中,所述第二方向y与所述第一方x向垂直。

59.在此步骤中,所述栅极110、所述第一扫描线210、以及所述辅助扫描线220由铜(cu)或是铜钼(cumo)合金的所述第一走线层200形成。所述栅极110、所述第一扫描线210、以及所述辅助扫描线220的厚度范围在2500埃(angstrom,)至8000埃,并且较佳地为7000埃。

60.需要注意的是,在所述第一走线层200的所述图案化过程中,所述辅助扫描线220与所述第一扫描线210彼此绝缘,即所述辅助扫描线220与所述第一扫描线210在同一水平面上互不相连接。

61.在图4示出的所述栅极110、所述第一扫描线210、以及所述辅助扫描线220形成之后,所述像素电路的制造方法在所述第一走线层200上形成如图2所示的栅极绝缘层120。所述栅极绝缘层120设置的目的除了是为了隔绝后续叠层中的薄膜晶体管100的有源层130、所述源极140、以及所述漏极150之外,同时也扮演著平坦化所述辅助扫描线220区域的目的。

62.请参照图2以及图5,在此步骤中,所述像素电路的制造方法在所述栅极绝缘层120对应所述辅助扫描线220的两端的上方的区域分别开设第一通孔510以及第二通孔520、在所述栅极绝缘层120对应所述第一扫描线210与所述辅助扫描线220轴线相交的上方的区域开设第三通孔530。

63.请参照图2以及图6,在此步骤中,所述像素电路的制造方法在所述栅极绝缘层120对应所述栅极110上方的区域形成所述有源层130。所述有源层130由氧化铟镓锌(indium gallium zinc oxide,igzo)或是非晶硅(a-si)材料制成。

64.请参照图2以及图7,在此步骤中,所述像素电路的制造方法在所述有源层130的两侧形成所述源极140以及所述漏极150。经过前述的步骤后,所述像素电路已形成了所述栅极110、所述栅极绝缘层120、所述有源层130、所述源极140、以及所述漏极150。所述栅极110、所述栅极绝缘层120、所述有源层130、所述源极140、以及所述漏极150便组成基本的所述薄膜晶体管100。所述源极140用以接收所述液晶显示面板的数据信号。所述栅极110用以接收所述液晶显示面板的扫描信号,并且通过所述扫描信号控制所述源极140以及所述漏极150之间的通路以及断路,以达成所述液晶显示面板的所述像素的图像显示。

65.如图2以及图7所示,此步骤还包括在所述栅极绝缘层120上形成第二走线层300,并且通过曝光、显影、以及蚀刻等图案化的方法形成第二扫描线310以及数据线320。在此步骤中,所述第二扫描线310沿所述第二方向y形成,并且所述第二扫描线310通过所述第三通孔530电性连接所述第一扫描线210以及通过所述第一通孔510以及所述第二通孔520电性连接所述辅助扫描线220。另外,在此步骤中,所述数据线320沿所述第二方向y形成,并且所述数据线320电性连接所述源极140。

66.当所述液晶显示面板的所述扫描信号在传递时,需要通过所述第二扫描线310以及所述第一扫描线210才能输入进所述薄膜晶体管100的所述栅极110,因此,本发明的所述像素电路中的所述扫描信号的走线路径大于习知技术的像素电路的扫描信号的走线路径。

由于较长的所述扫描信号的所述走线路径将会伴随走线电阻的提升,因此会造成所述扫描信号的延迟、或是所述薄膜晶体管100的充电不足,最终减损所述液晶显示面板的显示效果。

67.本发明的所述像素电路考量到上述问题,故设置与所述第二扫描线310并联的所述辅助扫描线220,以增加所述扫描信号的所述走线路径的等效截面积,进而降低所述走线电阻。在所述第一通孔510以及所述第二通孔520之间,所述扫描信号的所述走线路径的所述等效截面积大大的提升,因此所述走线电阻减低、所述扫描信号不会延迟、并且维持所述薄膜晶体管100的应有充电能力,最终维持所述液晶显示面板的显示效果。

68.在此步骤中,所述第二扫描线310以及所述数据线320由铜(cu)或是铜钼(cumo)合金的所述第二走线层300形成。所述数据线320以及所述第二扫描线310的厚度范围在2500埃(angstrom,)至8000埃,并且较佳地为7000埃。

69.需要注意的是,在所述第二走线层300的所述图案化过程中,所述数据线320与所述第二扫描线310彼此绝缘,即所述数据线320与所述第二扫描线310在同一水平面上互不相连接。

70.在图7示出的所述数据线320以及所述第二扫描线310形成之后,所述像素电路的制造方法所述第二走线层300上形成如图2所示的钝化层700。所述钝化层700设置的目的除了是为了隔绝所述薄膜晶体管100、所述数据线320、以及所述第二扫描线310之外,同时也扮演著平坦化的目的,为后续叠层的像素电极400形成基底。

71.请参照图2以及图8,在此步骤中,所述像素电路的制造方法在所述钝化层700对应所述薄膜晶体管100的所述漏极150上的区域开设第四通孔540。此步骤还包括在所述钝化层700上形成所述像素电极400,并且所述像素电极400通过所述第四通孔540电性连接所述漏极150。如图8所示,在俯视图中,所述像素电极400设置在所述数据线320与所述第二扫描线310以及所述辅助扫描线220之间。当所述液晶显示面板的所述扫描信号通过所述第二扫描线310以及所述第一扫描线210输入至所述薄膜晶体管100的所述栅极110时,所述薄膜晶体管100便会开启,使得所述液晶显示面板的所述数据信号能够经由所述数据线320、所述源极140、以及所述漏极150输入至所述像素电极400中。

72.在本实施例中,所述数据线320以及所述第二扫描线310具有一定的间隔距离。如此,除了能够有效进行像素的电路走线配置,以维持所述像素的开口率之外,还能够防止所述数据线320以及所述第二扫描线310产生寄生电容,进而维持所述像素电路应有的运作效能。

73.图4至图8所示的所述像素电路在各个制造过程的结构图仅是表示本发明的所述像素电路的制造方法,并非用以限制本发明的所述像素电路。另外,应用本发明的所述像素电路的制造方法的所述液晶显示面板用以达成显示画面的其馀必要元件并未示出于图4至图8中,在显示技术领域的技术人员应当能通过本领域的习知技术理解上述实施例的所述液晶显示面板的所述其馀必要元件的设置。

74.请参照图3,其为应用本发明的所述像素电路的所述液晶显示面板的部分电路图。图3示出的所述液晶显示面板的部分电路图包括4行以及4列的所述像素电路。换句话说,图3示出了具有4组如图4至图8示出的所述像素电路的制造方法制造出的4个所述像素电路。在图3中,所述第一方向x为所述液晶显示面板的水平方向,并且所述第二方向y为所述液晶

显示面板的垂直方向。

75.由于电性连接所述薄膜晶体管100的所述第一扫描线21沿着所述第一方向x设置,并且所述第一扫描线21进一步地电性连接沿着所述第二方向y设置的所述第二扫描线310,因此所述液晶显示面板的所述扫描信号的输入端scan可以设置在所述第二方向y的正方向或是负方向。在本实施例中,所述扫描信号的所述输入端scan可以设置在所述液晶显示面板的上侧。

76.另外,由于电性连接所述薄膜晶体管100所述像素电路的所述数据线320沿着所述第二方向y设置,因此所述液晶显示面板的所述数据信号的输入端data可以设置在所述第二方向y的正方向或是负方向。在本实施例中,所述数据信号的所述输入端data可以设置在所述液晶显示面板的所述上侧,即,所述扫描信号的所述输入端scan与所述数据信号的所述输入端data设置在同一个侧边。

77.如图3所示,虽然所述扫描信号的所述输入端scan到每一个所述像素电路的所述薄膜晶体管100的所述走线路径距离相较习知技术的所述走线路径较长,但是本发明将所述第二扫描线310并联设置了所述辅助扫描线220,以增加所述扫描信号的所述走线路径的所述等效截面积,进而降低所述走线电阻。

78.由图3的范例可以得知,得益于本发明的所述像素电路的结构设计,所述液晶显示面板的所述扫描信号的所述输入端scan以及所述数据信号的所述输入端data能够设置在所述液晶显示面板的同一侧。因此,所述液晶显示面板的边框的三个侧边便无须作为任何输入端而设置驱动芯片或是作为绑定端等,进而有效节省所述液晶显示面板的布线空间、并且缩减边框的空间,使得所述液晶显示面板的屏占比得以提升。

79.发明人在付出了创造性劳动之后完成了本发明的所述像素电路,以下提供本发明的实验数据辅助说明,将应用本发明的所述液晶显示面板与习知技术的所述液晶显示面板进行比较。

80.请参照下表1,其对比了习知技术的所述液晶显示面板的四个侧边的宽度以及应用本发明的所述像素电路的所述液晶显示面板的四个侧边的宽度。

81.需要说明的是,在表1中,习知技术的所述液晶显示面板的上边框的位置、以及应用本发明的所述像素电路的所述液晶显示面板的上边框的位置,皆设置有所述扫描信号的所述输入端以及所述数据信号的所述输入端。

82.表1

[0083][0084]

在习知技术中,驱动液晶显示面板的垂直交错输入的数据线以及扫描线会造成所

述液晶显示面板的两个相邻边具有较宽的边框。本发明的所述像素电路以及其制造方法通过沿着所述第一方向x设置的所述第一扫描线210以及沿着所述第二方向y设置的所述第二扫描线310的设计,将所述薄膜晶体管100的所述扫描信号的所述输入端scan与所述数据信号的所述输入端data设置在所述液晶显示面板的同一侧。因此,由表1可以得知,应用本发明的液晶显示面板能够有效节省所述液晶显示面板的布线空间、并且缩减习知技术的所示液晶显示面板的所述边框的空间,使得应用本发明的所述像素电路的所述液晶显示面板的屏占比相较习知技术的所述液晶显示面板的屏占比提升。

[0085]

请参照下表2,其对比了习知技术的所述液晶显示面板的所述扫描线(以第一扫描线栏位名称表示)的电阻以及电容、应用本发明的未设置所述辅助扫描线220的所述像素电路的所述液晶显示面板的所述第一扫描线210以及所述第二扫描线310的电阻以及电容、以及应用本发明的设置有所述辅助扫描线220的所述像素电路的所述第一扫描线210以及所述第二扫描线310的所述液晶显示面板的电阻以及电容。

[0086]

表2

[0087][0088]

如表2所示,本发明的所述像素电路以及其制造方法设置了所述第二扫描线310之后,相较习知技术会额外增加电阻。故本发明进一步设置与所述第二扫描线310并联的所述辅助扫描线220,这使得所述第一扫描线210以及所述第二扫描线310的电阻明显降低。

[0089]

因此,本发明的所述像素电路以及其制造方法除了能够使应用本发明的所述像素电路的所述液晶显示面板的屏占比相较习知技术的所述液晶显示面板的屏占比提升之外,还能维持所述液晶显示面板的预期效能。

[0090]

以上仅是本发明的优选实施方式,应当指出,对于所属领域技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。