1.本技术涉及医疗诊断技术领域,尤其涉及一种超声成像系统和模拟前端芯片。

背景技术:

2.软件波束合成超声系统相比于基于硬件波束合成超声系统,有着方案灵活功能更强等特点。但是目前用于超声成像系统的模拟前端芯片(analog front end,afe)并非为软件波束合成系统设计,这些模拟前端芯片输出的高速数据不能直接传输给cpu或gpu等数据处理单元,如pc机,必须使用fpga(field programmable gate array,现场可编辑逻辑门阵列)做转接器件,才能将数据传输给cpu或gpu等数据处理单元进行软件波束合成。fpga一般为通用器件,会集成很多计算单元,功耗高,体积大,价格贵,仅用于数据传输会有比较大的浪费,也增加了系统成本。

技术实现要素:

3.本技术提供了一种超声成像系统和模拟前端芯片,旨在解决软件波束合成超声系统必须使用fpga做转接器件,才能将数据传输给cpu或gpu等处理器进行软件波束合成等技术问题。

4.第一方面,本技术实施例提供了一种超声成像系统,包括:

5.收发电路,用于控制超声探头发射超声波,以及接收所述超声波的回波以获得超声回波模拟信号;

6.模拟前端芯片,包括集成于所述模拟前端芯片的前端处理电路和数据传输电路,所述前端处理电路连接所述收发电路,用于对超声回波模拟信号进行预设处理,得到超声回波数字信号;所述数据传输电路连接所述前端处理电路,所述数据传输电路包括支持预设协议的第一接口,所述数据传输电路用于接收所述超声回波数字信号,将所述超声回波数字信号封装为预设协议的数据包,以及将所述预设协议的数据包通过所述第一接口直接传输给图形处理器,其中所述预设协议为能够与图形处理器直接通信的协议;

7.图形处理器,所述图形处理器连接所述数据传输电路的所述第一接口,用于通过所述第一接口直接与所述模拟前端芯片通信,以获取所述数据传输电路上传的所述预设协议的数据包,以及对所述预设协议的数据包中的超声回波数字信号进行波束合成处理。

8.第二方面,本技术实施例提供了一种模拟前端芯片,用于超声成像系统,所述模拟前端芯片包括集成于所述模拟前端芯片的前端处理电路和数据传输电路,其中:

9.所述前端处理电路用于连接所述超声成像系统中的收发电路,对所述收发电路获得的超声回波模拟信号进行预设处理,得到超声回波数字信号;

10.所述数据传输电路包括支持预设协议的第一接口,所述第一接口用于直接与处理器通信,所述数据传输电路用于接收所述超声回波数字信号,将所述超声回波数字信号封装为预设协议的数据包,以及将所述预设协议的数据包通过所述第一接口直接传输给所述处理器,所述预设协议为能够与图形处理器直接通信的协议,以便所述处理器对所述预设

协议的数据包中的超声回波数字信号进行波束合成处理。

11.本技术实施例提供了一种超声成像系统和模拟前端芯片,系统包括收发电路、模拟前端芯片及图形处理器,模拟前端芯片中集成的数据传输电路包括支持预设协议的第一接口,将超声回波数字信号封装为预设协议的数据包;图形处理器通过数据传输电路的第一接口直接与模拟前端芯片通信,以获取数据传输电路上传的预设协议的数据包,以及对预设协议的数据包中的超声回波数字信号进行波束合成处理。通过在模拟前端芯片中集成支持预设协议的数据传输电路,使得模拟前端芯片能够直接与图形处理器通信,将超声回波数字信号传输至图形处理器,而不需要通过fpga等昂贵的器件做转接器件,以防止对fpga性能的浪费,降低基于软件波束合成的超声成像系统成本和能耗。

12.应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本技术实施例的公开内容。

附图说明

13.为了更清楚地说明本技术实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

14.图1是现有的一种超声成像系统的示意性框图;

15.图2是本技术实施例提供的一种超声成像系统的示意性框图;

16.图3是一实施方式中模拟前端芯片的结构示意图;

17.图4至图10是不同实施方式中超声成像系统的示意性框图;

18.图11是本技术实施例提供的一种模拟前端芯片的示意性框图。

19.附图标记说明:100、超声成像系统;110、收发电路;120、模拟前端芯片;130、转接电路;140、处理器;

20.200、超声成像系统;210、收发电路;211、第二fpga;212、激励电路;220、模拟前端芯片;221、前端处理电路;201、低噪声放大电路;202、衰减器电路;203、可变增益放大电路;204、低通滤波电路;205、模数转换电路;206、解调降采样滤波电路;222、数据传输电路;230、图形处理器;240、第一fpga;250、第三fpga;10、第一接口;20、第二接口;30、第三接口。

具体实施方式

21.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

22.附图中所示的流程图仅是示例说明,不是必须包括所有的内容和操作/步骤,也不是必须按所描述的顺序执行。例如,有的操作/步骤还可以分解、组合或部分合并,因此实际执行的顺序有可能根据实际情况改变。

23.下面结合附图,对本技术的一些实施方式作详细说明。在不冲突的情况下,下述的实施例及实施例中的特征可以相互组合。

24.如图1所示为目前一种超声成像系统100的示意性框图,收发电路110用于控制超

声探头发射超声波,以及接收超声波的回波以获得超声回波模拟信号,模拟前端芯片120用于将超声回波模拟信号处理为超声回波数字信号。由于目前的模拟前端芯片120并非为软件波束合成系统设计,其接口一般为jesd总线接口或lvds(low voltage differential signaling,低压差分信号)总线接口,主要是用于与fpga连接和通信,模拟前端芯片120输出的超声回波数字信号不能直接传输给cpu、gpu等处理器140。目前通常采用fpga做转接器件130,才能将数据传输给cpu或gpu等处理器140进行软件波束合成。fpga一般为通用器件,由于用于进行波束合成的超声回波数字信号的数据量巨大,对总线的传输速度要求很高,由于数据率高带宽高,要求fpga与模拟前端芯片120通信的接口,如serdes(serializer/deserializer,串行器/解串器)接口要有非常好的性能,例如需要采用多通道高性能serdes接口的fpga。但是带高速serdes接口的fpga会有很多计算单元,功耗高,体积大,价格贵,仅用于数据传输会有比较大的浪费,也增加了系统成本。

25.为了解决软件波束合成超声系统必须使用fpga做转接器件,才能将数据传输给cpu或gpu等处理器进行软件波束合成等技术问题,本技术的发明人对超声成像系统进行了改进,以防止对fpga性能的浪费,降低基于软件波束合成的超声成像系统成本和能耗。

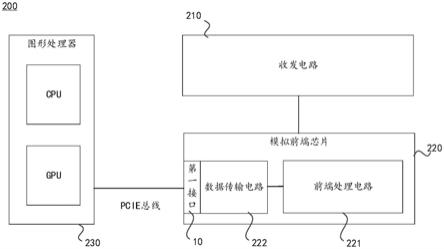

26.请参阅图2,图2是本技术实施例提供的一种超声成像系统200的示意性框图。

27.如图2所示,超声成像系统200包括:收发电路210、模拟前端芯片220以及图形处理器230。收发电路210至少连接模拟前端芯片220,模拟前端芯片220直接与图形处理器230连接,不需要fpga做转接器件。

28.其中,收发电路210用于控制超声探头发射超声波,以及接收超声波的回波以获得超声回波模拟信号。

29.在一些实施方式中,收发电路210包括发射电路和隔离电路,隔离电路连接于发射电路和模拟前端芯片220,用于控制发射电路与超声探头连通或者模拟前端芯片220与超声探头连通。发射电路与超声探头连通时,发射电路控制超声探头发射超声波;模拟前端芯片220与超声探头连通时,超声探头接收超声波的回波并输出超声回波模拟信号给模拟前端芯片220。示例性的,隔离电路包括限压开关,将超声回波模拟信号传送给接收通道上的模拟前端芯片220,并保护接收通道不受发射电路发射超声波影响。

30.请参阅图2,模拟前端芯片220包括集成于模拟前端芯片220的前端处理电路221和数据传输电路222,前端处理电路221的输入端连接收发电路210的输出端,前端处理电路221的输出端连接数据传输电路222的输入端,数据传输电路222的输出端连接图形处理器230。前端处理电路221用于对收发电路210获取的超声回波模拟信号进行预设处理,得到超声回波数字信号,数据传输电路222用于将前端处理电路221得到超声回波数字信号传输给图形处理器230。

31.在一些实施方式中,请参阅图3,前端处理电路221包括:低噪声放大电路201、衰减器电路202、可变增益放大电路203、低通滤波电路204、模数转换电路205和解调降采样滤波电路206,其中低噪声放大电路201、衰减器电路202、可变增益放大电路203、低通滤波电路204、模数转换电路205和解调降采样滤波电路206依次连接,且低噪声放大电路201连接收发电路210,解调降采样滤波电路206连接数据传输电路222。当然也不限于此,例如在一些实施方式中前端处理电路221可以不包括衰减器电路202、低通滤波电路204、解调降采样滤波电路206中的一种或多种;在另一些实施方式中,低噪声放大电路201、衰减器电路202、可

变增益放大电路203、低通滤波电路204、模数转换电路205和解调降采样滤波电路206的连接顺序也可以与图3中的连接顺序不同。

32.示例性的,低噪声放大电路201用于对超声回波模拟信号进行第一放大处理,低噪声放大电路201例如包括低噪声前放大器lna,放大的增益可以为15db、18db、21db;衰减器电路202用于对第一放大处理后的超声回波模拟信号进行衰减处理,衰减器电路202例如包括衰减器atten,衰减处理的增益可以为0db至负36db;可变增益放大电路203用于对衰减处理后的超声回波模拟信号进行第二放大处理,可变增益放大电路203例如包括可编程增益放大器pga,放大的增益可以为21db、24db、27db;低通滤波电路204用于对第二放大处理后的超声回波模拟信号进行抗混叠滤波处理,低通滤波电路204例如包括低通滤波器lpc,如包括抗混叠滤波器(anti-alias filter);模数转换电路205(adc)用于对抗混叠滤波处理后的超声回波模拟信号进行模数转换以得到超声回波数字信号,实现模拟信号到数字信号的转换;解调降采样滤波电路206用于对超声回波数字信号进行移频和降采样处理,解调降采样滤波电路206例如包括dsp(digital signal processing,数字信号图形处理器230),实现调制信号从载波频率移频到零频,并降低数据率,得到移频降采样后的数字信号。其中,衰减器电路202、可变增益放大电路203可以用于补偿超声波信号随探测深度变化引起的幅度的指数衰减。

33.在一些实施方式中,前端处理电路221包括多个处理通道,可以并行处理多路(如16路)超声回波模拟信号。

34.请参阅图2,模拟前端芯片220中的数据传输电路222连接前端处理电路221,数据传输电路222包括支持预设协议的第一接口10,数据传输电路222用于接收超声回波数字信号,将超声回波数字信号封装为预设协议的数据包,以及将预设协议的数据包通过第一接口10直接传输给图形处理器230,其中所述预设协议为能够与图形处理器230直接通信的协议。

35.图形处理器230用于多通道数据的软件波束合成。在一些实施方式中,图形处理器230包括cpu和/或gpu,可选的,cpu可以是集成有gpu的cpu。

36.示例性的,超声成像系统200包括cpu和gpu,其中gpu作为图形处理器230对超声回波数字信号进行软件波束合成,可选的,cpu可以根据gpu软件波束合成得到的数据生成超声图像,当然也可以由gpu根据软件波束合成得到的数据生成超声图像。

37.通过在模拟前端芯片220中集成支持预设协议的数据传输电路222,使得模拟前端芯片220能够直接与图形处理器230通信,将超声回波数字信号传输至图形处理器230。具体的,图形处理器230连接数据传输电路222的第一接口10,用于通过第一接口10直接与模拟前端芯片220通信,以获取数据传输电路222上传的预设协议的数据包,以及对预设协议的数据包中的超声回波数字信号进行波束合成处理。

38.在一些实施方式中,如图2所示,第一接口10包括支持pcie(peripheral component interconnect express)协议的总线接口或支持thunderbolt协议的总线接口,当然也不限于此,可以理解的,第一接口10可以包括任何能够直接与cpu、gpu等图形处理器230直接连接和通信的接口,且该接口具有足够的数据传输能力,cpu、gpu等图形处理器230能够直接通过第一接口10访问模拟前端芯片220,获取预设协议的数据包,而不需要通过fpga等昂贵的器件做转接器件。示例性的,第一接口10为用于向图形处理器230传输超声回

波数字信号的serdes接口、thunderbolt接口或者type-c接口。

39.在一些实施方式中,请参阅图3,数据传输电路222包括pcie控制器,pcie控制器用于将超声回波数字信号封装为pcie协议或thunderbolt协议的数据包。目前通用的x86系统最普遍的高速外设总线是支持pcie协议的总线或支持thunderbolt协议的总线,通过在模拟前端芯片220中集成支持pcie协议的总线接口或支持thunderbolt协议的总线接口,可以使模拟前端芯片220能够与cpu或gpu直接通信,将超声回波数字信号传输至图形处理器230。

40.如图3所示,pcie控制器连接前端处理电路221中的解调降采样滤波电路206,接收解调降采样滤波电路206输出的经移频和降采样处理后的超声回波数字信号,将接收的超声回波数字信号封装为pcie协议或thunderbolt协议的数据包,以及将pcie协议或thunderbolt协议的数据包通过支持pcie协议的总线接口或支持thunderbolt协议的总线接口传输给图形处理器230,图形处理器230解析该数据包,以及处理解析数据包得到的超声回波数字信号,得到超声图像。

41.在一些实施方式中,集成于模拟前端芯片220的前端处理电路221和数据传输电路222可以基于模拟前端芯片220的内部协议进行数据传输(即接收超声回波数字信号)。示例性的,pcie控制器基于内部协议从前端处理电路221接收超声回波数字信号,将接收到的超声回波数字信号封装为预设协议的数据包后,通过第一接口10将预设协议的数据包传输至图形处理器230。

42.在一些实施方式中,请参阅图4至图8,超声成像系统200还包括第一fpga240,收发电路210包括第二fpga211和激励电路212。示例性的,收发电路210中的发射电路包括第二fpga211和激励电路212。

43.示例性的,请参阅图4至图8,第一fpga240包括用于与第二fpga211、数据传输电路222、图形处理器230中的一种或多种连接并通信的serdes接口,所述serdes接口的通道数小于或等于8。

44.具体的,图形处理器230还用于向第一fpga240发送超声波接收时序,以及向第二fpga211发送超声波发射时序。超声波接收时序和超声波发射时序可以由图形处理器230中的cpu生成和发送,或者可以由图形处理器230中的gpu生成和发送,或者可以由图形处理器230中的cpu生成以及由图形处理器230中的gpu发送,或者可以由图形处理器230中的gpu生成以及由图形处理器230中的cpu发送。举例而言,第一fpga240可以获取图形处理器230发送的超声波接收时序和/或超声波发射时序,还可以将获取的超声波发射时序发送给第二fpga211;或者,图形处理器230将超声波接收时序和/或超声波发射时序发送给数据传输电路222,第一fpga240可以从数据传输电路222获取超声波接收时序和/或超声波发射时序,以及将获取的超声波发射时序发送给第二fpga211,当然也不限于此。

45.请参阅图2至图8,在模拟前端芯片220集成支持预设协议的数据传输电路222,如pcie控制器,超声回波数字信号可以从模拟前端芯片220的数据传输电路222传输给图形处理器230,因此第一fpga240不需要传输超声回波数字信号,减少了fpga的数据传输量。可以理解的,第一fpga240不需要采用具有多通道高性能数据接口的fpga,对fpga的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。在一些实施方式中,所述超声回波数字信号的通道数为256时,所述第一fpga的serdes接口的通道数小于

10,因此一个fpga就能满足设计要求。

46.在一些实施方式中,第一fpga240用于根据超声波接收时序控制前端处理电路221采样超声探头获取的超声波的回波,以获得超声回波数字信号。

47.示例性的,第一fpga240用于根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据,数据传输电路222用于将被标记为有效数据的超声回波数字信号封装为预设协议的数据包。

48.在一些实施方式中,前端处理电路221按照预设的采样率对超声回波模拟信号进行模数转换采样,得到一系列的超声回波数字信号。可以通过超声波接收时序标记超声探头每一次发射的超声波对应的需要处理的超声回波数字信号,即有效数据。

49.示例性的,第一fpga240用于根据超声波接收时序发送同步信号给前端处理电路221中的解调降采样滤波电路206,解调降采样滤波电路206用于根据该同步信号标记超声回波数字信号中的有效数据,使模拟前端芯片220采集的数据可以携带每线每帧的扫描信息,如时序信息。

50.示例性的,可以直接标记有效的超声回波数字信号,或者可以标记无效的超声回波数字信号,未标记的超声回波数字信号为有效的超声回波数字信号。示例性的,数据传输电路222将有效的超声回波数字信号封装为预设协议的数据包传输给图形处理器230,无效的超声回波数字信号则不传输给图形处理器230,可以降低模拟前端芯片220和图形处理器230之间需要的数据量,提高资源利用率。

51.示例性的,请参阅图4至图8,第二fpga211连接激励电路212,第二fpga211用于根据超声波发射时序控制激励电路212激励超声探头发射超声波。

52.示例性的,第二fpga211用于根据超声波发射时序进行发射波束合成,产生延时激励信号和发射波形给激励电路212,激励电路212例如包括发射功率模块,发射功率模块将功率放大后的发射波形传输给超声探头,以使超声探头发射超声波。

53.请参阅图1,目前的超声成像系统100中的fpga不仅需要传输超声波接收时序、超声波发射时序等扫描参数,还需要传输超声回波数字信号,数据率高带宽要求高,所以对fpga的serdes接口的性能要求高。举例而言,fpga传输256通道的超声回波数字信号时需要64个serdes通道从模拟前端芯片120接收超声回波数字信号,超声成像系统100中的fpga还与处理器140的pcie接口连接,还需要32个serdes通道去传输超声波接收时序、超声波发射时序等扫描参数,如此多的serdes通道通过1个fpga也无法实现,往往需要多个fpga,多个fpga之间的级联还需1至2个serdes通道。但是带多通道的高速serdes接口的fpga会有很多计算单元,功耗高,体积大,价格贵。

54.请参阅图2至图8,在模拟前端芯片220集成支持预设协议的数据传输电路222,如pcie控制器,超声回波数字信号可以从模拟前端芯片220的数据传输电路222传输给图形处理器230,因此第一fpga240、第二fpga211不需要传输超声回波数字信号,减少了fpga的数据传输量。举例而言,在处理256通道的超声回波数字信号时可以节约64个serdes通道。因此,可以只需要一个或两个fpga就能实现,减少了fpga的数量,也减少了对serdes通道数量的需求,对fpga的设计要求降低了,fpga的lut资源可以节约80%。另外,数据量没那么大了,对fpga的lut(查找表)存储资源也可以减配,也就是说fpga中的存储单元的设计也相应的减少或者降低了。

55.可以理解的,第一fpga240、第二fpga211不需要采用具有多通道高性能数据接口的fpga,对fpga的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。在一些实施方式中,所述超声回波数字信号的通道数为256时,所述第一fpga的serdes接口的通道数小于64,所述第二fpga的serdes接口的通道数小于64。示例性的,所述超声回波数字信号的通道数为256时,所述第一fpga的serdes接口的通道数小于10,所述第二fpga的serdes接口的通道数小于10。

56.在一些实施方式中,如图4所示,第一fpga240连接数据传输电路222和第二fpga211,数据传输电路222还用于将图形处理器230发送的超声波发射时序和超声波接收时序发送给第一fpga240,第一fpga240用于将超声波发射时序发送给第二fpga211,以便第二fpga211根据超声波发射时序控制激励电路212激励超声探头发射超声波,以及第一fpga240根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据。在本实施方式中,第一fpga240、收发电路210可以共用数据传输电路222的第一接口10与图形处理器230进行通信,第一fpga240、第二fpga211传输超声回波数字信号,也不需要与图形处理器230通过例如pcie接口进行连接,第一fpga240可以与数据传输电路222连接用于接收扫描参数。

57.示例性的,第一fpga240与第二fpga211通过serdes接口连接并通信,该serdes接口只需1至2个serdes通道即可。由于超声波发射时序的数据量相较于超声回波数字信号的数据量较小,第一fpga240、第二fpga211不需要具有多通道高性能的serdes接口,对fpga的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。

58.示例性的,第一fpga240包括用于与数据传输电路222通信的serdes接口,第一fpga240与数据传输电路222通过该serdes接口连接并通信,该serdes接口的通道数可以小于或等于8,可选的,该serdes接口只需1至2个serdes通道即可。由于第一fpga240、第二fpga211不需要传输超声回波数字信号,对第一fpga240与数据传输电路222的serdes接口的性能需求较低,也不需要多通道高性能的serdes接口。

59.在一些实施方式中,如图5所示,第一fpga240包括支持预设协议的第二接口20,第一fpga240通过第二接口20连接图形处理器230,以及第一fpga240连接第二fpga211,例如第一fpga240与第二fpga211通过serdes接口连接并通信。第一fpga240用于接收图形处理器230发送的超声波发射时序和超声波接收时序,以根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据,以及将超声波发射时序发送给第二fpga211,以便第二fpga211根据超声波发射时序控制激励电路212激励超声探头发射超声波。由于第一fpga240、第二fpga211不需要传输超声回波数字信号,对第二接口20、连接第一fpga240与第二fpga211的接口的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。

60.如图5所示,超声波发射时序和超声波接收时序等扫描参数可以不经数据传输电路222传输,数据相对独立,可以简化第一fpga240、第二fpga211与模拟前端芯片220之间的设计;示例性的,第二接口20包括serdes接口,该serdes接口的通道数小于或等于8。虽然第一fpga240与图形处理器230之间通过serdes接口进行连接,但是不需要传输超声回波数字信号,传输的扫描参数的数据量少,只需1至2个serdes通道即可,因此,也只需简单的fpga就能实现。

61.在一些实施方式中,如图6所示,第一fpga240连接数据传输电路222,例如,第一fpga240与数据传输电路222通过serdes接口连接并通信。数据传输电路222还用于将图形处理器230发送的超声波接收时序发送给第一fpga240,第一fpga240用于根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据。第二fpga211包括支持预设协议的第三接口30,第二fpga211通过第三接口30连接图形处理器230,第二fpga211用于获取图形处理器230发送的超声波发射时序,以及根据超声波发射时序控制激励电路212激励超声探头发射超声波。示例性的,第一fpga240包括用于与数据传输电路222通信的serdes接口,第一fpga240与数据传输电路222通过该serdes接口连接并通信,该serdes接口的通道数可以小于或等于8,可选的,该serdes接口只需1至2个serdes通道即可。由于第一fpga240、第二fpga211不需要传输超声回波数字信号,对第三接口30、连接第一fpga240与数据传输电路222的serdes接口的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。

62.如图6所示,超声波发射时序可以不经数据传输电路222传输,数据相对独立,可以简化第二fpga211与第一fpga240、模拟前端芯片220之间的设计;虽然第二fpga211与图形处理器230之间通过例如pcie接口进行连接,但是不需要传输超声回波数字信号,传输的超声波发射时序的数据量少,只需1至2个serdes通道即可,因此,也只需简单的fpga就能实现。

63.在一些实施方式中,如图7所示,第二fpga211包括支持预设协议的第三接口30,第二fpga211通过第三接口30连接图形处理器230,以及第一fpga240连接第二fpga211,例如第一fpga240与第二fpga211通过serdes接口连接并通信。第二fpga211用于接收图形处理器230发送的超声波发射时序和超声波接收时序,第二fpga211还用于根据超声波发射时序控制激励电路212激励超声探头发射超声波,以及将超声波接收时序发送给第一fpga240,以便第一fpga240用于根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据。由于第一fpga240、第二fpga211不需要传输超声回波数字信号,对第三接口30、连接第一fpga240与第二fpga211的接口的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。

64.如图7所示,超声波发射时序和超声波接收时序等扫描参数可以不经数据传输电路222传输,数据相对独立,可以简化第一fpga240、第二fpga211与模拟前端芯片220之间的设计;示例性的,第三接口30包括serdes接口,该serdes接口的通道数小于或等于8。虽然第二fpga211与图形处理器230之间通过例如serdes接口进行连接,但是不需要传输超声回波数字信号,传输的扫描参数的数据量少,只需1至2个serdes通道即可,因此,也只需简单的fpga就能实现。

65.在一些实施方式中,如图8所示,第一fpga240包括支持预设协议的第二接口20并通过第二接口20连接图形处理器230,第二fpga211包括支持预设协议的第三接口30并通过第三接口30连接图形处理器230。第一fpga240用于获取图形处理器230发送的超声波接收时序,以及根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据,数据传输电路222用于将被标记为有效数据的超声回波数字信号封装为预设协议的数据包;第二fpga211用于获取图形处理器230发送的超声波发射时序,以及根据超声波发射时序控制激励电路212激励超声探头发射超声波。由于第一fpga240、第二fpga211不需要传输

超声回波数字信号,对第二接口20、第三接口30的性能需求较低,常规的fpga就可以满足需求,不会造成fpga资源的浪费,且成本较低。

66.如图8所示,超声波发射时序和超声波接收时序等扫描参数可以不经数据传输电路222传输,数据相对独立,可以简化第一fpga240、第二fpga211与模拟前端芯片220之间的设计;示例性的,第二接口20、第三接口30包括serdes接口,该serdes接口的通道数小于或等于8。虽然第一fpga240、第二fpga211与图形处理器230之间通过serdes接口进行连接,但是不需要传输超声回波数字信号,传输的扫描参数的数据量少,只需1至2个serdes通道即可,因此,也只需简单的fpga就能实现。

67.请结合前述实施方式参阅图9和图10,在其他一些实施方式中,前述的第一fpga240、第二fpga211的功能可以由同一个fpga实现,可以简化相应的连接关系。具体的,如图9和图10所示,超声成像系统200包括第三fpga250,收发电路210包括激励电路212;其中,第三fpga250用于根据超声波发射时序控制激励电路212激励超声探头发射超声波,以及根据超声波接收时序标记模拟前端芯片220的超声回波数字信号中的有效数据,数据传输电路222用于将被标记为有效数据的超声回波数字信号封装为预设协议的数据包。

68.示例性的,如图9所示,第三fpga250连接数据传输电路222和激励电路212,数据传输电路222还用于将图形处理器230发送的超声波发射时序和超声波接收时序发送给第三fpga250。

69.可选的,第三fpga250包括用于与数据传输电路222通信的serdes接口,serdes接口的通道数小于或等于8。

70.示例性的,如图10所示,第三fpga250连接图形处理器230和激励电路212;第三fpga250用于接收图形处理器230发送的超声波发射时序和超声波接收时序。

71.可选的,第三fpga250包括用于与图形处理器230通信的serdes接口,serdes接口的通道数小于或等于8。

72.本技术实施例提供的超声成像系统,包括收发电路、模拟前端芯片以及处理器,其中模拟前端芯片的数据传输电路包括支持预设协议的第一接口,将超声回波数字信号封装为预设协议的数据包;处理器连接数据传输电路的第一接口,用于通过第一接口直接与模拟前端芯片通信,以获取数据传输电路上传的预设协议的数据包,以及对预设协议的数据包中的超声回波数字信号进行波束合成处理,得到超声图像。通过在模拟前端芯片中集成支持预设协议的数据传输电路,使得模拟前端芯片能够直接与处理器通信,将超声回波数字信号传输至处理器,而不需要通过fpga等昂贵的器件做转接器件,以防止对fpga性能的浪费,降低基于软件波束合成的超声成像系统成本和能耗。

73.请结合上述实施例参阅图11,图11是本技术实施例提供的用于超声成像系统200的模拟前端芯片220的示意性框图。

74.如图11所示,模拟前端芯片220包括集成于模拟前端芯片220的前端处理电路221和数据传输电路222。其中,前端处理电路221用于连接超声成像系统200中的收发电路210,对收发电路210获得的超声回波模拟信号进行预设处理,得到超声回波数字信号;数据传输电路222包括支持预设协议的第一接口10,第一接口10用于直接与图形处理器230通信,数据传输电路222用于接收超声回波数字信号,将超声回波数字信号封装为预设协议的数据包,以及将预设协议的数据包通过第一接口10直接传输给图形处理器230,所述预设协议为

能够与图形处理器直接通信的协议,以便图形处理器230对预设协议的数据包中的超声回波数字信号进行波束合成处理。

75.在一些实施方式中,前端处理电路221包括:低噪声放大电路201、衰减器电路202、可变增益放大电路203、低通滤波电路204、模数转换电路205和解调降采样滤波电路206,其中低噪声放大电路201、衰减器电路202、可变增益放大电路203、低通滤波电路204、模数转换电路205和解调降采样滤波电路206依次连接,且低噪声放大电路201连接收发电路210,解调降采样滤波电路206连接数据传输电路222;低噪声放大电路201用于对超声回波模拟信号进行第一放大处理,衰减器电路202用于对第一放大处理后的超声回波模拟信号进行衰减处理,可变增益放大电路203用于对衰减处理后的超声回波模拟信号进行第二放大处理,低通滤波电路204用于对第二放大处理后的超声回波模拟信号进行抗混叠滤波处理,模数转换电路205用于对抗混叠滤波处理后的超声回波模拟信号进行模数转换以得到超声回波数字信号,解调降采样滤波电路206用于对超声回波数字信号进行移频和降采样处理。

76.在一些实施方式中,数据传输电路222包括pcie控制器,pcie控制器用于将超声回波数字信号封装为pcie协议或thunderbolt协议的数据包。

77.在一些实施方式中,第一接口10包括支持pcie协议的总线接口或支持thunderbolt协议的总线接口。

78.在一些实施方式中,数据传输电路222与超声成像系统200中的fpga连接,可以理解的,该fpga可以为前述的第三fpga250,或者可以包括前述的第一fpga240和第二fpga211。例如数据传输电路222还包括serdes接口,serdes接口能够与超声成像系统200中的fpga240连接。数据传输电路222还用于将图形处理器230发送的超声波接收时序和/或超声波发射时序发送给该fpga;其中,该fpga用于根据所述超声波发射时序控制收发电路210中的激励电路212激励超声探头发射超声波,以及用于根据所述超声波接收时序标记超声回波数字信号中的有效数据,数据传输电路222用于将被标记为有效数据的超声回波数字信号封装为预设协议的数据包。

79.本技术实施例提供的模拟前端芯片的具体原理和实现方式均与前述实施例的超声成像系统类似,此处不再赘述。

80.应当理解,在此本技术中所使用的术语仅仅是出于描述特定实施例的目的而并不意在限制本技术。

81.还应当理解,在本技术和所附权利要求书中使用的术语“和/或”是指相关联列出的项中的一个或多个的任何组合以及所有可能组合,并且包括这些组合。

82.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以权利要求的保护范围为准。