一种用于pciis智能一体化系统的基于数码管的显示电路

技术领域

1.本实用新型属于电子技术领域,具体涉及一种用于pciis智能一体化系统的基于数码管的显示电路。

背景技术:

2.现目前的没有一套专门的用于pciis智能一体化系统的基于数码管的显示电路,本技术经过设计和测试,提出了一套专门的用于pciis智能一体化系统的基于数码管的显示电路,该显示电路相较于现有技术相比能满足实际的使用场景,传输内容更加丰富,尤其是针对专门的用于pciis智能一体化系统。

技术实现要素:

3.针对现有技术中的上述不足,本实用新型提供的一种用于pciis智能一体化系统的基于数码管的显示电路解决了现有技术中存在的问题。

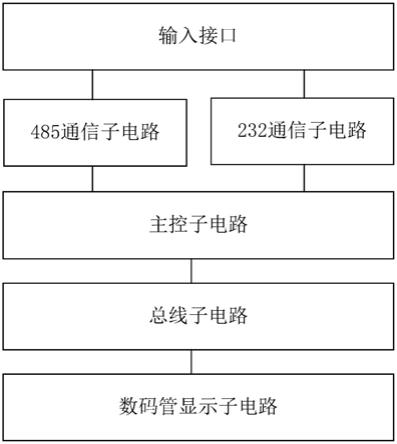

4.为了达到上述发明目的,本实用新型采用的技术方案为:一种用于pciis智能一体化系统的基于数码管的显示电路,包括输入接口、485通信子电路、232通信子电路、主控子电路、总线子电路以及数码管显示子电路;

5.所述输入接口分别与485通信子电路和232通信子电路电性连接,所述主控子电路分别与485通信子电路、232通信子电路以及总线子电路电性连接,所述总线子电路与数码管显示子电路电性连接。

6.进一步地,所述输入接口包括型号为header 10x2a的接口p1。

7.进一步地,所述485通信子电路包括型号均为adm2582ebrwz的第一rs485芯片u5和第二rs485芯片u19,所述第一rs485芯片u5的gnd2引脚、a引脚、y引脚、b引脚、z引脚分别与接口p1的第8引脚、第9引脚、第9引脚、第10引脚、第10引脚依次连接,所述第二rs485芯片u19的gnd2引脚、a引脚、y引脚、b引脚、z引脚分别与接口p1的第18引脚、第19引脚、第19引脚、第20引脚、第20引脚依次连接。

8.进一步地,所述232通信子电路包括型号为max3232eewe的rs232芯片u6,所述rs232芯片u6的r1in引脚、t1out引脚分别与接口p1的第16引脚、第6引脚依次连接。

9.进一步地,所述主控子电路包括型号为stm32f103ret7的主控芯片u9,所述主控芯片u9的pa5引脚、pa9引脚、pa10引脚分别与第一rs485芯片u5的引脚、txd引脚、rxd引脚依次连接,所述主控芯片u9的pc10引脚、pc11引脚、pc12引脚分别与第二rs485芯片u19的txd引脚、rxd引脚、引脚依次连接,所述主控芯片u9的pa2引脚、pa3引脚分别与rs232芯片u6的t1in引脚、r1out引脚依次连接。

10.进一步地,所述总线子电路包括型号均为sn74hc125d的第一总线驱动芯片u12和第二总线驱动芯片u15,所述第一总线驱动芯片u12的a1-a4引脚均与主控芯片u9的pb12引脚连接,所述第一总线驱动芯片u12的ce1引脚、ce2引脚、ce3引脚、oe4引脚分别与主控芯片u9的pb10引脚、pb9引脚、pb8引脚、pb7引脚依次连接;

11.所述第二总线驱动芯片u15的a1-a2引脚均与主控芯片u9的pb12引脚连接,所述第二总线驱动芯片u15的ce1引脚、ce2引脚、a3引脚、a4引脚分别与主控芯片u9的pb6引脚、pb5引脚、pb15引脚、pb13引脚依次连接。

12.进一步地,所述数码管显示子电路包括型号均为bc7275的第一数码管驱动芯片u1、第二数码管驱动芯片u3、第三数码管驱动芯片u7、第四数码管驱动芯片u10、第五数码管驱动新芯片u13和第六数码管驱动芯片u16;

13.所述第一数码管驱动芯片u1的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y1引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接;

14.所述第二数码管驱动芯片u3的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y2引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接;

15.所述第三数码管驱动芯片u7的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y3引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接;

16.所述第四数码管驱动芯片u10的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y4引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接;

17.所述第五数码管驱动新芯片u13的cs引脚、clk引脚、mosi引脚分别与第二总线驱动芯片u15的y1引脚、y4引脚、y3引脚依次连接;

18.所述第六数码管驱动芯片u16的cs引脚、clk引脚、mosi引脚分别与第二总线驱动芯片u15的y2引脚、y4引脚、y3引脚依次连接。

19.进一步地,所述第一数码管驱动芯片u1、第二数码管驱动芯片u3、第三数码管驱动芯片u7、第四数码管驱动芯片u10、第五数码管驱动新芯片u13和第六数码管驱动芯片u16的输出引脚上均设置有数码管。

20.本实用新型的有益效果为:该显示电路相较于现有技术相比能满足实际的使用场景,传输内容更加丰富,尤其是针对专门的用于pciis智能一体化系统。

附图说明

21.图1为本实用新型提出的一种用于pciis智能一体化系统的基于数码管的显示电路结构框图。

22.图2为本实用新型中输入接口电路示意图。

23.图3为本实用新型中485通信子电路示意图。

24.图4为本实用新型中232通信子电路示意图。

25.图5为本实用新型中主控子电路示意图。

26.图6为本实用新型中总线子电路示意图。

27.图7为本实用新型中数码管显示子电路示意图。

具体实施方式

28.下面对本实用新型的具体实施方式进行描述,以便于本技术领域的技术人员理解本实用新型,但应该清楚,本实用新型不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本实用新型的精神和范围内,这些变化是显而易见的,一切利用本实用新型构思的发明创造均在保护之列。

29.下面结合附图详细说明本实用新型的实施例。

30.如图1所示,一种用于pciis智能一体化系统的基于数码管的显示电路,包括输入接口、485通信子电路、232通信子电路、主控子电路、总线子电路以及数码管显示子电路。

31.所述输入接口分别与485通信子电路和232通信子电路电性连接,所述主控子电路分别与485通信子电路、232通信子电路以及总线子电路电性连接,所述总线子电路与数码管显示子电路电性连接。

32.如图2所示,所述输入接口包括型号为header 10x2a的接口p1。

33.如图3所示,所述485通信子电路包括型号均为adm2582ebrwz的第一rs485芯片u5和第二rs485芯片u19,所述第一rs485芯片u5的gnd2引脚、a引脚、y引脚、b引脚、z引脚分别与接口p1的第8引脚、第9引脚、第9引脚、第10引脚、第10引脚依次连接,所述第二rs485芯片u19的gnd2引脚、a引脚、y引脚、b引脚、z引脚分别与接口p1的第18引脚、第19引脚、第19引脚、第20引脚、第20引脚依次连接。

34.如图4所示,所述232通信子电路包括型号为max3232eewe的rs232芯片u6,所述rs232芯片u6的r1in引脚、t1out引脚分别与接口p1的第16引脚、第6引脚依次连接。

35.如图5所示,所述主控子电路包括型号为stm32f103ret7的主控芯片u9,所述主控芯片u9的pa5引脚、pa9引脚、pa10引脚分别与第一rs485芯片u5的re引脚、txd引脚、rxd引脚依次连接,所述主控芯片u9的pc10引脚、pc11引脚、pc12引脚分别与第二rs485芯片u19的txd引脚、rxd引脚、re引脚依次连接,所述主控芯片u9的pa2引脚、pa3引脚分别与rs232芯片u6的t1in引脚、r1out引脚依次连接。

36.如图6所示,所述总线子电路包括型号均为sn74hc125d的第一总线驱动芯片u12和第二总线驱动芯片u15,所述第一总线驱动芯片u12的a1-a4引脚均与主控芯片u9的pb12引脚连接,所述第一总线驱动芯片u12的ce1引脚、ce2引脚、ce3引脚、oe4引脚分别与主控芯片u9的pb10引脚、pb9引脚、pb8引脚、pb7引脚依次连接。

37.所述第二总线驱动芯片u15的a1-a2引脚均与主控芯片u9的pb12引脚连接,所述第二总线驱动芯片u15的ce1引脚、ce2引脚、a3引脚、a4引脚分别与主控芯片u9的pb6引脚、pb5引脚、pb15引脚、pb13引脚依次连接。

38.如图7所示,所述数码管显示子电路包括型号均为bc7275的第一数码管驱动芯片u1、第二数码管驱动芯片u3、第三数码管驱动芯片u7、第四数码管驱动芯片u10、第五数码管驱动新芯片u13和第六数码管驱动芯片u16。

39.所述第一数码管驱动芯片u1的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y1引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接。

40.所述第二数码管驱动芯片u3的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y2引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连

接。

41.所述第三数码管驱动芯片u7的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y3引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接。

42.所述第四数码管驱动芯片u10的cs引脚、clk引脚、mosi引脚分别与第一总线驱动芯片u12的y4引脚、第二总线驱动芯片u15的y4引脚、第二总线驱动芯片u15的y3引脚依次连接。

43.所述第五数码管驱动新芯片u13的cs引脚、clk引脚、mosi引脚分别与第二总线驱动芯片u15的y1引脚、y4引脚、y3引脚依次连接。

44.所述第六数码管驱动芯片u16的cs引脚、clk引脚、mosi引脚分别与第二总线驱动芯片u15的y2引脚、y4引脚、y3引脚依次连接。

45.所述第一数码管驱动芯片u1、第二数码管驱动芯片u3、第三数码管驱动芯片u7、第四数码管驱动芯片u10、第五数码管驱动新芯片u13和第六数码管驱动芯片u16的输出引脚上均设置有数码管。