1.本发明涉及电子器件用基板及其制造方法。

背景技术:

2.以gan或aln为代表的氮化物半导体可以用于使用二维电子气体的高电子迁移率晶体管(hemt)或高耐压电子器件的制作。

3.难以制作使这些氮化物半导体在基板上生长而成的氮化物晶圆,作为基板,使用蓝宝石基板或sic基板。但是,为了抑制大口径化或基板的成本,使用基于气相生长的在硅基板上的外延生长。在基于气相生长的在硅基板上的外延生长膜的制作中,与蓝宝石基板或sic基板相比,能够使用大口径的基板,因此器件的生产率高,在散热性方面是有利的。但是,由于晶格常数差或热膨胀系数差所引起的应力,容易引起翘曲的增大或塑性变形,从而进行基于生长条件或缓和层的应力降低。

4.在高耐压电子器件中,为了提高高耐压特性,需要较厚地堆积外延层。因此,如果较厚地堆积外延层,则作为其基板的硅基板由于与外延层的热膨胀系数的不同而导致在晶圆上产生翘曲。

5.在专利文献1中,作为外延层aln/si(1000ωcm以上)/si(100ωcm以下),公开了将高电阻基板与低电阻基板接合从而控制翘曲形状的电子器件用外延基板。此外,在专利文献2中,作为外延层aln/si(cz低电阻)/si(fz高电阻),公开了将低电阻cz基板与高电阻fz基板接合从而抑制了翘曲的电子器件用外延基板。

6.但是,在用于高耐压电子器件的电子器件用基板中,希望进一步抑制较厚地堆积外延层时的晶圆的翘曲。现有技术文献专利文献

7.专利文献1:国际公开第2011/016219号专利文献2:日本专利公开第2014-192226号公报

技术实现要素:

(一)要解决的技术问题

8.本发明是为了解决上述问题而完成的,其目的在于提供一种在将氮化物半导体膜形成在硅基板上的电子器件用基板中能够抑制翘曲并且也能够用于高耐压产品的电子器件用基板及其制造方法。(二)技术方案

9.为了达到上述目的,本发明提供一种电子器件用基板,其是在单晶硅的接合基板上形成了氮化物半导体膜的基板,其特征在于,所述接合基板是接合了多个单晶硅基板而成的基板,厚度大于2000μm,所述多个单晶硅基板是通过cz法制造的基板,电阻率为0.1ωcm以下。

10.如果是本发明的电子器件用基板,则通过将多个单晶硅基板设为电阻率为0.1ωcm以下的通过cz法制造的基板,进而使接合基板的厚度大于2000μm,从而接合基板的强度大幅增加,因此能够抑制由形成的氮化物半导体膜引起的电子器件用基板的翘曲。因此,特别适合作为用于高耐压产品的电子器件用基板。

11.此时,所述多个单晶硅基板的氧浓度优选为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79)。

12.如果是这样的基板,则能够防止发生单晶硅基板中的滑移。

13.此外,所述接合基板优选是多个cz单晶硅基板经由sio2膜接合而成的基板。

14.如果是这样的基板,则能够缓和由氮化物半导体膜产生的应力,并能够形成更厚的氮化物半导体膜。

15.此外,本发明提供一种电子器件用基板的制造方法,其用于在单晶硅的接合基板上形成氮化物半导体膜,其特征在于,包括以下工序:接合多个单晶硅基板,从而形成厚度大于2000μm的接合基板;以及在所述接合基板上使氮化物半导体膜进行外延生长,使用通过cz法制造的电阻率为0.1ωcm以下的基板作为所述多个单晶硅基板。

16.如果是本发明的电子器件用基板的制造方法,则通过使用电阻率为0.1ωcm以下的多个cz单晶硅基板,进而使接合基板的厚度大于2000μm,从而能够制作强度高的接合基板,因此能够抑制形成氮化物半导体膜时的电子器件用基板的翘曲。因此,特别适合作为用于高耐压产品的电子器件用基板的制造方法。

17.此外,优选使用氧浓度为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79)的基板作为所述多个单晶硅基板。

18.如果是这样的方法,则能够防止发生单晶硅基板中的滑移。

19.此外,在形成所述接合基板的工序中,优选经由sio2膜接合多个cz单晶硅基板。

20.如果是这样的方法,则能够缓和氮化物生长时施加的应力,并能够形成更厚的氮化物半导体膜。(三)有益效果

21.如果是本发明的电子器件用基板及其制造方法,则通过将多个单晶硅基板设为电阻率为0.1ωcm以下的通过cz法制造的基板,进而使接合基板的厚度大于2000μm,接合基板的强度大幅增加,因此能够抑制由形成的氮化物半导体膜引起的电子器件用基板的翘曲。因此,特别适合作为用于高耐压产品的电子器件用基板。

附图说明

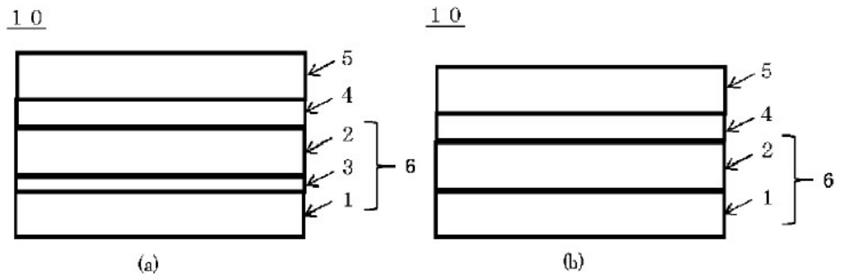

22.图1的(a)是表示在多个单晶硅基板间具有粘接层的情况下的本发明的电子器件用基板的概念图,图1的(b)是表示不具有粘接层的情况下的本发明的电子器件用基板的概念图。

具体实施方式

23.以下,对本发明进行详细说明,但本发明不限于此。

24.在使氮化物半导体在硅基板上进行外延生长而制造的电子器件中,本发明人等深

入研究了对由于热膨胀系数的不同而产生的翘曲进行抑制的电子器件基板及其制造方法,发现通过使用接合了低电阻率的多个cz单晶硅且厚度大于2000μm的基板,能够显著抑制翘曲,从而完成了本发明。

25.[电子器件用基板]即,本发明是在单晶硅的接合基板上形成了氮化物半导体膜的电子器件用基板,其特征在于所述接合基板是接合了多个单晶硅基板而成的基板,厚度大于2000μm,所述多个单晶硅基板是通过cz法制造的基板,电阻率为0.1ωcm以下。

[0026]

本发明的电子器件用基板是在单晶硅的接合基板上形成了氮化物半导体膜的基板。此外,在本发明中,接合基板是接合了通过cz法制造的多个单晶硅基板而成的基板。

[0027]

图1表示本发明的电子器件用基板的概念图。

[0028]

如图1的(a)、(b)所示,本发明的电子器件用基板10由接合了单晶硅基板1和单晶硅基板2(多个单晶硅基板)的接合基板6、和由氮化物构成的氮化物半导体膜(器件层)5构成。多个单晶硅基板间的接合方式没有特别限定,可以设置粘接层。图1的(a)表示在单晶硅基板1和单晶硅基板2之间具有粘接层3的结构。粘接层没有特别限定,例如可以是氧化膜(sio2)。此外,图1的(b)表示在单晶硅基板1和单晶硅基板2之间没有粘接层3的结构。例如,使接合前的氧化膜薄膜化,从而仅氧化膜的氧由于接合后的结合热处理而扩散,能够成为在接合界面部没有氧化膜的结构。像这样,如果单晶硅基板的粘接通过氧化膜进行,则能够缓和氮化物生长时施加的应力。另外,接合的单晶硅基板的片数不限于2片,也可以是3片以上。以下,参照图1,以接合基板为接合了2片单晶硅基板的基板的情况为例进行说明。

[0029]

在本发明中,将单晶硅基板1及单晶硅基板2作为通过cz法制造的单晶硅基板(以下,有时简称为cz单晶基板),设定电阻率为0.1ωcm以下,并设定接合后的接合基板的厚度大于2000μm。通过制成电阻率为0.1ωcm以下的cz单晶基板,单晶硅基板的刚性提高,接合基板的强度增加,因此能够抑制形成了氮化物半导体膜时的电子器件用基板的翘曲。

[0030]

此外,在本发明中,氧浓度优选为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79)。通常,cz单晶与fz单晶不同,其含有氧,由此基板的强度和硬度提高。另一方面,通过使氧浓度为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79),能够防止发生cz单晶基板中的滑移。

[0031]

此外,也可以在单晶硅基板2和器件层5之间形成中间层4。中间层4作为用于进行器件层的结晶性改善或应力的控制而插入的缓冲层发挥作用。上述中间层4能够利用与氮化物半导体膜相同的设备制作,因此优选使用氮化物进行制作。

[0032]

在单晶硅基板2上形成有由例如gan、aln、inn、algan、ingan、alinn等氮化物的薄膜构成的器件层5。在此,在形成了中间层4的情况下,能够在中间层4上形成器件层5。器件层5能够通过movpe法或溅射等气相生长来进行生长。氮化物的薄膜可以为1~20μm,可以根据器件进行设计。

[0033]

例如,对于氮化镓而言,其与si(111)单晶的晶格常数差为17%,热膨胀系数差为116%,在高温下的生长中对薄膜或基板施加应力。此外,由于在生长中被加热到1000℃以上,因此在对晶圆施加应力时,不会脆性破坏而展现出延展性,并且产生位错而塑性变形。

[0034]

如果是本发明的电子器件用基板,则通过使基板的厚度足够厚,形成电阻率为0.1ωcm以下的cz单晶基板,能够防止生长中的塑性变形,减小翘曲。从电子器件用基板的翘曲

的观点出发,电阻率的下限没有特别限定,可以适当决定,可以是大于0ωcm的值。此外,通过使接合基板的厚度大于2000μm,接合基板的强度增加,因此能够进一步抑制由形成的氮化物半导体膜引起的电子器件用基板的翘曲。因此,特别适合作为用于高耐压产品的电子器件用基板。从接合基板的强度的观点出发,厚度的上限没有特别限定,可以适当决定,但只要达到4800μm即足够。

[0035]

[电子器件用基板的制造方法]此外,本发明是在单晶硅的接合基板上形成氮化物半导体膜的电子器件用基板的制造方法,其特征在于,包括以下工序:接合多个单晶硅基板,从而形成厚度大于2000μm的接合基板;以及在所述接合基板上使氮化物半导体膜进行外延生长,使用通过cz法制造的电阻率为0.1ωcm以下的基板作为所述多个单晶硅基板。

[0036]

在本发明的制造方法中,首先接合多个单晶硅基板,形成厚度大于2000μm的接合基板。在此,在本发明的制造方法中,作为多个单晶硅基板,使用硬且强度优异的、通过cz法制造的电阻率为0.1ωcm以下的基板。

[0037]

此外,作为多个单晶硅基板,优选使用氧浓度为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79)的基板。通过使用氧浓度为3.0

×

10

17

~1

×

10

18

atoms/cm3(astm’79)的基板,能够防止发生cz单晶基板中的滑移。

[0038]

接合多个单晶硅基板的方法没有特别限定,优选使用氧化膜进行贴合。此外,使接合前的氧化膜薄膜化,从而在接合后通过结合热处理而仅使氧化膜的氧扩散,能够成为在接合界面部没有氧化膜的结构。像这样,通过利用氧化膜进行单晶硅基板的粘接,能够缓和氮化物生长时施加的应力。

[0039]

此外,多个单晶硅基板的各自的厚度优选为1000μm以上。为了制作超过2000μm厚度的接合基板,需要准备装置类的夹具等,但通过贴合2片1000μm以上厚度的单晶硅基板,能够简单地制作超过2000μm厚度的接合基板。

[0040]

接着,在如上述方式制造的接合基板上使氮化物半导体膜进行外延生长。在此,能够在氮化物半导体膜的生长之前形成中间层。通过在氮化物生长时形成中间层并加入适当的缓冲层,能够在冷却后控制由热膨胀系数差和晶格常数差引起的来自薄膜的应力,并且通过加厚基板,能够防止高温生长中的塑性变形,进而能够制造翘曲较小的晶圆。为了简化工序,优选使用氮化物制作中间层。

[0041]

如果是这样的制造方法,则通过使用电阻率为0.1ωcm以下的多个cz单晶硅基板,进而使接合基板的厚度大于2000μm,从而能够制作强度高的接合基板,因此能够抑制形成了氮化物半导体膜时的电子器件用基板的翘曲。因此,特别适合作为用于高耐压产品的电子器件用基板的制造方法。实施例

[0042]

以下,示出实施例和比较例,更具体地说明本发明,但本发明不限于下述的实施例。

[0043]

(实施例1)准备电阻率为0.007ωcm、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz单晶硅基板的厚度为1100μm的2片晶圆(直径150mm、结晶方位(111))。

接着,如以下方式,制作了图1的(a)所示的电子器件用基板。将cz单晶硅基板(基底晶圆)1和双面研磨后的cz单晶硅基板(接合晶圆)2进行热氧化,分别形成了厚度100nm的sio2膜。然后,经过结合工序,在1150℃下进行了2小时的结合热处理。之后,作为氧化膜去除,浸渍在10%hf中而去除表面氧化膜,制作出得到的厚度2200μm(1100μm基板2片+接合层200nm)的接合基板。然后,使所制作的接合基板在movpe炉中外延生长8μm厚的gan(中间层:4μm、器件层4μm)。外延生长后的晶圆的翘曲为10μm。

[0044]

(比较例1)在比较例1中,除了变更了cz单晶硅基板的厚度以外,与实施例1同样地制作基板。分别准备了:电阻率为0.007ωcm、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz单晶硅基板的厚度为500μm的2片晶圆(直径150mm、结晶方位(111));以及,电阻率为0.007ωcm、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz单晶硅基板的厚度为625μm的2片晶圆(直径150mm、结晶方位(111))。将cz单晶硅基板(基底晶圆)进行热氧化(厚度100nm),将双面研磨后的cz单晶硅基板(接合晶圆)进行热氧化(厚度100nm),经过结合工序,在1150℃下进行2小时的结合热处理。之后,作为氧化膜去除,浸渍在10%hf中而去除表面氧化膜,制作出得到的厚度1000μm(500μm基板2片+接合层200nm)、1250μm(625μm基板2片+接合层200nm)的结合基板。然后,分别使各结合基板在相同的movpe炉中外延生长出8μm厚的gan(中间层:4μm、器件层4μm)。基板厚度1250μm的晶圆的翘曲为20μm。在基板厚度1000μm的晶圆中,翘曲为50μm。

[0045]

(比较例2)在比较例2中,制作了将fz单晶硅基板和cz单晶硅基板贴合的结合基板,并且在制作的结合基板上生长外延层。分别准备了:电阻率为0.007ωcm、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz单晶硅基板的厚度为625μm的晶圆(直径150mm、结晶方位(111));电阻率为0.007ωcm、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz单晶硅基板的厚度为675μm的晶圆(直径150mm、结晶方位(111));电阻率为5000ωcm、氮浓度为8

×

10

14

atoms/cm3的fz单晶硅基板的厚度为625μm的晶圆(直径150mm、结晶方位(111));以及,电阻率为5000ωcm、氮浓度为8

×

10

14

atoms/cm3的fz单晶硅基板的厚度为675μm的晶圆(直径150mm、结晶方位(111))。将cz单晶硅基板(基底晶圆)进行热氧化(厚度100nm),将双面研磨后的fz单晶硅基板(接合晶圆)进行热氧化(厚度100nm),经过结合工序,在1150℃下进行2小时的结合热处理。之后,作为氧化膜去除,浸渍在10%hf中而去除表面氧化膜,制作出得到的厚度1250μm(625μm基板2片+接合层200nm)、1350μm(675μm基板2片+接合层200nm)的结合基板。然后,分别使各结合基板在相同的movpe炉中外延生长出8μm厚的gan(中间层:4μm、器件层4μm)。基板厚度1250μm的晶圆的翘曲为25μm。在基板厚度1350μm的晶圆中,翘曲为15μm。

[0046]

(比较例3)在比较例3中,制作了将fz单晶硅基板彼此贴合的结合基板,并且在制作的结合基板上生长外延层。分别准备了:电阻率为5000ωcm、氮浓度为8

×

10

14

atoms/cm3的fz单晶硅基板的厚度为625μm的2片晶圆(直径150mm、结晶方位(111));以及,电阻率为5000ωcm、氮浓度为8

×

10

14

atoms/cm3的fz单晶硅基板的厚度为675μm的2片晶圆(直径150mm、结晶方位(111))。将fz单晶硅基板(基底晶圆)1进行热氧化(厚度100nm),将双面研磨后的fz单晶硅

基板(接合晶圆)2进行热氧化(厚度100nm),经过结合工序,在1150℃下进行2小时的结合热处理。之后,作为氧化膜去除,浸渍在10%hf中而去除表面氧化膜,制作出得到的厚度1250μm(625μm基板2片+接合层200nm)、1350μm(675μm基板2片+接合层200nm)的结合基板。然后,分别使各结合基板在相同的movpe炉中外延生长出8μm厚的gan(中间层:4μm、器件层4μm)。基板厚度1250μm的晶圆的翘曲为30μm。在基板厚度1350μm的晶圆中,翘曲为20μm。

[0047]

(比较例4)在比较例4中,使cz单晶硅基板的厚度与比较例1相比更薄,与比较例1同样地制作基板。准备了:电阻率为0.007ωcm以下、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz硅基板且基板的厚度为400μm的一晶圆(直径150mm、结晶方位(111));以及,是电阻率为0.007ωcm以下、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz硅基板且基板的厚度为400μm的另一晶圆(直径150mm、结晶方位(111))。将cz单晶硅基板(基底晶圆)1进行热氧化(厚度50nm),将双面研磨后的cz单晶硅基板(接合晶圆)2进行热氧化(厚度50nm),经过结合工序,在1150℃下进行2小时的结合热处理。然后,作为氧化膜去除,浸渍在10%hf中而去除表面氧化膜,制作出得到的厚度800μm(400μm基板2片+接合层100nm)的结合基板。然后,使基板在movpe炉中外延生长出8μm厚的gan(中间层:4μm、器件层4μm)。晶圆的翘曲为200μm。

[0048]

(比较例5)在比较例5中,不进行cz单晶硅基板的贴合,而使外延层生长。准备了电阻率为0.007ωcm以下、氧浓度为7

×

10

17

atoms/cm3(astm’79)的cz硅基板且基板的厚度为625μm的晶圆(直径150mm、结晶方位(111))。然后,使基板在movpe炉中外延生长出8μm厚的gan(中间层:4μm、器件层4μm)。晶圆的翘曲为300μm。

[0049]

根据上述结果,如实施例1所示,在使电阻率为0.1ωcm以下的cz单晶硅基板贴合,并使贴合后的接合基板的厚度大于2000μm的情况下,在形成了氮化物半导体膜的情况下,晶圆的翘曲最小。另一方面,可知,即使使用具有相同电阻率的cz单晶硅基板,在如比较例1、4、5那样基板的厚度为2000μm以下的情况下,晶圆的翘曲变得更大。此外,从比较例1和比较例2、3的比较可知,即使是相同的基板厚度,如果使用比cz单晶硅基板软的fz单晶硅基板,则晶圆的翘曲变得更大。

[0050]

另外,本发明并不限于上述实施方式。上述实施方式为示例说明,凡具有与本发明的权利要求书所记载的技术思想实质上相同的构成并产生相同作用效果的任何方案都包含在本发明的技术范围内。