1.本实用新型涉及一种蜂鸣器电路领域,具体涉及一种电磁式蜂鸣器低电压启动电路和蜂鸣器驱动芯片。

背景技术:

2.如图6所示,传统的电磁式蜂鸣器驱动电路,为了防止蜂鸣器电磁线圈在导通时过度拉低芯片内部的供电,就在蜂鸣器nmos驱动管与内部电路供电信号线vcc之间加入二极管d1,电路的供电需要通过二极管d1,二极管d1可以看作蜂鸣器电路的启动器件,电源通过二极管有比较大的压降,约为0.5~0.7v,一般蜂鸣器要求当电源在1.5v以下就要工作,当电源在1.5v时,电源经二极管降压后给振荡器等电路供电电压约为1v,在这个电压下,振荡器很难工作或者工作不正常。

技术实现要素:

3.本实用新型提供一种电磁式蜂鸣器低电压启动电路,在电源电压比较低时,以解决振荡器难以正常工作的问题。

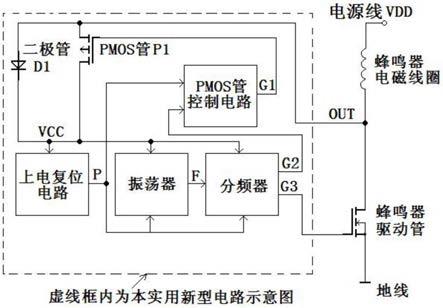

4.为解决上述技术问题,本实用新型提供一种电磁式蜂鸣器低电压启动电路,如图1所示,包括二极管d1、pmos管p1、pmos管控制电路、上电复位电路、振荡器,分频器。其中,二极管d1正极连接蜂鸣器驱动管输出out,二极管d1负极连接信号线vcc,pmos管p1栅极连接pmos管控制电路输出g1,pmos管p1源极连接蜂鸣器驱动管输出out,pmos管p1漏极连接信号线vcc,pmos管p1的衬底悬空或者选择性连接信号线vcc和蜂鸣器驱动管输出out中电压较高的电位,或者pmos管p1的衬底连接信号线vcc,信号线vcc给pmos管控制电路、上电复位电路、振荡器、分频器供电,上电复位电路输出p分别连接pmos管控制电路、振荡器、分频器的输入,振荡器输出f连接到分频器的输入,分频器输出g2连接pmos管控制电路输入,分频器输出g3连接到蜂鸣器驱动管栅极。

5.如图1所示,当电路刚上电时,通过蜂鸣器电磁线圈和二极管d1对信号线vcc进行充电,上电复位电路输出信号p使得分频器输出g3为低电平,分频器输出g3为低电平使得蜂鸣器驱动管截止,上电复位电路输出信号p也使得pmos管控制电路输出信号g1为低电平,pmos管控制电路输出信号g1为低电平使得pmos管p1导通,从而降低二极管d1两端的压降,二极管d1两端的压降变小,信号线vcc电压变高,有助于振荡器及分频器的正常工作。从上电开始到蜂鸣器驱动管导通前,pmos管p1始终导通或者导通一段时间,以完成对信号线vcc的充电,在蜂鸣器驱动管导通一次以后,可始终关闭pmos管p1,也可以让pmos管控制电路输出g1在蜂鸣器驱动管截止时使得pmos管p1导通,pmos管控制电路输出g1在蜂鸣器驱动管导通时使得pmos管p1截止,这样工作若干个周期,或者一直工作下去,具体由应用环境而定。

6.优选的,所述二极管至少为一个。

7.优选的,所述振荡器可以不受上电复位电路输出p的控制。

8.优选的,所述分频器输出g2、分频器输出g3可以是同一个信号线。

9.优选的,所述振荡器频率合适时可以去除分频器,分频器输出g2、分频器输出g3均由振荡器输出。

10.优选的,pmos管p1的衬底接信号线vcc或者选择性连接信号线vcc和蜂鸣器驱动管输出out中电压较高的电位,或者悬空。

11.本实用新型带来的有益效果:本实用新型提供的一种电磁式蜂鸣器低电压启动电路,通过在蜂鸣器驱动管截止时打开电源线与内部供电信号线之间的pmos管,以提高内部电路模块的供电电压,起到电路低电压启动并正常工作的作用。该电路具有成本低和工作电压低的优点。

附图说明

12.图1是本实用新型的电磁式蜂鸣器低电压启动电路的结构示意图。

13.图2是根据本实用新型第一实施例的电磁式蜂鸣器低电压启动电路示意图。

14.图3是根据本实用新型第一实施例的电磁式蜂鸣器低电压启动电路时序示意图。

15.图4是根据本实用新型第二实施例的电磁式蜂鸣器低电压启动电路示意图。

16.图5是根据本实用新型第二实施例的电磁式蜂鸣器低电压启动电路时序示意图。

17.图6背景技术示意图。

具体实施方式

18.为使本实用新型的目的、技术方案和优点更加清楚,以下结合附图及具体实施例,对本实用新型作进一步地详细说明。

19.如图1所示,本实用新型提供的一种电磁式蜂鸣器低电压启动电路,包括二极管d1、pmos管p1、pmos管控制电路、上电复位电路、振荡器,分频器。其中,二极管d1正极连接蜂鸣器驱动管输出out,负极连接信号线vcc,pmos管p1栅极连接pmos管控制电路输出g1,源极连接蜂鸣器驱动管输出out,漏极连接信号线vcc,信号线vcc给pmos管控制电路、上电复位电路、振荡器、分频器供电,上电复位电路输出p分别连接pmos管控制电路、振荡器、分频器的输入,振荡器输出f连接到分频器的输入,分频器输出g2连接pmos管控制电路输入,分频器输出g3连接到蜂鸣器驱动管栅极。在实际应用中,振荡器可以不受上电复位电路输出p的控制,分频器输出g2、分频器输出g3可以是同一个信号线,pmos管p1的衬底接信号线vcc或者选择性连接信号线vcc和蜂鸣器驱动管输出out中电压较高的电位,或者悬空。

20.本实用新型的第一实施例,如图2所示:包括二极管d1、pmos管p1、pmos管控制电路、上电复位电路、振荡器,分频器。其中,二极管d1正极连接蜂鸣器nmos驱动管输出out,二极管d1负极连接信号线vcc,pmos管p1栅极连接pmos管控制电路输出g1,pmos管p1源极连接蜂鸣器nmos驱动管输出out,pmos管p1漏极连接信号线vcc,pmos管p1的衬底连接信号线vcc,信号线vcc给pmos管控制电路、上电复位电路、振荡器、分频器供电,上电复位电路输出p分别连接pmos管控制电路、振荡器、分频器的输入,振荡器输出f连接到分频器的输入,分频器输出g2连接pmos管控制电路输入,分频器输出g3连接到蜂鸣器nmos驱动管栅极。信号线vcc外接电容c1,外接电容c1的另一端接地线。

21.本实用新型的第一实施例其中的一种工作时序如图3所示,结合图2,电源上电时,通过蜂鸣器电磁线圈和二极管d1对信号线vcc进行充电,上电复位电路开始工作,上电复位

电路输出p为高电平,上电复位电路输出p对振荡器和分频器进行复位,分频器输出g2为低电平,上电复位电路输出p为高电平时pmos管控制电路输出g1为低电平,使得pmos管p1导通,pmos管p1对外挂电容c1进行充电,信号线vcc电位进一步上升,为振荡器、分频器等内部电路提供足够高的电压以保证电路的正常工作,经过一段时间,上电复位电路输出p由高电平变为低电平,pmos管控制电路输出g1维持低电平不变,振荡器和分频器开始工作,再经过一段时间,分频器输出g2为高电平,分频器输出g2的高电平使得mos管控制电路输出g1翻转为高电平,pmos管p1截止,再经过一段时间分频器输出g3为高电平,蜂鸣器驱动管开始工作。

22.本实用新型的第一实施例的其他工作时序中,上电复位输出p复位期间可以为低电平,而不一定如图3所示上电复位输出p复位期间为高电平,分频器输出g2在复位期间可以为高电平,而不一定如图3所示分频器输出g2在复位期间为低电平,但起到的作用时一样的,即上电复位期间pmos管p1导通,蜂鸣器驱动管导通时pmos管p1导通截止。

23.本实用新型的第二实施例如图4所示:包括二极管d1、pmos管p1、pmos管p2、pmos管p3、pmos管控制电路、上电复位电路、振荡器,分频器。其中,二极管d1正极连接蜂鸣器nmos驱动管输出out,二极管d1负极连接信号线vcc,pmos管p1栅极连接pmos管控制电路输出g1,pmos管p1源极连接蜂鸣器nmos驱动管输出out,pmos管p1漏极连接信号线vcc,pmos管p1衬底连接信号线b1,pmos管p2栅极连接信号线vcc,pmos管p2源极连接蜂鸣器nmos驱动管输出out,pmos管p2漏极连接信号线b1,pmos管p2衬底连接信号线b1,pmos管p3栅极连接蜂鸣器nmos驱动管输出out,pmos管p3源极连接信号线vcc,pmos管p3漏极连接信号线b1,pmos管p3衬底连接信号线b1,信号线vcc给pmos管控制电路、上电复位电路、振荡器、分频器供电,上电复位电路输出p分别连接pmos管控制电路、分频器的输入,振荡器输出f连接到分频器的输入,分频器输出g2连接pmos管控制电路输入,分频器输出g2连接到蜂鸣器nmos驱动管栅极。信号线vcc外接电容c1,外接电容c1的另一端接地线。

24.本实用新型的第二实施例其中的一种工作时序如图5所示,结合图4,图中复位周期是指上电复位周期,在上电复位周期,pmos管控制电路输出g1为低电平,pmos管p1导通,pmos管p1对外挂电容c1进行充电,信号线vcc电位进一步上升,为振荡器、分频器等内部电路提供足够高的电压以保证电路的正常工作,在分频器工作期间,分频器输出g2为低电平时,pmos管p1导通,pmos管p1对外挂电容c1进行充电,分频器输出g2为高电平时,pmos管p1截止,如此往复。

25.本实用新型的第二实施例的其他工作时序中,在分频器工作期间,pmos管p1可以只在分频器工作第一周期分频器输出g2为低电平时导通,也可以只在分频器工作前若干个周期分频器输出g2为低电平时导通,具体视电容大小及应用条件而定。

26.综上所述,本实用新型提供的一种电磁式蜂鸣器低电压启动电路,通过控制电源线与内部供电信号线之间的pmos管的导通时间,来降低电源线与内部供电信号线之间的电压差,使得蜂鸣器可以在比较低的电压下正常工作,本实用新型电路具有工作电压低,成本低的优点。

27.以上所述仅为本实用新型的实施例而已,并不用于限制本实用新型,对于本领域的技术人员来说,本实用新型可以有各种更改和变化。凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的权利要求范围之内。