1.本发明涉及一种外延生长装置及外延晶片的制造方法。

背景技术:

2.在代表性的半导体晶片即硅晶片上形成有硅外延层的外延硅晶片用作如下基板,即,用来制作mosfet(metal-oxide-semiconductor field-effect transistor:金属氧化层半导体场效应晶体管)、dram(dynamic random access memory:动态随机存取存储器)等各式各样的半导体器件的基板。

3.图1中示出使外延层气相生长在半导体晶片的表面上的单片式外延生长装置的一例。该图中所示的外延层生长装置100具有工艺腔室10,所述工艺腔室10具有上部拱顶11、下部拱顶12及拱顶安装体13。上部拱顶11及下部拱顶12是由透明的石英构成,通过夹具14安装在拱顶安装体13。

4.在上述工艺腔室10的内壁配置有用于保护拱顶安装体13的环状的上部衬垫15及下部衬垫16,这些衬垫分别由石英构成。然后,在上部衬垫15与下部衬垫16之间的与工艺腔室10对置的位置,设置有对工艺腔室10内部供给反应气体等的气体供给口17及排出未反应气体等的气体排出口18。

5.并且,在工艺腔室10的内部,设置有载置半导体晶片w的基座4。基座4构成为,通过与可转动的支承轴7的中心柱7a连接的支承臂7b嵌合支承其下表面的外周部,并且与支承臂7b一起旋转。基座4构成为将石墨碳(石墨)作为母材且在其表面实施了sic涂敷,在基座4的表面上形成有收容并载置半导体晶片w的锪孔部。

6.在上述基座4及支承臂7b形成有贯穿孔,在各贯穿孔中插入有用于支承半导体晶片w的背面并使其升降的升降销5。关于升降销5,以升降轴6支承其基端,并且通过使升降轴6在上下方向上移动而使其升降。

7.并且,在基座4的外周配置有用于预热从气体供给口17供给至载置在基座4上的半导体晶片w表面的反应气体的环状的预热环60。预热环60构成为将石墨碳(石墨)作为母材且在其表面实施了碳化硅(sic)涂敷,并且预热环60被向下部衬垫16的开口部突出的支承部16a支承。

8.图2中示出图1所示的外延生长装置100的晶片运入口附近的图。另外,关于晶片运入口,在从上面观察图1所示的外延生长装置100时,设置在与设置有气体供给口17及气体排出口18的位置,在圆周方向上偏离大致90

°

的位置。

9.如图2所示,与外延装置100的工艺腔室10相邻地,设置有用于将半导体晶片w输送至工艺腔室10内部的输送腔室20。然后,输送腔室20与工艺腔室10经由大致长方体的狭缝构件21连通。

10.狭缝构件21上划分有连通输送腔室20的内部与工艺腔室10的内部的连通路22。并且,在狭缝构件21的输送腔室20侧,设置有将工艺腔室10内部密闭的狭缝阀23。

11.半导体晶片w如以下载置在基座4上。首先,通过支承轴7使基座4下降。接着,在开

启输送腔室20内的狭缝阀23然后,使载置在输送板b上的半导体晶片w通过连通路22,并将其从晶片运入口24运入至工艺腔室10内部,最后配置在基座4的上方。

12.接着,通过升降轴6使升降销5上升,支承半导体晶片w的背面。然后,使输送板b从工艺腔室10退出,关闭狭缝阀23。然后,通过支承轴7使基座4上升,将半导体晶片w载置在基座4上,使基座4上升至规定高度的位置,从气体供给口17导入反应气体,从而使外延层生长在半导体晶片w的表面上。

13.外延层的生长结束,将所得到的外延晶片从工艺腔室10运出时,进行与上述顺序相反的顺序。

14.如上所述,预热环60是被下部衬垫16的突出部16a支承,但是这些预热环60与下部衬垫16的构成材料不同。因此,在使腔室10内部升温或降温时,在预热环60与下部衬垫16的突出部16a之间发生由热膨胀系数差引起的摩擦,从而存在从这些构件起尘,粒子附着在半导体晶片w表面的问题。

15.伴随近几年的半导体器件的细微化

·

高集成化,要求降低晶体缺陷及附着在晶片表面上的粒子。因此,需要抑制如上所述的预热环60与下部衬垫16间的起尘。

16.因此,在专利文献1中记载有在预热环的下部设置突出部并固定在下部衬垫,在使腔室内部升温或降温时,防止预热环与下部衬垫间的起尘的技术。

17.现有技术文献专利文献专利文献1:国际公开第2015/076487号。

技术实现要素:

18.发明所要解决的技术问题但是,专利文献1中所记载的技术中,在使腔室内部升温或降温时,在预热环与下部衬垫之间施加由热膨胀系数差引起的力,而有可能损坏预热环。

19.因此,本发明的目的在于提供一种能够在不损坏预热环的前提下抑制预热环与下部衬垫之间的起尘的外延生长装置。

20.用于解决技术问题的方案解决上述问题的本发明如下所示。

21.[1]一种外延生长装置,使外延层气相生长在半导体晶片的表面上,其特征在于具备:腔室;配置在所述腔室内壁的环状的上部衬垫及下部衬垫;设置在所述腔室内部且用于载置所述半导体晶片的基座;及载置在向所述下部衬垫的开口部突出的支承部上,并且配置在所述基座的外周的预热环,所述半导体晶片在所述基座下降的状态下,从设置在所述腔室的晶片运入口运入至所述腔室内部,并经由所述下部衬垫的支承部及所述预热环的下方,最后载置在所述基座上,所述预热环构成为,在所述半导体晶片被运入至所述腔室内部并载置在所述基座

上为止的输送路径中所述半导体晶片所通过的区域的正上方的至少一部分区域,不被所述支承部支承。

[0022]

[2]根据所述[1]所述的外延生长装置,其中,在所述至少一部分区域,没有设置所述支承部。

[0023]

[3]根据所述[1]所述的外延生长装置,其中,在所述至少一部分区域,在所述预热环与所述支承部之间设置有空隙。

[0024]

[4]根据所述[1]~[3]中任一项所述的外延生长装置,其中,所述至少一部分区域是如下区域:在从上面观察所述外延生长装置时,所述支承部的整周中,相对于所述半导体晶片的输送方向的中心角为

±

10

°

~90

°

。

[0025]

[5]根据所述[1]~[4]中任一项所述的外延生长装置,其中,所述至少一部分区域为所有区域。

[0026]

[6]一种外延晶片的制造方法,其特征在于,对所述[1]~[5]中任一项所述的外延生长装置供给反应气体,使外延层生长在半导体晶片上而得到外延晶片。

[0027]

[7]根据所述[6]所述的外延晶片的制造方法,其中,所述半导体晶片为硅晶片。

[0028]

发明效果根据本发明,能够在不损坏预热环的前提下抑制预热环与下部衬垫之间的起尘。

附图说明

[0029]

图1是外延生长装置的一例的示意图。

[0030]

图2是表示在外延生长装置的晶片运入口附近的结构的示意图。

[0031]

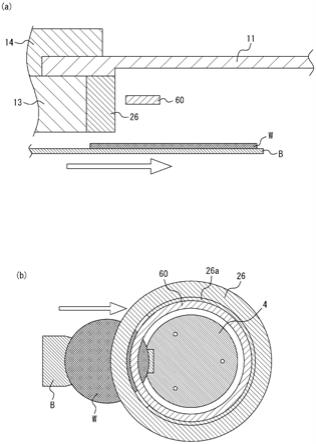

图3是以往的外延生长装置的预热环周围的结构的示意图,图3(a)是沿晶片输送方向的剖视图,图3(b)是俯视图。

[0032]

图4是基于本发明的外延生长装置的预热环周围的结构的一例的示意图,图4(a)是沿晶片输送方向的剖视图,图4(b)是俯视图。

[0033]

图5是基于本发明的外延生长装置的下部衬垫的一例的示意图。

[0034]

图6是基于本发明的外延生长装置的下部衬垫的另一个例子的示意图。

[0035]

图7是基于本发明的外延生长装置的下部衬垫的又一个例子的示意图。

[0036]

图8是基于本发明的外延生长装置的下部衬垫的再一个例子的示意图。

[0037]

图9是基于本发明的外延生长装置的下部衬垫的另一个例子的示意图。

具体实施方式

[0038]

(外延生长装置)以下参考附图,对基于本发明的外延生长装置进行说明。基于本发明的外延生长装置是使外延层气相生长在半导体晶片的表面上的外延生长装置,其具备:腔室;配置在该腔室内壁的环状的上部衬垫及下部衬垫:设置在腔室内部且用于载置半导体晶片的基座;及载置在向下部衬垫的开口部突出的支承部上,并且配置在基座的外周的预热环。然后,半导体晶片构成为,在基座下降的状态下,从设置在腔室的晶片运入口运入至腔室内部,并经由下部衬垫的支承部及预热环的下方,最后载置在基座上。在此,预热环的特征在于构成

为,在半导体晶片被运入至腔室内部并载置在基座上为止的输送路径中半导体晶片w所通过的区域的正上方的至少一部分区域,不被支承部支承。

[0039]

图3中示出以往的外延生长装置100的预热环60周围的结构的示意图,图3(a)是沿晶片输送方向的剖视图,图3(b)是俯视图。

[0040]

如图3(a)所示,环状的预热环60遍及其整周被下部衬垫16的支承部16a支承。

[0041]

然后,如图3(b)所示,半导体晶片w,在从外延生长装置100的晶片运入口24运入并载置在基座4上为止的输送路径,通过预热环60的下方。

[0042]

在这种状况下,当使腔室10内部升温或降温时,如果在预热环60与下部衬垫16的支承部16a之间发生摩擦而起尘,则有时在通过预热环60下方的半导体晶片w的表面上会附着粒子。

[0043]

因此本发明的发明人,对抑制上述粒子附着的原因即预热环60与下部衬垫16的支承部16a之间的起尘的方法进行了深入研究。结果,想到在将半导体晶片w从晶片运入口24导入并载置在基座4上为止的输送路径中半导体晶片w所通过的区域(以下,也简单称为“半导体晶片的通过区域”。)的正上方的至少一部分区域,将预热环60构成为不被下部衬垫16的支承部16a支承,从而完成了本发明。

[0044]

图4是基于本发明的外延生长装置的预热环周围的结构的一例的示意图,图4(a)是沿晶片输送方向的剖视图,图4(b)是俯视图。在图4(a)所示的结构中,预热环60构成为,在半导体晶片w的通过区域的正上方的所有区域,不被下部衬垫26的支承部26a支承。

[0045]

图5中示出图4(a)所示的下部衬垫26。如该图所示,在半导体晶片w的通过区域的正上方的所有区域并没有设置下部衬垫26的环状的支承部26a。由此,在半导体晶片w的通过区域的正上方,能够防止预热环60与下部衬垫26的支承部26a之间的起尘。另外,在图5所示的下部衬垫26,支承部26a的整周之中,只有相对于半导体晶片w的输送方向的中心角

±

40

°

的区域没有设置。

[0046]

通过将下部衬垫26的支承部26a构成为如上所述,如图4(b)所示,在将半导体晶片w输送至基座4上时,在输送路径的正上方,由于不会发生预热环60与下部衬垫26的支承部26a之间的起尘,因此能够抑制粒子附着在半导体晶片w的表面。

[0047]

并且,在使外延层生长在半导体晶片w的表面上时,如果在预热环60与下部衬垫26之间沉积多晶硅,则在输送半导体晶片w时,有时会掉到半导体晶片w表面,但通过图5所示的下部衬垫26,能够防止上述多晶硅的沉积。

[0048]

另外,在图5所示的下部衬垫26中半导体晶片w的通过区域的正上方的所有区域,预热环60不被支承部26a支承,但是也可以构成为只有在一部分的区域,预热环60不被支承部26a支承。

[0049]

图6中示出基于本发明的外延生长装置的下部衬垫的另一个例子。在图6(a)所示的下部衬垫36,环状的支承部36a的整周之中,只有相对于半导体晶片w的输送方向的中心角

±

15

°

的区域没有设置。在这种情况下,与图3所示的使用以往的下部衬垫16的情况相比,也能够抑制预热环60与下部衬垫36之间的起尘而抑制粒子附着在半导体晶片w的表面。并且,与图5所示的下部衬垫26相比,能够防止由预热环60的自重引起的下垂(变形)。上述中心角优选设为

±

10

°

~90

°

,更优选设为

±

10

°

~45

°

。

[0050]

并且,在图6(b)所示的下部衬垫46之中,虽与图5同样地,在中心角

±

40

°

的部分没

有设置支承部46a,但是在该范围内,局部地设置有支承部46a。由此,与图5所示的下部衬垫26相比,能够更稳定地支承预热环60。

[0051]

另外,在图4~6所示的下部衬垫26、36、46,在从上面观察时完全去除了没有支承预热环60的支承部26a、36a、46a的部分,但是无需一定以这种方式构成。

[0052]

即,也可以如图7所示的下部衬垫56,在其支承部56a的

±

40

°

的区域的表面设置凹部56b,在预热环60与支承部56a之间设置空隙。即使在该情况下,在半导体晶片w的通过区域的正上方,也能够防止预热环60与下部衬垫56之间的起尘。

[0053]

并且,如图6所示的下部衬垫36、46,能够仅在输送路径的上方的区域的一部分的区域,在支承部设置凹部。具体而言,在图8所示的下部衬垫66,环状的支承部66a的整周之中,在中心角

±

15

°

的部分设置有凹部66b。并且,在图9所示的下部衬垫76,与图7同样地在支承部76a的中心角

±

40

°

的部分断断续续地设置有凹部76b。

[0054]

如此,将预热环构成为在半导体晶片的输送区域的正上方的至少一部分区域,不被下部衬垫的支承部支承,从而能够抑制预热环与下部衬垫的支承部之间的起尘。

[0055]

从以上说明可以明显看出,基于本发明的外延生长装置在支承预热环的下部衬垫的支承部的结构上具有特征,其他的结构并无限定,能够适当地使用以往的结构。

[0056]

(外延晶片的制造方法)基于本发明的外延晶片的制造方法的特征在于,对上述基于本发明的外延生长装置供给反应气体,使外延层生长在半导体晶片上而得到外延晶片。

[0057]

如上所述,在基于本发明的外延生长装置中半导体晶片w的通过区域的正上方的至少一部分区域,将预热环构成为在半导体晶片的输送区域的正上方的至少一部分区域,不被下部衬垫的支承部支承,能够抑制预热环与下部衬垫之间的起尘。因此,对上述基于本发明的外延生长装置供给反应气体而在半导体晶片上形成外延层,由此能够制造抑制粒子的附着的外延晶片。

[0058]

作为外延晶片的基板的半导体晶片并无特别限定,能够良好地使用硅晶片,能够使硅外延层适当地生长在硅晶片上。半导体晶片的直径并无特别限定,能够设为150mm以上,具体地,能够设为200mm、300mm、450mm等。

[0059]

产业上的可利用性根据本发明,由于能够在不损坏预热环的前提下抑制预热环与下部衬垫之间的起尘,因此有用于半导体晶片制造业。

[0060]

附图标记说明4-基座,5-升降销,6-升降轴,7-支承轴,7a-中心柱,7b-支承臂,10-工艺腔室,11-上部拱顶,12-下部拱顶,13-拱顶安装体,14-夹具,15-上部衬垫,16、26、36、46、56、66、76-下部衬垫,16a、26a、36a、46a、56a、66a、76a-支承部,17-气体供给口,18-气体排出口,20-输送腔室,21-狭缝材料,22-连通路,23-狭缝阀,24-晶片运入口,56b、66b、76b-凹部,60-预热环,100-外延生长装置,b-输送板,w-半导体晶片。