1.本发明涉及芯片设计领域,特别是涉及一种音频编码译码标准芯片单元及多通道音频编码译码器芯片。

背景技术:

2.音频编码译码器包含数模转换器与模数转换器,在不同的应用场合下,两者的数量与组合很多,仅以音响为例,最低端的音箱只有一个喇叭,因此只需要单通道的数模转换器与单通道的模数转换器即可,常见的电脑音箱有两个喇叭,需要两通道的数模转换器与两通道的模数转换器,汽车上的音箱最少是四通道的数模转换器与若干通道的模数转换器。音频编解码器设计厂家,为了上述不同的需求,通常做法如下:设计一些典型通道配置的音频编码译码器,例如分别设计生产两通道的音频编码译码器芯片、四通道的音频编码译码器、六通道音频编码译码器。然后在设计完成的上述芯片上通过把一些音频通道端口不进行封装的方式,裁剪出来一些音频通道数量更少的芯片产品,例如把原始设计为两通道的芯片,既可以作为两通道的芯片进行销售,也可以通过封装方式裁剪为单通道以更低的售价推向市场,这是为了更好的覆盖市场的不同需求。同理把原始设计为四通道芯片,既可以作为四通道音频芯片销售,也可以通过封装方式裁剪变成一个三通道的音频编码译码器芯片进行低价销售。设计厂家这样做是基于经济利益考虑,单独设计芯片的费用非常昂贵,但是如果在已经设计完成的芯片上,通过封装的方式裁剪出不同的通道数以变成新的系列产品,这个研发成本较低,推向市场的时间也更快。

3.如上所述的现有方法,通过封装的方法减少了重新研发芯片的数量,但是这样做存在两个问题:一个是通过封装方法,虽然可以把原始设计上音频通道多的芯片裁剪为通道少的音频编解码芯片并推向市场,但是该通道少的芯片成本与裁剪之前的芯片实际上差别不多,因为芯片的硅片面积是一样大的,生产成本一样,只是减少了一些封装成本,这些减少的封装成本通常在总成本中占比不大。另一个是仍然需要设计研发多款芯片,例如需要单独设计两通道音频芯片、四通道音频芯片等等,因为通常设计厂家不会只设计一款具有最大通道数的产品,然后通过封装裁剪的方式推出各款低通道产品,这样虽然节约了研发成本,但是对于低通道产品是非常不经济的。

4.因此,在减少芯片设计种类的基础上如何提高低通道产品的经济性、适于各种不同通道数量的扩展,已成为本领域技术人员亟待解决的问题之一。

技术实现要素:

5.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种音频编码译码标准芯片单元及多通道音频编码译码器芯片,用于解决现有技术中芯片设计种类多,低通道产品不经济等问题。

6.为实现上述目的及其他相关目的,本发明提供一种音频编码译码标准芯片单元,所述音频编码译码标准芯片单元包括:

7.控制接口pad单元、音频接口pad单元、控制接口互联pad单元、音频接口互联pad单元、控制单元、音频数据传输单元、存储单元、dac单元和/或adc单元及与所述dac单元和/或adc单元对应的传输接口pad单元;

8.所述控制单元连接所述控制接口pad单元,通过所述控制接口pad单元获取通讯协议数字信号并译码为控制指令,为所述音频编码译码标准芯片单元中的各单元提供控制信号;

9.所述音频数据传输单元连接所述音频接口pad单元及所述存储单元,用于传输音频数据;

10.所述存储单元连接所述音频数据传输单元与adc单元,用于数据的缓存;

11.所述dac单元连接所述存储单元,将所述存储单元输出的数字信号转换为模拟信号后通过对应传输接口pad单元输出;

12.所述adc单元连接所述存储单元,接收对应传输接口pad单元输入的模拟信号并转化为数字信号后存入所述存储单元;

13.所述控制接口互联pad单元与所述控制接口pad单元对应连接;

14.所述音频接口互联pad单元与所述音频接口pad单元对应连接。

15.可选地,所述音频编码译码标准芯片单元还包括音效处理单元,所述音效处理单元连接所述存储单元,对所述存储单元中的音频数据进行音效处理。

16.可选地,所述音频编码译码标准芯片单元还包括电源接口、地接口、时钟接口、复位接口及gpio接口中的至少一个。

17.可选地,当所述音频编码译码标准芯片单元包括所述dac单元时,所述dac单元为单通道或两通道dac;当所述音频编码译码标准芯片单元包括所述adc单元时,所述adc单元为单通道或两通道adc。

18.更可选地,所述控制接口互联pad单元与所述控制接口pad单元、所述音频接口互联pad单元与所述音频接口pad单元分别通过芯片内部低阻抗金属线连接。

19.更可选地,所述控制接口互联pad单元与所述控制接口pad单元、所述音频接口互联pad单元与所述音频接口pad单元分别通过封装打线连接。

20.为实现上述目的及其他相关目的,本发明提供一种多通道音频编码译码器芯片,所述多通道音频编码译码器芯片包括:

21.主芯片及至少一从芯片,所述主芯片及所述从芯片采用上述音频编码译码标准芯片单元;

22.所述主芯片的控制接口pad单元、音频接口pad单元及与所述dac单元和/或adc单元对应的传输接口pad单元封装引出;

23.各从芯片的控制接口pad单元及音频接口pad单元连接前一级从芯片的控制接口互联pad单元及音频接口互联pad单元,第一级从芯片的控制接口pad单元及音频接口pad单元连接所述主芯片的控制接口互联pad单元及音频接口互联pad单元,各从芯片中与所述dac单元和/或adc单元对应的传输接口pad单元部分或全部封装引出。

24.可选地,所述主芯片及各从芯片之间的互联线通过金属预埋线连接。

25.可选地,所述主芯片及各从芯片之间的互联线通过封装打线连接。

26.如上所述,本发明的音频编码译码标准芯片单元及多通道音频编码译码器芯片,

具有以下有益效果:

27.本发明的多通道音频编码译码器芯片只需设计一款通道数量较少的标准音频编码译码芯片,该标准芯片既可以当做最低通道数的标准产品进行生产销售,也可以通过封装互连以及软件协同的方式扩展成多通道的音频编码译码器芯片进行生产销售,成本低且适用于不同通道数量的需求。

附图说明

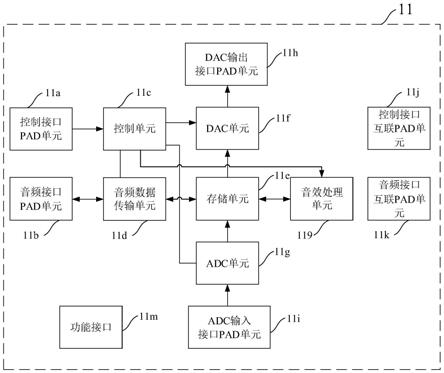

28.图1显示为本发明的音频编码译码标准芯片单元的电路结构示意图。

29.图2显示为本发明的音频编码译码标准芯片单元中控制接口pad单元与控制接口互联pad单元、音频接口pad单元与音频接口互联pad单元之间连接的一种实现方式示意图。

30.图3显示为本发明的音频编码译码标准芯片单元中控制接口pad单元与控制接口互联pad单元、音频接口pad单元与音频接口互联pad单元之间连接的另一种实现方式示意图。

31.图4显示为本发明的单芯片在晶圆上的一种切割方式示意图。

32.图5显示为本发明的单芯片的一种封装打线示意图。

33.图6显示为本发明的单芯片的一种封装成品示意图。

34.图7显示为本发明的双芯片在晶圆上的一种切割方式示意图。

35.图8显示为本发明的双芯片的一种封装打线示意图。

36.图9显示为本发明的双芯片的一种封装成品示意图。

37.图10显示为本发明的双芯片的一种主从芯片间金属预埋线连接方式示意图。

38.图11显示为本发明的双芯片下i2s->dac模式的软件配置流程图。

39.图12显示为本发明的双芯片下adc->i2s模式的软件配置流程图。

40.图13显示为本发明的双芯片下adc->dac模式的软件配置流程图。

41.图14显示为本发明的双芯片下控制单元的配置原理及等效电路示意图。

42.图15显示为本发明的双芯片下音频数据传输单元的一种配置原理及等效电路示意图。

43.图16显示为本发明的双芯片下音频数据传输单元的另一种配置原理及等效电路示意图。

44.图17显示为本发明的三芯片的一种封装打线示意图。

45.元件标号说明

[0046]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

多通道音频编码译码器芯片

[0047]

11a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制接口pad单元

[0048]

11b

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

音频接口pad单元

[0049]

11c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制单元

[0050]

11d

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

音频数据传输单元

[0051]

11e

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

存储单元

[0052]

11f

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

dac单元

[0053]

11g

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

adc单元

[0054]

11h

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

dac输出接口pad单元

[0055]

11i

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

adc输入接口pad单元

[0056]

11j

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制接口互联pad单元

[0057]

11k

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

音频接口互联pad单元

[0058]

11l

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

音效处理单元

[0059]

11m

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

功能接口

[0060]2ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

dsp芯片

具体实施方式

[0061]

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

[0062]

请参阅图1~图17。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,遂图式中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

[0063]

实施例一

[0064]

如图1所示,本实施例提供一种音频编码译码标准芯片单元11,所述音频编码译码标准芯片单元11包括:

[0065]

控制接口pad单元11a、音频接口pad单元11b、控制接口互联pad单元11j、音频接口互联pad单元11k、控制单元11c、音频数据传输单元11d、存储单元11e、dac单元11f和/或adc单元11g及与所述dac单元11f和/或adc单元11g对应的传输接口pad单元。所述dac单元11f及所述adc单元11g的设置可基于实际需要,所述dac单元11f及所述adc单元11g可二选一;且所述dac单元11f可以是单通道或双通道的数模转换器,所述adc单元11g可以是单通道或双通道的模数转换器。作为示例,在本实施例中,所述音频编码译码标准芯片单元11包括dac单元11f及adc单元11g;相应地,所述音频编码译码标准芯片单元11还包括dac输出接口pad单元11h及adc输入接口pad单元11i。

[0066]

如图1所示,所述控制单元11c连接控制接口pad单元11a,获取通讯协议数字信号并译码为控制指令,为所述音频编码译码标准芯片单元11中的各单元提供控制信号。

[0067]

具体地,所述控制单元11c通过所述控制接口pad单元11a与音频编码译码标准芯片单元11外部的其他芯片的相应控制端口进行通信,以产生所述音频编码译码标准芯片单元11中各单元的控制信号,以配置相关单元中的控制寄存器。

[0068]

具体地,所述控制单元11c包括但不限于i2c协议、spi协议、uart协议,任意可实现控制信号传输的接口类型均适用于本发明,不以本实施例为限。在本实施例中,所述控制单元11c采用i2c协议,包含两个io端口,分别为第一端口sda和第二端口sclk。

[0069]

如图1所示,所述音频接口pad单元11b用于与外部芯片进行数据传输。

[0070]

具体地,所述音频数据传输单元11d可以支持但不限于i2s协议、pcm协议、ac97协议,任意可实现音频数据传输的接口类型均适用于本发明,不以本实施例为限。在本实施例中,所述音频数据传输单元11d采用i2s协议,根据i2s协议,所述音频数据传输单元11d可以

包含4个或者更多的io,作为示例,所述i2s接口包括五个io端口。分别是第一端口lrck、第二端口bclk、第三端口dac_data1、第四端口dac_data2及第五端口adc_data。

[0071]

如图1所示,所述音频数据传输单元11d连接所述存储单元11e,用于传输音频数据。

[0072]

具体地,所述音频数据传输单元11d从所述音频接口pad单元11b获取i2s协议数据,对其解码变成pcm数据后保存到所述存储单元11e,或从所述存储单元11e获取音频pcm数据编码成i2s协议数据并通过所述音频接口pad单元11b传输到所述音频编码译码标准芯片单元11外。

[0073]

如图1所示,所述存储单元11e连接所述音频数据传输单元11d、所述dac单元11f及所述adc单元11g,用于数据的缓存。

[0074]

如图1所示,所述dac单元11f连接所述存储单元11e,将所述存储单元11e输出的数字信号转换为模拟信号后通过对应的dac输出接口pad单元11h输出。

[0075]

具体地,所述dac单元11f从所述存储单元11e获取数字的音频信号,并将数字的音频信号转换为模拟信号后通过所述dac输出接口pad单元11h输出到外部,其中所述dac单元11f的寄存器配置受所述控制单元11c的控制。在本实施例中,所述dac输出接口pad单元11h为一个dac输出接口dacout,当所述dac单元11f为两通道时所述dac输出接口pad单元11h具有相应的两个输出接口,在此不一一赘述。

[0076]

具体地,在本实施例中,所述dac单元11f为单通道的数模转换器。作为示例,所述dac单元11f采用单通道16bit精度音频sigma delta dac。

[0077]

如图1所示,所述adc单元11g连接所述存储单元11e,接收对应adc输入接口pad单元11i输入的模拟信号并转化为数字信号后存入所述存储单元11e。

[0078]

具体地,所述adc单元11g从所述adc输入接口pad单元11i获取外部模拟的音频信号,并将模拟的音频信号转换为数字信号并存入所述存储单元11e中,其中所述adc单元11g的寄存器配置受所述控制单元11c的控制。在本实施例中,所述adc输入接口pad单元11i为一个adc输入接口adcin,实际使用中,所述adc输入接口pad单元11i具有与所述adc单元11g的通道对应数量的输入接口,在此不一一赘述。

[0079]

具体地,在本实施例中,所述adc单元11g为单通道的模数转换器。作为示例,所述adc单元11g采用单通道16bit精度音频sigma delta adc。

[0080]

如图1所示,所述控制接口互联pad单元11j与所述控制接口pad单元11a对应连接。

[0081]

具体地,所述控制接口互联pad单元11j与所述控制接口pad单元11a具有相应的接口,且各接口一一对应连接。如图2及图3所示,在本实施例中,所述控制接口互联pad单元11j包括两个pad端口,分别为第一端口sda’和第二端口sclk’,端口sda’与端口sda连接,端口sclk’与端口sclk连接。在实际使用中,所述控制接口互联pad单元11j中各接口的功能及数量以所述控制接口pad单元11a采用的接口类型为准,在此不一一赘述。所述控制接口互联pad单元11j便于后续多个芯片之间的对应接口的封装互联。

[0082]

如图1所示,所述音频接口互联pad单元11k与所述音频接口pad单元11b对应连接。

[0083]

具体地,所述音频接口互联pad单元11k与所述音频接口pad单元11b具有相应的接口,且各接口一一对应连接。如图2及图3所示,在本实施例中,所述音频接口互联pad单元11k包括五个端口,分别为第一端口lrck’、第二端口bclk’、第三端口dac_data1’、第四端口

dac_data2’及第五端口adc_data’,端口lrck’与端口lrck连接,端口bclk’与端口bclk连接,端口dac_data1’与端口dac_data1连接,端口dac_data2’与端口dac_data2连接,端口adc_data’与端口adc_data连接。在实际使用中,所述音频接口互联pad单元11k中各接口的功能及数量以所述音频接口pad单元11b采用的接口类型为准,在此不一一赘述。所述音频接口互联pad单元11k便于后续多个芯片之间的对应接口的封装互联。

[0084]

如图2所示,作为示例,所述控制接口互联pad单元11j与所述控制接口pad单元11a、所述音频接口互联pad单元11k与所述音频接口pad单元11b分别通过芯片内部低阻抗金属线连接。

[0085]

如图3所示,作为另一示例,所述控制接口互联pad单元11j与所述控制接口pad单元11a、所述音频接口互联pad单元11k与所述音频接口pad单元11b分别通过封装打线连接。

[0086]

上述两种连接方式的效果相同,但是前者成本低灵活性高,本实例中采用如图2所示的方式。

[0087]

需要说明的是,任意其它形式的电连接均适用于本发明的所述控制接口互联pad单元11j与所述控制接口pad单元11a、所述音频接口互联pad单元11k与所述音频接口pad单元11b之间的连接,不限于本实施例所列举的两种方式。

[0088]

作为本发明的一种实现方式,如图1所示,所述音频编码译码标准芯片单元11还包括音效处理单元11l,所述音效处理单元11l连接所述存储单元11e,对所述存储单元11e中的音频数据进行音效处理。所述音效处理单元11l可采用但不限于均衡器、压限器、3d、低音增强等装置实现,在此不一一赘述。

[0089]

作为本发明的一种实现方式,如图1~图3所示,所述音频编码译码标准芯片单元11还包括电源接口、地接口、时钟接口、复位接口及gpio接口中的至少一个功能接口11m,在此不一一赘述,各接口用于维持所述音频编码译码标准芯片单元11的正常工作。

[0090]

实施例二

[0091]

如图4~图6所示,本实施例提供一种多通道音频编码译码器芯片1,所述多通道音频编码译码器芯片1包括:

[0092]

一个如实施例一所述的音频编码译码标准芯片单元11,所述音频编码译码标准芯片单元11的控制接口pad单元11a、音频接口pad单元11b、dac单元11f和/或adc单元11g对应的传输接口pad单元以及功能接口11m相关pad封装引出。

[0093]

具体地,如图4所示,所述音频编码译码标准芯片单元11作为芯片单元制备于晶圆(wafer)上,每个小格代表一个完整的标准芯片单元,通过晶圆切割得到单个芯片单元。如图5~图6所示,再通过打线、封装得到所述多通道音频编码译码器芯片1,在本实施例中,所述多通道音频编码译码器芯片1为单通道dac+单通道adc的音频编码译码器芯片。在实际使用中以所述音频编码译码标准芯片单元11内dac及adc的通道数为准,不以本实施例为限。

[0094]

更具体地,在本实施例中,如图5所示,所述控制接口pad单元11a、所述音频接口pad单元11b、所述dac输出接口pad单元11h、所述adc输入接口pad单元11i及其他功能接口11m(包括但不限于电源接口、地接口、时钟接口、复位接口及gpio接口)封装引出,所述控制接口互联pad单元11j、音频接口互联pad单元11k不引出,相当于弃用。

[0095]

本实施例的单通道dac+单通道adc的音频编码译码器芯片的软件配置流程如下:

[0096]

i2s->dac功能模式:对所述音频编码译码器芯片上电,通过控制接口配置所述芯

片;具体地,将所述芯片的工作模式配置为i2s->dac;i2s模式配置为master模式或slave模式;配置相关dac寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。

[0097]

adc->i2s功能模式:对所述音频编码译码器芯片上电,通过控制接口配置所述芯片;具体地,将所述芯片的工作模式配置为adc->i2s;i2s模式配置为master模式或slave模式;配置相关adc寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。

[0098]

adc->dac功能模式:对所述音频编码译码器芯片上电,通过控制接口配置所述芯片;具体地,将所述芯片的工作模式配置为adc->dac;配置相关adc、dac寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。

[0099]

实施例三

[0100]

如图7~图9所示,本实施例提供一种多通道音频编码译码器芯片1,所述多通道音频编码译码器芯片1包括:

[0101]

主芯片及至少一从芯片,所述主芯片及所述从芯片采用实施例一的音频编码译码标准芯片单元11,

[0102]

所述主芯片的控制接口pad单元11a、音频接口pad单元11b、dac单元11f和/或adc单元11g对应的传输接口pad单元以及功能接口11m相关pad封装引出;

[0103]

各从芯片的控制接口pad单元11a及音频接口pad单元11b连接前一级从芯片的控制接口互联pad单元11j及音频接口互联pad单元11k,第一级从芯片的控制接口pad单元11a及音频接口pad单元11b连接所述主芯片的控制接口互联pad单元11j及音频接口互联pad单元11k,各从芯片中与所述dac单元11f和/或adc单元11g对应的传输接口pad单元封装引出。

[0104]

具体地,如图7所示,所述音频编码译码标准芯片单元11作为芯片单元制备于晶圆上,每个小格代表一个完整的标准芯片单元,以两个芯片单元为一组切割晶圆得到相邻的两个芯片单元。如图8~图9所示,再通过打线、封装得到所述多通道音频编码译码器芯片1,在本实施例中,所述多通道音频编码译码器芯片1为两通道dac+两通道adc的音频编码译码器芯片。在实际使用中以所述音频编码译码标准芯片单元11内dac及adc的通道数为准,不以本实施例为限。

[0105]

更具体地,在本实施例中包括两颗芯片,分别为主芯片及从芯片,在实际使用中可基于设计需要设置所述从芯片的数量,不以本实施例为限。所述主芯片的控制接口pad单元11a、音频接口pad单元11b、dac输出接口pad单元11h、adc输入接口pad单元11i及其他功能接口11m(包括但不限于电源接口、地接口、时钟接口、复位接口及gpio接口)封装引出,控制接口互联pad单元11j、音频接口互联pad单元11k分别与从芯片的控制接口pad单元11a及音频接口pad单元11b对应连接。从芯片的dac输出接口pad单元11h、adc输入接口pad单元11i及其他功能接口11m封装引出,控制接口互联pad单元11j和音频接口互联pad单元11k不引出,相当于弃用。

[0106]

如图8所示,作为示例,所述主芯片与所述从芯片之间通过封装打线连接。

[0107]

如图10所示,作为示例,所述主芯片与所述从芯片之间通过芯片内部低阻抗金属线(预埋线)预先连通,这样就无需在封装时打线,可以更加节约成本。图10显示为晶圆上的

一个局部位置,2*4个标准芯片,每两个芯片为一组,在设计上已经保证了它们内部的控制接口pad单元11a和音频接口pad单元11b都分别与一个相邻芯片的控制接口互联pad单元11j和音频接口互联pad单元11k连接,在生产晶圆的时候就全部分别相连。切割的时候,确保纵向切线要切割在没有金属预埋线的相邻芯片那边即可,这样切割下来的芯片部分就天然连接起来了,无需额外打线连接。

[0108]

本实施例的两通道dac+两通道adc的音频编码译码器芯片的软件配置流程如下:

[0109]

i2s->dac功能模式:如图11所示,首先对所述多通道音频编码译码器芯片1上电,通过控制接口配置所述主芯片;具体地,将所述主芯片的工作模式配置为i2s->dac;i2s模式配置为master模式或slave模式;再配置主芯片接收i2s数据的方式,包括但不限于固定取dac_data1左声道数据进行dac播放输出;配置相关dac寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。然后对从芯片进行配置,配置的流程与主芯片基本相同,不同之处在于,从芯片的i2s模式只能配置为slave模式,同时从芯片固定收取不同于主芯片收取声道的数据,例如右声道数据进行dac播放输出。

[0110]

adc->i2s功能模式:如图12所示,首先对所述多通道音频编码译码器芯片1上电,通过控制接口配置所述主芯片;具体地,将所述主芯片的工作模式配置为adc->i2s;i2s模式配置为master模式或slave模式;再配置主芯片接收i2s数据的方式,在本实施例中,固定把数据放在左声道输出;配置相关adc寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。然后对从芯片进行配置,配置的流程与主芯片基本相同,不同之处在于,从芯片的i2s模式只能配置为slave模式,同时从芯片固定把数据放在不同于主芯片数据的声道上,例如固定把数据放到右声道输出。

[0111]

adc->dac功能模式:如图13所示,首先对所述多通道音频编码译码器芯片1上电,通过控制接口配置所述主芯片;具体地,将所述主芯片的工作模式配置为adc->dac;配置相关adc、dac寄存器,包括但不限于采样率;若需要音效处理则配置音效算法及相关参数;还包括配置相关系统参数,包括但不限于时钟、电源等。然后对从芯片进行配置,配置的流程与主芯片相同。

[0112]

需要说明的是,主芯片与从芯片中各参数的配置顺序不限于本实施例所列举,能基于时序完成主芯片与从芯片的配置即可,在此不一一赘述。

[0113]

本实施例的两通道dac+两通道adc的音频编码译码器芯片需要通过外部控制芯片2(包括但不限于dsp芯片)实现配置,其中,控制单元11c的配置方法如下:

[0114]

如图8所示,所述音频编码译码器芯片1中只有主芯片的控制接口pad单元11a才能被封装出来,与外部dsp芯片2对应端口连接,其他的从芯片的控制接口pad单元11a分别与前一级芯片(主芯片或从芯片)的控制接口互联pad单元11j进行串联,实际连接关系等效于图14,也就是实际上每一个标准芯片的控制接口pad单元11a都是互相连通的。由于所述音频编码译码器芯片1属于从设备,所以i2c工作在slave模式,另外,每个标准芯片内部配置有独立且唯一的芯片地址,这样根据i2c标准协议,可以实现外部dsp芯片2只通过主芯片的两个端口(sda、sclk)根据不同的标准芯片地址,读取或者写入不同标准芯片的寄存器。

[0115]

音频接口pad单元11d的配置方法如下:

[0116]

如图8所示,所述音频编码译码器芯片1中只有主芯片的音频接口pad单元11d才能被封装出来,与外部dsp芯片2对应端口连接,其他的从芯片的音频接口pad单元11d分别与前一级芯片(主芯片或从芯片)的音频接口互联pad单元11k进行串联,实际连接关系等效于图15及16,也就是实际上每一个标准芯片的音频接口pad单元11d都是互相连通的。

[0117]

i2s协议有两种模式,一种是master模式,一种是slave模式,如果所述音频编码译码器芯片1工作在i2s master模式下,则连接方式等效于图15,主芯片提供i2s总线上的bclk、lrck两个信号,从芯片工作在i2s slave模式下,同时外部dsp芯片2也工作在i2s slave模式下。如果所述音频编码译码器芯片1工作在i2s slave模式下,则连接方式等效于图16,主芯片及从芯片均工作在i2s slave模式下,外部dsp芯片2工作在i2s master模式并提供bclk、lrck两个信号。

[0118]

进一步,如果所述音频编码译码器芯片1功能为i2s->dac,那么外部dsp芯片2通过i2c接口依次配置主芯片及从芯片,确保主芯片及从芯片在各自对应的时刻从dac_data1或者dac_data2收取数据并通过dac输出,例如可以根据bclk、lrck两个信号的相位关系,安排主芯片从dac_data1左声道取数据,从芯片从dac_data1右声道取数据等,具体可以参考音频编码译码器芯片的软件配置流程。

[0119]

如果音频芯片功能为adc->i2s,那么外部dsp芯片2通过i2c接口依次配置主芯片及从芯片,确保主芯片及从芯片在各自对应的时刻,把各自的adc的数据输出到adc_data上,其他时候必须保持高阻,确保不影响其他芯片的输出,具体可以参考音频编码译码器芯片的软件配置流程。

[0120]

需要说明的是,为了让主芯片及从芯片的时钟保持同步,使得dac输出或者adc的采样保持一致,主芯片及从芯片也通过互联的方式共用同一个时钟,方式可以参考i2s数据互联的方法,具体实现方式在此不一一赘述。

[0121]

实施例四

[0122]

如图17所示,本实施例提供一种多通道音频编码译码器芯片1,与实施例三的不同之处在于,本实施例包括两颗从芯片。

[0123]

具体地,在本实施例中包括三颗芯片,分别为主芯片、第一从芯片及第二从芯片。所述主芯片的控制接口pad单元11a、音频接口pad单元11b、dac输出接口pad单元11h、adc输入接口pad单元11i及其他功能接口11m(包括但不限于电源接口、地接口、时钟接口、复位接口及gpio接口)封装引出,控制接口互联pad单元11j、音频接口互联pad单元11k分别与所述第一从芯片的控制接口pad单元11a及音频接口pad单元11b对应连接。所述第一从芯片的dac输出接口pad单元11h、adc输入接口pad单元11i及其他功能接口11m封装引出,控制接口互联pad单元11j和音频接口互联pad单元11k分别与所述第二从芯片的控制接口pad单元11a及音频接口pad单元11b对应连接。所述第二从芯片的dac输出接口pad单元11h、adc输入接口pad单元11i及其他功能接口11m封装引出,控制接口互联pad单元11j和音频接口互联pad单元11k不引出,相当于弃用。

[0124]

本实施例的多通道音频编码译码器芯片1为三通道dac+三通道adc的音频编码译码器芯片,其软件配置流程及配置方法与实施例三基本相同,仅多增加一个从芯片的配置步骤,在此不一一赘述。

[0125]

需要说明的是,本实施例的多通道音频编码译码器芯片1的具体电路、连接关系、

连接方式均与实施例三相同,在此不一一赘述。同样的方式可扩展出更多通道,在实际使用中adc与dac的通道数量可以相同,也可以不相同,不用的通道对应接口不引出即可,在此不一一赘述。

[0126]

综上所述,本发明提供一种音频编码译码标准芯片单元及多通道音频编码译码器芯片,包括:控制接口pad单元、音频接口pad单元、控制接口互联pad单元、音频接口互联pad单元、控制单元、音频数据传输单元、存储单元、dac单元和/或adc单元及与所述dac单元和/或adc单元对应的传输接口pad单元;所述控制单元连接所述控制接口pad单元,通过所述控制接口pad单元获取协议数字信号并译码为控制指令,为所述音频编码译码标准芯片单元中的各单元提供控制信号;所述音频数据传输单元连接所述音频接口pad单元及所述存储单元,用于传输音频数据;所述存储单元连接所述音频数据传输单元,用于数据的缓存;所述dac单元连接所述存储单元,将所述存储单元输出的数字信号转换为模拟信号后通过对应传输接口pad单元输出;所述adc单元连接所述存储单元,接收对应传输接口pad单元输入的模拟信号并转化为数字信号后存入所述存储单元;所述控制接口互联pad单元与所述控制接口pad单元对应连接;所述音频接口互联pad单元与所述音频接口pad单元对应连接。本发明通过只设计一款通道数量较少的标准音频编码译码芯片,利用封装互连以及软件协同的方式扩展成多通道的音频编码译码器芯片,成本低且适用于不同通道数量的需求。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

[0127]

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。