1.本技术涉及显示技术领域,具体涉及一种阵列基板及显示面板。

背景技术:

2.目前,垂直配向型(英文全称:vertical alignment,简称va)液晶显示面板在不同视角下,液晶分子双折射率的差异较大,色偏较严重。高垂直配向型(英文全称:high vertical alignment,简称hva)液晶显示面板需设计多畴显示以改善色偏。基于电学原理,将像素单元分为液晶分子转动角度不同的主像素(英文全称:main pixel)区和次像素(英文全称:sub pixel)区,结合物理结构上的4畴(domain),可以实现8domain显示。

3.目前的8domain显示是通过一个主像素薄膜晶体管控制主像素电极,通过次像素薄膜晶体管和分享薄膜晶体管共同控制次像素电极,实现主像素电极和次像素电极的不同电位,这种设计可单独控制次像素电极偏压,实现低色偏(英文全称:low color shift)和残像优化。

4.如图1、图2所示,目前的分享薄膜晶体管的分享电极线100’(英文全称:share bar)纵穿主像素区及次像素区的中间,由此会减小像素单元的透光面积,降低像素单元的开口率;目前的分享薄膜晶体管的公共线200’为第一层金属走线,分享电极线100’为第二层金属走线,分享电极线100’覆盖于公共线200’上方,由此会降低像素单元的穿透率。

技术实现要素:

5.本发明的目的是提供一种阵列基板及显示面板,其能够解决现有技术中存在的像素单元开口率低下及穿透率低下等问题。

6.为了解决上述问题,本发明提供了一种阵列基板,其包括基板及阵列排布于所述基板上的多个像素单元;每一所述像素单元均分为主像素区和次像素区;每一所述像素单元均包括:数据线,设置于相邻所述像素单元之间;扫描线,与所述数据线交错设置于所述基板上,且位于所述主像素区和所述次像素区之间;第一公共线,设置于所述扫描线靠近所述主像素区的一侧的所述基板上,且平行于所述扫描线;以及第一分享线,设置于所述扫描线靠近所述次像素区的一侧的所述基板上,且平行于所述扫描线。

7.进一步的,所述第一公共线、所述第一分享线以及所述扫描线同层设置。

8.进一步的,每一所述像素单元均还包括:主像素电极,设置于所述主像素区内,所述主像素电极包括平行于所述数据线的第一主干电极;次像素电极,设置于所述次像素区内,所述次像素电极包括平行于所述数据线的第二主干电极;主像素薄膜晶体管,其栅极电连接至所述扫描线,其源极电连接至所述数据线,其漏极电连接至所述主像素电极;次像素薄膜晶体管,其栅极电连接至所述扫描线,其源极电连接至所述数据线,其漏极电连接至所述次像素电极;以及分享薄膜晶体管,其栅极电连接至所述扫描线,其源极电连接至所述次像素薄膜晶体管的漏极,其漏极电连接至所述第一分享线。

9.进一步的,每一所述像素单元均还包括:第二公共线,平行于所述数据线,其一端

电连接至所述第一公共线,另一端沿着所述数据线的延伸方向由一所述像素单元的主像素区延伸至相邻的所述像素单元的次像素区。

10.进一步的,所述第二公共线包括相互间隔设置的第一子公共线、第二子公共线以及第三子公共线;在所述主像素区内,所述第一子公共线设置于所述主像素电极与所述数据线之间,所述第二子公共线设置于所述主像素电极远离所述数据线的一侧,所述第三子公共线与所述第一主干电极对应设置;在所述次像素区内,所述第一子公共线设置于所述次像素电极与所述数据线之间,所述第二子公共线设置于所述次像素电极远离所述数据线的一侧,所述第三子公共线与所述第二主干电极对应设置。

11.进一步的,每一所述像素单元均还包括:第二分享线,平行于所述数据线,其一端电连接至所述第一分享线,另一端沿着所述数据线的延伸方向由一所述像素单元的次像素区延伸至相邻的所述像素单元的主像素区。

12.进一步的,所述第二分享线包括相互间隔设置的第一子分享线、第二子分享线以及第三子分享线;在所述主像素区内,所述第一子分享线设置于所述主像素电极与所述数据线之间,所述第二子分享线设置于所述主像素电极远离所述数据线的一侧,所述第三子分享线与所述第一主干电极对应设置;在所述次像素区内,所述第一子分享线设置于所述次像素电极与所述数据线之间,所述第二子分享线设置于所述次像素电极远离所述数据线的一侧,所述第三子分享线与所述第二主干电极对应设置。

13.进一步的,所述扫描线、所述第二公共线以及所述第二分享线同层设置。

14.进一步的,在所述主像素区内,所述第一主干电极层叠设置于所述第三子公共线远离所述基板的一侧;在所述次像素区内,所述第二主干电极层叠设置于所述第三子公共线远离所述基板的一侧;或者在所述主像素区内,所述第一主干电极层叠设置于所述第三子分享线远离所述基板的一侧;在所述次像素区内,所述第二主干电极层叠设置于所述第三子分享线远离所述基板的一侧。

15.为了解决上述问题,本发明提供了一种显示面板,其包括本发明所述的阵列基板、与所述阵列基板对应设置的彩膜基板以及设置于所述阵列基板与所述彩膜基板之间的液晶层。

16.本发明的优点是:本发明将第一公共线和第一分享线分别设置于扫描线的两侧,由此避免现有技术中的第一分享线纵穿所述主像素区和次像素区,进而提升像素单元的开口率和穿透率。将第一公共线、第一分享线以及扫描线同层设置,由此进一步提升像素单元的穿透率。

附图说明

17.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

18.图1是现有技术的阵列基板的一个像素单元的平面示意图;

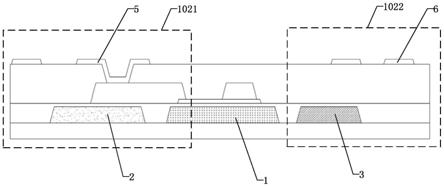

19.图2是图1的a-a截面图;

20.图3是本发明实施例1的阵列基板的平面示意图;

21.图4是本发明实施例1的阵列基板的一个像素单元的平面示意图;

22.图5是图4中的b-b截面图;

23.图6是本发明实施例1的阵列基板的两个像素单元的局部平面示意图;

24.图7是图4中的c-c截面图;

25.图8是图4中的d-d截面图;

26.图9是本发明实施例1的阵列基板的驱动电路图;

27.图10是本发明实施例2的阵列基板的一个像素单元的平面示意图;

28.图11是本发明实施例2的阵列基板的两个像素单元的局部平面示意图。

29.图12是图10中的e-e截面图;

30.图13是图10中的f-f截面图。

31.附图标记说明:

32.100、阵列基板;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

101、基板;

33.102、像素单元;

34.1021、主像素区;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

1022、次像素区;

35.1、扫描线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

2、第一公共线;

36.3、第一分享线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

4、数据线;

37.5、主像素电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

6、次像素电极;

38.7、主像素薄膜晶体管;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

8、次像素薄膜晶体管;

39.9、分享薄膜晶体管;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

10、第二公共线;

40.11、第二分享线;

41.110、第一子公共线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

120、第二子公共线;

42.130、第三子公共线;

43.111、第一子分享线;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

112、第二子分享线;

44.113、第三子分享线;

45.51、第一主干电极;

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

61、第二主干电极。

具体实施方式

46.以下结合说明书附图详细说明本发明的优选实施例,以向本领域中的技术人员完整介绍本发明的技术内容,以举例证明本发明可以实施,使得本发明公开的技术内容更加清楚,使得本领域的技术人员更容易理解如何实施本发明。然而本发明可以通过许多不同形式的实施例来得以体现,本发明的保护范围并非仅限于文中提到的实施例,下文实施例的说明并非用来限制本发明的范围。

47.本发明所提到的方向用语,例如「上」、「下」、「前」、「后」、「左」、「右」、「内」、「外」、「侧面」等,仅是附图中的方向,本文所使用的方向用语是用来解释和说明本发明,而不是用来限定本发明的保护范围。

48.在附图中,结构相同的部件以相同数字标号表示,各处结构或功能相似的组件以相似数字标号表示。此外,为了便于理解和描述,附图所示的每一组件的尺寸和厚度是任意示出的,本发明并没有限定每个组件的尺寸和厚度。

49.实施例1

50.本实施例提供了一种显示面板。所述显示面板包括阵列基板、与所述阵列基板对应设置的彩膜基板以及设置于所述阵列基板与所述彩膜基板之间的液晶层。

51.如图3所示,所述阵列基板100包括:基板101及阵列排布于所述基板101上的多个像素单元102。

52.其中,基板101的材质为玻璃、聚酰亚胺、聚碳酸酯、聚对苯二甲酸乙二醇酯以及聚萘二甲酸乙二醇酯中的一种或多种,由此基板101可具有较好的抗冲击能力,可以有效保护显示面板。

53.如图4所示,每一所述像素单元102均分为主像素区1021和次像素区1022。每一所述像素单元102均包括:扫描线1、第一公共线2、第一分享线3、数据线4、主像素电极5、次像素电极6、主像素薄膜晶体管7、次像素薄膜晶体管8、分享薄膜晶体管9以及第二公共线10。

54.如图4、图5及图6所示,扫描线1与所述数据线4交错设置于所述基板101上,且位于所述主像素区1021和所述次像素区1022之间。本实施例中,所述扫描线1的材质为金属。在其他实施例中,所述扫描线1的材质也可以是其他导电材料。例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其他导电材料的堆叠层或其他合适的材料。

55.如图4、图5及图6所示,第一公共线2设置于所述扫描线1靠近所述主像素区1021的一侧的所述基板101上。所述第一公共线2平行于所述扫描线1,且与所述扫描线1间隔设置。本实施例中,所述第一公共线2的材质为金属。在其他实施例中,所述第一公共线2的材质也可以是其他导电材料。例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其他导电材料的堆叠层或其他合适的材料。

56.如图4、图5及图6所示,第一分享线3间隔设置于所述扫描线1靠近所述次像素区1022的一侧的所述基板101上。所述第一分享线3平行于所述扫描线1,且与所述扫描线1间隔设置。本实施例中,所述第一分享线3的材质为金属。在其他实施例中,所述第一分享线3的材质也可以是其他导电材料。例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其他导电材料的堆叠层或其他合适的材料。

57.其中,所述扫描线1、所述第一公共线2以及所述第一分享线3同层设置。本实施例中,所述扫描线1、所述第一公共线2以及所述第一分享线3的材质相同,由此可以在一道工序内同时制备形成,进而可以节省工序,节约生产成本。

58.本实施例将第一公共线2和第一分享线3分别设置于扫描线1的两侧,由此避免现有技术中的第一分享线100’纵穿所述主像素区1021和次像素区1022,进而提升像素单元102的开口率和穿透率。将第一公共线2、第一分享线3以及扫描线1同层设置,由此进一步提升像素单元102的穿透率。

59.如图4、图6所示,数据线4设置于相邻所述像素单元102之间,且与所述扫描线1相互交错设置。换言之,所述数据线4的延伸方向和扫描线1的延伸方向不平行。本实施例中,所述数据线4的延伸方向与扫描线1的延伸方向相互垂直。本实施例中,所述数据线4的材质为金属。在其他实施例中,所述数据线4的材质也可以是其他导电材料。例如:合金、金属材料的氮化物、金属材料的氧化物、金属材料的氮氧化物、或是金属材料与其他导电材料的堆叠层或其他合适的材料。

60.如图4、图6、图7所示,主像素电极5设置于所述主像素区1021内。主像素电极5包括

平行于所述数据线4的第一主干电极51。

61.如图4、图6、图8所示,次像素电极6设置于所述次像素区1022内。次像素电极6包括平行于所述数据线4的第二主干电极61。

62.如图4、图6所示,第二公共线10的一端电连接至所述第一公共线2,另一端沿着所述数据线4的延伸方向由一所述像素单元102的主像素区1021延伸至相邻的所述像素单元102的次像素区1022。第二公共线10平行于所述数据线4,且与所述数据线4间隔设置。其中,所述第二公共线10与所述扫描线1、所述第一公共线2以及所述第一分享线3同层设置。

63.如图4、图6所示,所述第二公共线10包括相互间隔设置的第一子公共线110、第二子公共线120以及第三子公共线130。

64.如图4、图6、图7所示,在所述主像素区1021内,所述第一子公共线110设置于所述主像素电极5与所述数据线4之间,所述第二子公共线120设置于所述主像素电极5远离所述数据线4的一侧,所述第三子公共线130与所述第一主干电极51对应设置。在所述主像素区1021内,所述第一主干电极层51叠设置于所述第三子公共线130远离所述基板101的一侧。由此可以避免额外占用阵列基板100的透光面积,提升阵列基板100的开口率。

65.如图4、图6、图8所示,在所述次像素区1022内,所述第一子公共线110设置于所述次像素电极6与所述数据线4之间,所述第二子公共线120设置于所述次像素电极6远离所述数据线4的一侧,所述第三子公共线130与所述第二主干电极61对应设置。在所述次像素区1022内,所述第二主干电极层61叠设置于所述第三子公共线130远离所述基板101的一侧。由此可以避免额外占用阵列基板100的透光面积,提升阵列基板100的开口率。

66.如图4、图9所示,所述主像素薄膜晶体管7(即图9中的t1)的栅极电连接至所述扫描线1(即图9中的gate);所述主像素薄膜晶体管7(即图9中的t1)的源极电连接至所述数据线4(即图9中的data),所述主像素薄膜晶体管7(即图9中的t1)的漏极电连接至所述主像素电极5。

67.如图4、图9所示,所述次像素薄膜晶体管8(即图9中的t2)的栅极电连接至所述扫描线1(即图9中的gate);所述次像素薄膜晶体管8(即图9中的t2)的源极电连接至所述数据线4(即图9中的data),所述次像素薄膜晶体管8(即图9中的t2)的漏极电连接至所述次像素电极6。

68.如图4、图9所示,所述分享薄膜晶体管9(即图9中的t3)的栅极电连接至所述扫描线1(即图9中的gate);所述分享薄膜晶体管9(即图9中的t3)的源极电连接至所述次像素薄膜晶体管8(即图9中的t2)的漏极,所述分享薄膜晶体管9(即图9中的t3)的漏极电连接至所述第一分享线3。

69.其中,所述主像素薄膜晶体管7的栅极、所述次像素薄膜晶体管8的栅极和所述分享薄膜晶体管9的栅极电连接至同一所述扫描线1;所述主像素薄膜晶体管7的源极和所述次像素薄膜晶体管8的源极电连接至同一条所述数据线4。

70.实施例2

71.如图10-图13所示,实施例2包括了实施例1的大部分技术特征,实施例2与实施例1的区别在于:实施例2中去除了实施例1的第二公共线10,在实施例1的第二公共线10的位置处设置了第二分享线11。

72.如图10、图11所示,第二分享线11的一端电连接至所述第一分享线3,另一端沿着

所述数据线4的延伸方向由一所述像素单元102的次像素区1022延伸至相邻的所述像素单元102的主像素区1021。第二分享线11平行于所述数据线,且与所述数据线4间隔设置。其中,第二分享线11与所述扫描线1、所述第一公共线2以及所述第一分享线3同层设置。

73.如图10、图11所示,所述第二分享线11包括相互间隔设置的第一子分享线111、第二子分享线112以及第三子分享线113。

74.如图10、图11、图12所示,在所述主像素区1021内,所述第一子分享线111设置于所述主像素电极5与所述数据线4之间,所述第二子分享线112设置于所述主像素电极5远离所述数据线4的一侧,所述第三子分享线113与所述第一主干电极51对应设置。在所述主像素区1021内,所述第一主干电极51层叠设置于所述第三子分享线113远离所述基板101的一侧。由此可以避免额外占用阵列基板100的透光面积,提升阵列基板100的开口率。

75.如图10、图11、图13所示,在所述次像素区1022内,所述第一子分享线111设置于所述次像素电极6与所述数据线4之间,所述第二子分享线112设置于所述次像素电极6远离所述数据线4的一侧,所述第三子分享线113与所述第二主干电极61对应设置。在所述次像素区1022内,所述第二主干电极61层叠设置于所述第三子分享线113远离所述基板101的一侧。由此可以避免额外占用阵列基板100的透光面积,提升阵列基板100的开口率。

76.本实施例将第一公共线2和第一分享线3分别设置于扫描线1的两侧,由此避免现有技术中的第一分享线100’纵穿所述主像素区1021和次像素区1022,进而提升像素单元102的开口率和穿透率。将第一公共线2、第一分享线3以及扫描线1同层设置,由此进一步提升像素单元102的穿透率。

77.以上对本技术所提供的一种阵列基板及显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。