1.本技术涉及显示技术领域,尤其涉及一种显示面板、阵列基板及其制造方法。

背景技术:

2.传统的液晶显示面板包括阵列基板、彩膜基板以及夹设在彩膜基板和阵列基板之间的液晶层。参照图1,其显示一种现有技术的显示面板的阵列基板10的示意图。阵列基板10包括数据线11、栅极线12、公共电极13、屏蔽电极14、像素电极15和薄膜晶体管16。数据线11和栅极线12相互垂直且定义出像素区域。像素电极15和薄膜晶体管16设置在像素区域内,且像素电极15通过薄膜晶体管16与数据线11和栅极线12电连接。

3.参照图2,其显示图1的阵列基板10沿着割面线a-a的剖面图。阵列基板10还包含基底17和绝缘层18。数据线11和公共电极13设置在基底17上。绝缘层18设置在基底17、数据线11和公共电极13上。屏蔽电极14和像素电极15设置在绝缘层18上。屏蔽电极14采用dbs(data line black matrix less)技术,其是通过将屏蔽电极14设置在数据线11上方以起到遮蔽数据线11的效果,从而取代传统的黑矩阵。

4.如图2所示,在传统的阵列基板10中,为了防止数据线11对像素电极15产生干扰而造成漏光和串扰等不良影响,必须在数据线11的两侧设置公共电极13,以及在数据线11的上方设置屏蔽电极14。然而,公共电极13和屏蔽电极14会造成像素的开口率损失。其次,由于屏蔽电极14通常采用电阻较大的透明导电材料,导致其被数据线11耦合后电位恢复较慢,容易引起水平串扰问题。再者,公共电极13通常采用不透明的金属材料,公共电极13会与像素电极15构成存储电容,存储电容与像素的开口率为负相关。为了确保像素的开口率,存储电容的数值被限制,进而导致显示面板的可变刷新率(variable refresh rate,vrr)效果差。此外,由于公共电极13和屏蔽电极14可覆盖的数据线11的范围有限,使得数据线11和与像素电极15之间的耦合电容较大,导致电容串扰和垂直串扰问题。

5.有鉴于此,有必要提出一种显示面板的阵列基板,以解决现有技术中存在的问题。

技术实现要素:

6.为解决上述现有技术的问题,本技术的目的在于提供一种显示面板、阵列基板及其制造方法,其能改善开口率损失、串扰和vrr不良等问题。

7.为达成上述目的,本技术提供一种阵列基板,包括:基板;数据线,设置在所述基板的一侧;第一钝化层,设置在所述数据线上;屏蔽电极,设置在所述第一钝化层远离所述基板的一侧;第二钝化层,设置在所述屏蔽电极上;以及像素电极,设置在所述第二钝化层上,其中所述屏蔽电极配置为屏蔽所述数据线和所述像素电极之间的电场,以及所述像素电极的第一侧边在所述基板上的正投影与所述数据线在所述基板上的正投影至少部分重叠。

8.在一些实施例中,所述像素电极包括第二侧边,所述第二侧边与所述第一侧边相连,所述阵列基板还包括公共电极,设置在所述基板上,且邻近所述第二侧边,所述屏蔽电极通过至少一通孔与所述公共电极电连接。

9.在一些实施例中,所述阵列基板还包括连接电极,设置在所述第二钝化层上,配置为通过所述至少一通孔连接所述屏蔽电极和所述公共电极。

10.在一些实施例中,所述阵列基板包括红色像素、绿色像素和蓝色像素,其中所述连接电极设置在所述蓝色像素。

11.在一些实施例中,所述像素电极在所述基板上的正投影与所述屏蔽电极在所述基板上的正投影至少部分重叠。

12.在一些实施例中,所述阵列基板还包括彩色滤光层,设置在所述第一钝化层和所述屏蔽电极之间。

13.本技术还提供一种阵列基板的制造方法,包括:提供基板;在所述基板的一侧设置数据线;在所述数据线上设置第一钝化层;在所述第一钝化层远离所述基板的一侧设置屏蔽电极;在所述屏蔽电极上设置第二钝化层;以及在所述第二钝化层上设置像素电极,其中所述屏蔽电极配置为屏蔽所述数据线和所述像素电极之间的电场,以及所述像素电极的第一侧边在所述基板上的正投影与所述数据线在所述基板上的正投影至少部分重叠。

14.在一些实施例中,在所述基板的一侧设置所述数据线之前,所述制造方法还包括:在所述基板上设置公共电极;以及在所述第二钝化层上设置所述像素电极时,所述制造方法还包括:将所述像素电极的第二侧边设置为邻近所述公共电极,其中所述第二侧边与所述第一侧边相连。

15.在一些实施例中,在所述第一钝化层远离所述基板的一侧设置所述屏蔽电极之前,所述制造方法还包括:在所述第一钝化层上设置彩色滤光层,其中所述彩色滤光层包含红色光阻、绿色光阻和蓝色光阻;在所述屏蔽电极上设置所述第二钝化层之后,所述制造方法还包括:在所述蓝色光阻的设置区域形成暴露出所述屏蔽电极和所述公共电极的两通孔,以及形成覆盖所述两通孔的孔壁的连接电极以电连接所述屏蔽电极和所述公共电极。

16.本技术还提供一种显示面板,包括:上述的阵列基板、对置基板和液晶层。对置基板与所述阵列基板相对设置,包括:第二基板;黑色矩阵层,设置在所述第二基板上;以及对置电极,设置在所述黑色矩阵层和所述第二基板上。液晶层设置在所述阵列基板和所述对置基板之间。

17.相较于先前技术,本技术通过在数据线与像素电极之间设置屏蔽电极可起到屏蔽数据线和像素电极之间的电场的效果,使得不需要在数据线与像素电极之间设置不透光金属电极,进而可有效地提高显示面板的开口率。其次,通过设置屏蔽电极可有效地降低数据线与像素电极之间的耦合电容,进而解决电容串扰和垂直串扰的问题。再者,通过将屏蔽电极和公共电极电连接以形成网格状公共电极,可避免被数据线引响而导致电位恢复较慢,进而解决水平串扰的问题。此外,由于屏蔽电极整面地设置在显示面板的透光区域,并且与像素电极有极大的重叠面积,故可有效地增加存储电容,进而解决vrr技术中因为像素电压降增加而导致的负面问题。

附图说明

18.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

19.图1显示一种现有技术的显示面板的阵列基板的示意图。

20.图2显示图1的阵列基板沿着割面线a-a的剖面图。

21.图3显示一种根据本技术的实施例的显示面板的示意图。

22.图4显示图3的显示面板的阵列基板的俯视图。

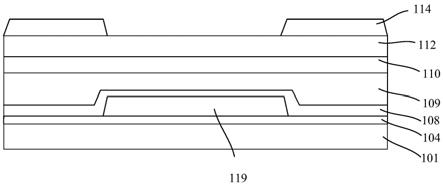

23.图5显示图4的阵列基板沿着割面线b-b的剖面图。

24.图6显示一种根据本技术的实施例的阵列基板的制造方法的流程图。

具体实施方式

25.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

26.请参照图3,其显示一种根据本技术的实施例的显示面板1的示意图。显示面板1包含阵列基板100、对置基板200和液晶层300。阵列基板100和对置基板200相对设置,且液晶层300设置在阵列基板100和对置基板200之间。显示面板1定义有透光区401和非透光区402。

27.如图3所示,阵列基板100包含第一基板101、公共电极102、栅极103、栅极绝缘层104、半导体层105、源极106、漏极107、第一钝化层108、彩色滤光层109、屏蔽电极110、隔离层111、第二钝化层112、连接电极113、像素电极114、第一通孔115、第二通孔116和第三通孔117。栅极103、栅极绝缘层104、半导体层105、源极106和漏极107构成薄膜晶体管tft。薄膜晶体管tft与公共电极102电性分离。公共电极102、薄膜晶体管tft、第一通孔115、第二通孔116和第三通孔117设置在显示面板1的非透光区402。在本实施例中,屏蔽电极110由透明导电材料(如氧化铟锡)制成。屏蔽电极110和像素电极114的极大部分设置在显示面板1的透光区401,且屏蔽电极110和像素电极114的一小部分设置在非透光区402。

28.如图3所示,对置基板200包括第二基板201、黑色矩阵层202和对置电极203。黑色矩阵层202设置在第二基板201上。对置电极203设置在第二基板201和黑色矩阵层202上。黑色矩阵层202设置在显示面板1的非透光区402。对置电极203整面地设置在透光区401和非透光区402。通过在阵列基板100的像素电极114和对置基板200的对置电极203施加电压以在液晶层300上产生电场,可控制液晶层300的液晶分子的方向以及控制入射光的偏振,使得显示面板1显示图像。

29.如图3所示,公共电极102和栅极103设置在第一基板101。栅极绝缘层104设置在栅极103上且包含曝露出公共电极102远离第一基板101的表面的开口。半导体层105设置在栅极绝缘层104上且与栅极103对应设置。源极106和漏极107设置在半导体层105上。第一钝化层108设置在公共电极102和薄膜晶体管tft远离所述第一基板的一侧。具体来说,第一钝化层108设置在栅极绝缘层104、半导体层105、源极106、漏极107上。第一钝化层108包含曝露出公共电极102远离第一基板101的表面的开口以及包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。彩色滤光层109设置在第一钝化层108。彩色滤光层109包含曝露出公共电极102远离第一基板101的表面的开口以及包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。屏蔽电极110设置在第一钝化层108远离第一基板101的一侧。具体来说,屏蔽电极110设置在彩色滤光层109上。隔离层111设置在彩色滤光层

109的没有被屏蔽电极110覆盖的表面上。隔离层111包含曝露出公共电极102远离第一基板101的表面的开口以及包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。第二钝化层112设置在隔离层111和屏蔽电极110上。第二钝化层112包含曝露出公共电极102远离第一基板101的表面的开口、包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口以及包含曝露出屏蔽电极110远离第一基板101的部分表面的开口。应当理解的是,由于屏蔽电极110设置在彩色滤光层109和第二钝化层112,因此不需要设置额外的绝缘层来避免屏蔽电极110与其他导电层接触。

30.如图3所示,第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112曝露出薄膜晶体管tft的漏极107的该些开口构成第一通孔115。第二钝化层112的曝露出屏蔽电极110的开口为第二通孔116。也就是说,第二通孔116贯穿第二钝化层112以曝露出屏蔽电极110。栅极绝缘层104、第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112曝露出公共电极102的该些开口构成第三通孔117。也就是说,第三通孔117贯穿栅极绝缘层104、第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112以曝露出公共电极102。

31.如图3所示,像素电极114设置在第二钝化层112上且覆盖住第一通孔115的孔壁。也就是说,像素电极114通过第一通孔115与薄膜晶体管tft的漏极107电连接。连接电极113设置在第二钝化层112上且与像素电极114间隔设置。连接电极113覆盖住第二通孔116和第三通孔117的孔壁。也就是说,连接电极113配置为通过第二通孔116和第三通孔117电连接屏蔽电极110和公共电极102。在本实施例中,通过将屏蔽电极110和公共电极102电连接以形成网格状公共电极,可避免被数据线引响而导致电位恢复较慢,进而解决水平串扰的问题。

32.参照图4和图5。图4显示图3的显示面板1的阵列基板100的俯视图。图5显示图4的阵列基板沿着割面线b-b的剖面图。图3的阵列基板100的示意图相当于图4的阵列基板100沿着割面线c-c的剖面图。如图4所示,阵列基板100包含多条栅极线118和多条数据线119,并且该些栅极线118和该些数据线119定义出多个像素p。栅极线118和公共电极102沿着第一方向延伸,数据线119沿着第二方向延伸,其中第一方向垂直于第二方向。每个像素p的像素电极114包含第一侧边、第二侧边和第三侧边。第一侧边和第三侧边相对,且第二侧边连接第一侧边和第三侧边。像素电极114的第一侧边和第三侧边分别与两数据线119相邻,且像素电极114的第二侧边与公共电极102相邻。在本实施例中,如图4所示,从俯视视角观视时,公共电极102仅仅邻近像素电极114的第二侧边,并且不会延伸至与数据线119相邻的第一侧边和第三侧边。因此,公共电极102在第一基板101上的正投影仅与像素电极114的第二侧边在第一基板101上的正投影重叠。

33.如图5所示,像素电极114的第一侧边在第一基板101上的正投影与数据线119在第一基板101上的正投影至少部分重叠。应当理解的是,通过屏蔽电极110可起到屏蔽数据线119和像素电极114之间的电场的效果,因此,不需要在数据线119与像素电极114之间设置不透光金属电极,使得像素电极114可延伸至邻近数据线119,进而可有效地提高显示面板的开口率。再者,通过在数据线119与像素电极114之间设置屏蔽电极110可有效地降低数据线119与像素电极114之间的耦合电容,进而解决电容串扰和垂直串扰的问题。

34.如图4所示,每个像素连接至单个栅极线和单个数据线,并且包含有薄膜晶体管tft和存储电容以驱动像素。如图3所示,像素电极114在第一基板101上的正投影与屏蔽电

极110在第一基板101上的正投影至少部分重叠。因此,像素电极114与屏蔽电极110共同形成像素的存储电容。应当理解的是,在显示面板1的驱动操作中,为了避免功耗的增加,可使用可变刷新率(variable refresh rate,vrr)技术。根据vrr技术,通过增加存储电容可有效地避免当以60hz或更低的低频驱动显示面板时,像素电压降增加,进而产生闪烁、图像残留等缺陷的问题。在本实施例中,由于屏蔽电极110整面地设置在显示面板1的透光区域,并且与像素电极114有极大的重叠面积,故可有效地增加存储电容。具体来说,如图3所示,在显示面板1的透光区401中,像素电极114在第一基板101上的正投影完全在屏蔽电极110在第一基板101上的正投影的范围内。因此,本技术可解决vrr技术中因为像素电压降增加而导致的负面问题。此外,通过整面的屏蔽电极110的设计,可避免因制程位移而引起的电容串扰和垂直串扰问题。

35.如图3和图4所示,存储电容的数值大小可进一步通过调节像素电极114与屏蔽电极110之间的第二钝化层112的厚度来调整。第二钝化层112的厚度越小,存储电容的数值越大。然而,第二钝化层112的厚度过薄容易有制程风险或充电率不足风险。因此,在一些实施例中,第二钝化层112的厚度较佳大于或等于0.4um。

36.应当理解的是,数据线119与薄膜晶体管tft的源极106和漏极107同时形成。由此,如图3和图4所示,数据线119与屏蔽电极110之间间隔厚度相对较厚的彩色滤光层109,因此不会使得数据线119与屏蔽电极110之间产生额外的寄生电容。

37.如图3和图4所示,彩色滤光层109对应不同的像素p包含相同或相异的彩色光阻,如红色光阻、绿色光阻和蓝色光阻。也就是说,本实施例的阵列基板100的像素p包含红色像素、绿色像素和蓝色像素。在一些实施例中,第二通孔116、第三通孔117和连接电极113设置在蓝色像素,即蓝色光阻的设置区域。第二通孔116、第三通孔117和连接电极113的设置会导致像素损失一部分的开口率。相较于改变其他颜色像素的开口率,选择降低蓝色像素的开口率,可使得视觉感受上对于光穿透率的影响最小。在一些实施例中,每一包含第二通孔116和第三通孔117的像素中,通孔的形状、尺寸和布局一致,如此可避免颜色不均(mura)的问题。

38.图6,其显示一种根据本技术的实施例的阵列基板的制造方法的流程图。图6的制造方法是用于制造上述的阵列基板100。阵列基板100的制造方法包含以下步骤。

39.在步骤s601中,提供基板。具体来说,提供阵列基板100的第一基板101。

40.在步骤s602中,在第一基板101的一侧设置数据线119。具体来说,首先,在第一基板101设置第一金属层,并且通过蚀刻工艺形成公共电极102、栅极线118和薄膜晶体管tft的栅极103。接着,在公共电极102、栅极线118和栅极103上形成栅极绝缘层104。栅极绝缘层104包含曝露出公共电极102远离第一基板101的表面的开口。在栅极绝缘层104上设置半导体层105。半导体层105与栅极103对应设置。之后,在栅极绝缘层104半导体层105上设置第二金属层,并且通过蚀刻工艺形成数据线119和薄膜晶体管tft的源极106和漏极107。

41.在步骤s603中,在数据线119上设置第一钝化层108。第一钝化层108还设置在栅极绝缘层104、半导体层105、源极106、漏极107上。第一钝化层108包含曝露出公共电极102远离第一基板101的表面的开口以及包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。

42.在步骤s604中,在第一钝化层108远离第一基板101的一侧设置屏蔽电极110。具体

来说,在第一钝化层108上设置彩色滤光层109。彩色滤光层109包含红色光阻、绿色光阻和蓝色光阻。彩色滤光层109包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。并且,在蓝色光阻的设置区域,彩色滤光层109还包含曝露出公共电极102远离第一基板101的表面的开口。接着,在彩色滤光层109上设置屏蔽电极110。

43.在步骤s605中,在屏蔽电极110上设置二钝化层112。具体来说,在彩色滤光层109的没有被屏蔽电极110覆盖的表面上设置隔离层111。隔离层111包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。并且,在蓝色光阻的设置区域,隔离层111包含曝露出公共电极102远离第一基板101的表面的开口。在隔离层111和屏蔽电极110上设置第二钝化层112。第二钝化层112包含曝露出薄膜晶体管tft的漏极107远离第一基板101的表面的开口。并且,在蓝色光阻的设置区域,第二钝化层112包含曝露出公共电极102远离第一基板101的表面的开口以及包含曝露出屏蔽电极110远离第一基板101的部分表面的开口。

44.如图3所示,第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112曝露出薄膜晶体管tft的漏极107的该些开口构成第一通孔115。在蓝色光阻的设置区域,阵列基板100还形成有第二通孔116和第三通孔117。具体来说,第二钝化层112的曝露出屏蔽电极110的开口为第二通孔116。也就是说,第二通孔116贯穿第二钝化层112以曝露出屏蔽电极110。栅极绝缘层104、第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112曝露出公共电极102的该些开口构成第三通孔117。也就是说,第三通孔117贯穿栅极绝缘层104、第一钝化层108、彩色滤光层109、隔离层111和第二钝化层112以曝露出公共电极102。

45.在步骤s606中,在第二钝化层112上设置像素电极114,其中像素电极114包含第一侧边和的第二侧边,并且第二侧边与第一侧边相连。在第二钝化层112上设置像素电极114时,将像素电极114的第二侧边设置为邻近公共电极102。屏蔽电极110配置为屏蔽数据线119和像素电极114之间的电场,以及像素电极114的第一侧边在第一基板101上的正投影与数据线119在第一基板101上的正投影至少部分重叠。接着,在第二钝化层112上形成连接电极113,进而形成阵列基板100。像素电极114设置在第二钝化层112上且覆盖住第一通孔115的孔壁,以与薄膜晶体管tft的漏极107电连接。在一些实施例中,像素电极114和连接电极113可通过同一道工艺形成。连接电极113设置在第二钝化层112上且与像素电极114间隔设置。连接电极113覆盖住第二通孔116和第三通孔117的孔壁,使得屏蔽电极110和公共电极102通过连接电极113电连接。应当理解的是,通过本实施例所制成的阵列基板,其特征和功效相似于前述的阵列基板100,在此不加以赘述。

46.综上所述,本技术通过在数据线与像素电极之间设置屏蔽电极可起到屏蔽数据线和像素电极之间的电场的效果,使得不需要在数据线与像素电极之间设置不透光金属电极,进而可有效地提高显示面板的开口率。其次,通过设置屏蔽电极可有效地降低数据线与像素电极之间的耦合电容,进而解决电容串扰和垂直串扰的问题。再者,通过将屏蔽电极和公共电极电连接以形成网格状公共电极,可避免被数据线引响而导致电位恢复较慢,进而解决水平串扰的问题。此外,由于屏蔽电极整面地设置在显示面板的透光区域,并且与像素电极有极大的重叠面积,故可有效地增加存储电容,进而解决vrr技术中因为像素电压降增加而导致的负面问题。

47.以上对本技术实施例所提供的一种显示面板、阵列基板及其制造方法进行了详细介绍。本文中应用了具体实施例对本技术的原理及实施方式进行了阐述。以上实施例的说

明只是用于帮助理解本技术的技术方案及其核心思想。本领域的普通技术人员应当理解,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。