1.本发明涉及光电技术领域,尤其涉及一种硅光调制器及其形成方法。

背景技术:

2.光调制器是高速光通信的关键器件,也是最重要的集成光学器件之一。它是通过电压或电场的变化调制输出光的折射率、吸收率、振幅或相位的器件。它所依据的基本理论是各种不同形式的电光效应、声光效应、磁光效应、载流子色散效应等。硅光调制器与互补金属氧化物半导体(cmos)制造技术兼容,同时拥有电子和光子的优点。

3.具体地,硅光调制器可以实现高速的数据调制,是硅光芯片的核心器件,为了实现高速传输通常采用载流子耗尽的调制机制,例如采用行波电极的马赫-曾德(mach-zehnder,mz)调制器(modulators)结构。

4.在现有的硅光调制器中,微波信号一般加载在输入端,沿着调制臂方向,由于微波损耗和金属信号线本身电阻的存在,随着微波信号的传播,调制器的驱动电压逐渐减小。然而,现有的硅光调制器容易造成传输方向pn结电学参数的变化,从而影响调制器的调制效率、器件带宽及整体性能。

5.亟需一种硅光调制器的形成方法,能够在沿脊型结构的轴向方向上,降低硅光调制器的pn结电学参数的变化,优化调制器的调制效率、器件带宽及整体性能。

技术实现要素:

6.本发明解决的技术问题是提供一种硅光调制器及其形成方法,可以在沿脊型结构的轴向方向上,保持pn结性能参数的稳定,从而保证调制器沿轴向有均匀的特征阻抗和群折射率,进而提高调制器的调制效率、器件带宽及整体性能。

7.为解决上述技术问题,本发明实施例提供一种硅光调制器的形成方法,包括:提供半导体衬底;在所述半导体衬底的表面进行刻蚀以得到脊型结构,所述脊型结构具有多段掺杂区域,每段掺杂区域具有相邻的p型掺杂区域以及n型掺杂区域,且所述各段掺杂区域之间具有间隔;其中,沿所述脊型结构的轴向方向,各段掺杂区域的长度逐渐增大。

8.可选的,沿所述脊型结构的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大。可选的,所述脊型结构沿轴向方向被划分为多个预设长度的长度周期,所述长度周期与所述多段掺杂区域一一对应,且所述多段掺杂区域分别落入对应的长度周期内;其中,在沿所述脊型结构的轴向方向的各个长度周期内,掺杂区域的长度与剩余区域的长度的比例逐渐增大。

9.可选的,在沿所述脊型结构的轴向方向的各个长度周期内,所述掺杂区域的长度与剩余区域的长度的比例记为掺杂比例;在每个长度周期内,掺杂比例与输入信号的电压衰减比例呈正比。

10.可选的,所述的硅光调制器的形成方法还包括:形成第一电极和第二电极,所述第一电极电连接至所述p型掺杂区域,所述第二电极电连接至所述n型掺杂区域;其中,所述第

一电极为阳极电极以及阴极电极中的一种,所述第二电极为阳极电极以及阴极电极中的另一种。

11.可选的,所述阳极电极电连接至所述p型掺杂区域的第三浓度掺杂区,所述阴极电极电连接至所述n型掺杂区域的第三浓度掺杂区。

12.可选的,所述硅光调制器为马赫-曾德硅光调制器,所述脊型结构的轴向方向为所述马赫-曾德硅光调制器的调制臂方向。

13.为解决上述技术问题,本发明实施例提供一种硅光调制器,包括:脊型结构,所述脊型结构是对半导体衬底的表面进行刻蚀得到的;多段掺杂区域,位于所述脊型结构内,每段掺杂区域具有相邻的p型掺杂区域以及n型掺杂区域,且所述各段掺杂区域之间具有间隔;其中,沿所述脊型结构的轴向方向,各段掺杂区域的长度逐渐增大。

14.可选的,沿所述脊型结构的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大。

15.可选的,所述脊型结构沿轴向方向被划分为多个预设长度的长度周期,所述长度周期与所述多段掺杂区域一一对应,且所述多段掺杂区域分别落入对应的长度周期内;其中,在沿所述脊型结构的轴向方向的各个长度周期内,掺杂区域的长度与剩余区域的长度的比例逐渐增大。

16.与现有技术相比,本发明实施例的技术方案具有以下有益效果:

17.在本发明实施例中,通过设置沿硅光调制器的脊型结构的轴向方向,脊型结构具有多段掺杂区域,且所述各段掺杂区域之间具有间隔,各段掺杂区域的长度逐渐增大,可以在沿脊型结构的轴向方向上,增加pn结的结面积占比,补偿pn结区高速信号的电压衰减,从而保证高速信号沿着调制臂的传输过程中,pn结被均匀的调制,从而保证特征阻抗的稳定和微波折射率的稳定,减小阻抗失配,折射率匹配和提高调制效率,进而提升调制器的带宽。

18.进一步,设置沿所述脊型结构的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大,从而可以根据输入信号的电压衰减情况,确定pn结的结面积占比增大的程度,进而实施本发明实施例中的方案,实现减小阻抗失配,提高调制效率,进而提升调制器的带宽。

19.进一步,设置所述脊型结构沿轴向方向被划分为多个预设长度的长度周期,所述长度周期与所述多段掺杂区域一一对应,且所述多段掺杂区域分别落入对应的长度周期内,在沿所述脊型结构的轴向方向的各个长度周期内,掺杂区域的长度与剩余区域的长度的比例逐渐增大。采用本发明实施例的方案,可以采用长度周期更好地控制掺杂区域的长度增大程度,进一步实现减小阻抗失配,提高调制效率,进而提升调制器的带宽。

20.进一步,设置在每个长度周期内,掺杂比例与输入信号的电压衰减比例呈正比,可以根据在各个长度周期内输入信号的电压衰减情况,更准确地确定在该长度周期内掺杂区域的长度增大的程度,进一步有效实现减小阻抗失配,提高调制效率,进而提升调制器的带宽。

附图说明

21.图1是本发明实施例中一种硅光调制器的形成方法的流程图;

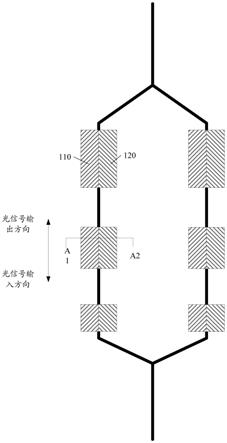

22.图2是本发明实施例中一种硅光调制器的顶视图;

23.图3是图2中沿切割线a1-a2的剖面图;

24.图4是本发明实施例中另一种硅光调制器的顶视图;

25.图5是本发明实施例中又一种硅光调制器的剖面结构示意图。

具体实施方式

26.如前所述,在现有的硅光调制器中,微波信号一般加载在输入端,沿着调制臂方向,由于微波损耗和金属信号线本身电阻的存在,随着微波信号的传播,调制器的驱动电压逐渐减小。然而,现有的硅光调制器具有带宽降低和调制效率较低的问题。

27.本发明的发明人经过研究发现,随着驱动电压的减小,沿着波导传输方向上的pn结区的rc常数也会发生变化,从而造成调制器的特征阻抗和群折射率发生变化,特征阻抗的变化会带来阻抗失配,引起反射的问题,恶化眼图质量,降低消光比;群折射率的变化会带来群速度失配,信号不能被有效调制,降低带宽;同时,由于驱动电压的逐渐降低,沿轴向的被调制的电容改变量逐渐减小,导致相位变化积分逐渐饱和,降低调制效率。

28.在本发明实施例中,通过设置沿硅光调制器的脊型结构的轴向方向,脊型结构具有多段掺杂区域,且所述各段掺杂区域之间具有间隔,各段掺杂区域的长度逐渐增大,可以在沿脊型结构的轴向方向上,增加pn结的结面积占比,补偿pn结区高速信号的电压衰减,从而保证高速信号沿着调制臂的传输过程中,pn结被均匀的调制,从而保证特征阻抗的稳定和微波折射率的稳定,减小阻抗失配,折射率匹配和提高调制效率,进而提升调制器的带宽。

29.为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

30.参照图1,图1是本发明实施例中一种硅光调制器的形成方法的流程图。所述硅光调制器的形成方法可以包括步骤s11至步骤s12:

31.步骤s11:提供半导体衬底;

32.步骤s12:在所述半导体衬底的表面进行刻蚀以得到脊型结构,所述脊型结构具有多段掺杂区域,每段掺杂区域具有相邻的p型掺杂区域以及n型掺杂区域,且所述各段掺杂区域之间具有间隔;其中,沿所述脊型结构的轴向方向,各段掺杂区域的长度逐渐增大。

33.下面结合图2和图3对上述各个步骤进行说明。

34.结合参照图2和图3,图2是本发明实施例中一种硅光调制器的顶视图,图3是图2中沿切割线a1-a2的剖面图。

35.在具体实施中,提供半导体衬底,在所述半导体衬底的表面进行刻蚀以得到脊型结构100。

36.具体地,所述半导体衬底可以是在初始半导体衬底的表面形成硅材料层得到的。

37.进一步地,所述初始半导体衬底可以为硅衬底,或者所述初始半导体衬底的材料还可以包括锗、锗化硅、碳化硅、砷化镓或镓化铟,所述初始半导体衬底还可以为绝缘体上的硅衬底或者绝缘体上的锗衬底,或者是生长有外延层(epitaxy layer,epi layer)的衬底。

38.进一步地,所述硅光调制器可以为马赫-曾德硅光调制器,所述马赫-曾德硅光调

制器的调制臂可以包括所述脊型结构100。所述脊型结构100的轴向方向可以为所述马赫-曾德硅光调制器的调制臂方向。

39.需要指出的是,所述脊型结构100可以包括刻蚀后得到的凹陷部,以及凸起的凸出部,所述凸出部用于在掺杂离子后形成脊光波导,对输入的光信号进行传输。

40.进一步地,可以对所述脊型结构100进行离子注入,以得到相邻的p型掺杂区域110以及n型掺杂区域120。其中,由相邻位置起,所述p型掺杂区域110以及n型掺杂区域120均依次包括第一浓度掺杂区111(121)、第二浓度掺杂区112(122)、第三浓度掺杂区113(123)。

41.在本发明实施例的一种具体实施方式中,从第一浓度掺杂区111(121)至第三浓度掺杂区113(123)的掺杂浓度可以依次增大。

42.具体而言,p型掺杂区域110的第一浓度掺杂区111与n型掺杂区域120的第一浓度掺杂区121的掺杂浓度最小,又可以称为轻掺杂区。由于第一浓度掺杂区111与第一浓度掺杂区121相邻,则可以在相邻位置形成pn结。在本发明实施例的一种具体实施方式中,所述第一浓度掺杂区111(121)在刻蚀区的宽度又可以称为中掺脊边距。

43.需要指出的是,沿所述脊型结构的轴向方向,pn结的调制均匀性是保证特征阻抗的稳定和微波折射率的稳定的重要因素。然而在现有技术中,高速行波信号在传输过程中会存在微波损耗和电压衰减,随着驱动电压的减小,沿着波导传输方向上的pn结区的rc常数也会发生变化,从而引起折射率失配、阻抗失配和调制效率下降的问题。

44.其中,p型掺杂区域110的第二浓度掺杂区112的掺杂浓度比第一浓度掺杂区111的掺杂浓度高,以及n型掺杂区域120的第二浓度掺杂区122的掺杂浓度比第一浓度掺杂区121的掺杂浓度高,所述p型掺杂区域110的第二浓度掺杂区112以及n型掺杂区域120的第二浓度掺杂区122又可以称为中掺杂区。

45.需要指出的是,第二浓度掺杂区112(122)可以包含多级掺杂,例如邻近第一浓度掺杂区111(121)采用第一级掺杂,邻近第三浓度掺杂区采用第二级掺杂。其中,第一级掺杂的掺杂浓度可以大于第一浓度掺杂区111(121)的掺杂浓度,第二级掺杂的掺杂浓度可以大于第一级掺杂的掺杂浓度,且第二级掺杂的掺杂浓度可以小于第三浓度掺杂区113(123),从而在多级掺杂的情况下,仍然保持由相邻位置起,第一浓度掺杂区111(121)、第二浓度掺杂区112(122)的多级掺杂、第三浓度掺杂区113(123)的掺杂浓度依次增大。

46.在本发明实施例中,通过设置第二浓度掺杂区112(122)包含多级掺杂,可以不仅限于一种浓度的掺杂,有助于优化电阻性能。

47.其中,p型掺杂区域110的第三浓度掺杂区113的掺杂浓度比第二浓度掺杂区112的掺杂浓度高,以及n型掺杂区域120的第三浓度掺杂区123的掺杂浓度比第二浓度掺杂区122的掺杂浓度高,所述p型掺杂区域110的第三浓度掺杂区113以及n型掺杂区域120的第三浓度掺杂区123又可以称为重掺杂区。

48.在本发明实施例中,沿所述脊型结构100的轴向方向,所述脊型结构100具有多段掺杂区域,每段掺杂区域具有相邻的p型掺杂区域以及n型掺杂区域,且所述各段掺杂区域之间具有间隔,并且沿所述脊型结构100的轴向方向,各段掺杂区域的长度逐渐增大。

49.其中,所述各段掺杂区域的长度增大的方向为从光信号输入方向至光信号输出方向。

50.在本发明实施例中,通过设置沿硅光调制器的脊型结构100的轴向方向,脊型结构

100具有多段掺杂区域,且所述各段掺杂区域之间具有间隔,各段掺杂区域的长度逐渐增大,可以在沿脊型结构100的轴向方向上,增加pn结的结面积占比,补偿pn结区高速信号的电压衰减,从而保证高速信号沿着调制臂的传输过程中,pn结被均匀的调制,从而保证特征阻抗的稳定和微波折射率的稳定,减小阻抗失配,折射率匹配和提高调制效率,进而提升调制器的带宽。

51.可以理解的是,本发明实施例中的技术方案设计复杂度较低,成本较低,不需要引入额外的控制电路和电学补偿,且能够有效提升调制器的性能。

52.需要指出的是,在本发明实施例中,可以先进行刻蚀处理以得到脊形结构100,再进行离子注入;还可以先进行离子注入,再对离子注入后的半导体衬底进行刻蚀处理,以得到脊型结构。

53.进一步地,沿所述脊型结构100的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大。

54.具体地,高速行波信号在传输过程中会存在微波损耗和电压衰减,导致越远离光信号输入方向,驱动电压越小。

55.在本发明实施例中,设置沿所述脊型结构100的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大,从而可以根据输入信号的电压衰减情况,确定pn结的结面积占比增大的程度,进而实施本发明实施例中的方案,实现减小阻抗失配,提高调制效率,进而提升调制器的带宽。

56.参照图4,图4是本发明实施例中另一种硅光调制器的顶视图。所述脊型结构沿轴向方向被划分为多个预设长度的长度周期l,所述长度周期l与所述多段掺杂区域一一对应,且所述多段掺杂区域分别落入对应的长度周期内l,其中,在沿所述脊型结构的轴向方向的各个长度周期l内,掺杂区域d1的长度与剩余区域d2的长度的比例逐渐增大。

57.如图4所示,在临近光信号输入方向上,在长度周期l内,掺杂区域d1的长度较小,剩余区域d2的长度较大;在临近光信号输出方向上,在长度周期l内,掺杂区域d1的长度较大,剩余区域d2的长度较小。

58.其中,剩余区域d2可以等于长度周期l-掺杂区域d1。

59.进一步地,在沿所述脊型结构的轴向方向的各个长度周期l内,所述掺杂区域d1的长度与剩余区域d2的长度的比例记为掺杂比例;在每个长度周期内,掺杂比例与输入信号的电压衰减比例呈正比。

60.其中,掺杂比例可以等于d1/d2。

61.在本发明实施例中,设置在每个长度周期l内,掺杂比例与输入信号的电压衰减比例呈正比,可以根据在各个长度周期l内输入信号的电压衰减情况,更准确地确定在该长度周期l内掺杂区域的长度增大d1的程度,进一步有效实现减小阻抗失配,提高调制效率,进而提升调制器的带宽。

62.在本发明实施例中,设置所述脊型结构沿轴向方向被划分为多个预设长度的长度周期l,所述长度周期l与所述多段掺杂区域一一对应,且所述多段掺杂区域d1分别落入对应的长度周期l内,在沿所述脊型结构的轴向方向的各个长度周期l内,掺杂区域d1的长度与剩余区域d2的长度的比例逐渐增大。采用本发明实施例的方案,可以采用长度周期l更好地控制掺杂区域的长度增大程度,进一步实现减小阻抗失配,提高调制效率,进而提升调制

器的带宽。

63.参照图5,图5是本发明实施例中又一种硅光调制器的剖面结构示意图。

64.如图5所示,在图3示出的硅光调制器的基础上,还可以形成第一电极和第二电极,所述第一电极电连接至所述p型掺杂区域110,所述第二电极电连接至所述n型掺杂区域120,其中,所述第一电极为阳极电极以及阴极电极中的一种,所述第二电极为阳极电极以及阴极电极中的另一种。

65.具体地,可以形成图5所示的分别电连接至所述p型掺杂区域110以及所述n型掺杂区域120的阳极电极140以及阴极电极141。

66.其中,p型掺杂区域110可以是经由插塞(contact)130与阳极电极140连接的,n型掺杂区域120可以是经由插塞130与阴极电极141连接的。

67.进一步地,所述阳极电极140可以电连接至所述p型掺杂区域110的第三浓度掺杂区113,所述阴极电极141可以电连接至所述n型掺杂区域120的第三浓度掺杂区123。

68.在本发明实施例中,通过设置阳极电极140以及阴极电极141,可以实现从外界输入电压对所述硅光调制器进行电学性能控制,且有助于提高与现有的包含双电极结构的硅光调制器的一致性。

69.在本发明实施例中,还公开了一种硅光调制器,如图4及图5所示,可以包括:脊型结构100,所述脊型结构100是对半导体衬底的表面进行刻蚀得到的;多段掺杂区域,位于所述脊型结构100内,每段掺杂区域具有相邻的p型掺杂区域110以及n型掺杂区域120,且所述各段掺杂区域之间具有间隔;其中,沿所述脊型结构100的轴向方向,各段掺杂区域的长度逐渐增大。

70.进一步地,沿所述脊型结构100的轴向方向,输入信号的电压衰减比例越大,各段掺杂区域的长度增大的比例越大。

71.进一步地,所述脊型结构100沿轴向方向被划分为多个预设长度的长度周期l,所述长度周期l与所述多段掺杂区域一一对应,且所述多段掺杂区域分别落入对应的长度周期l内;其中,在沿所述脊型结构100的轴向方向的各个长度周期l内,掺杂区域的长度d1与剩余区域的长度d2的比例逐渐增大。

72.在本发明实施例中,通过设置沿硅光调制器的脊型结构100的轴向方向,脊型结构100具有多段掺杂区域,且所述各段掺杂区域之间具有间隔,各段掺杂区域的长度逐渐增大,可以在沿脊型结构100的轴向方向上,增加pn结的结面积占比,补偿pn结区高速信号的电压衰减,从而保证高速信号沿着调制臂的传输过程中,pn结被均匀的调制,从而保证特征阻抗的稳定和微波折射率的稳定,减小阻抗失配,折射率匹配和提高调制效率,进而提升调制器的带宽。

73.关于该硅光调制器的原理、具体实现和有益效果请参照前文描述的关于硅光调制器的形成方法的相关描述,此处不再赘述。

74.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。