1.本发明涉及半导体封装领域,特别涉及封装结构的制作方法及封装结构。

背景技术:

2.随着半导体技术的日益发展,具有高的集成密度的封装结构越来越重要。例如,采用3d封装结构可以实现芯片与芯片之间的相互堆叠。

3.目前现有的硅基光电集成芯片中的电芯片(电子集成芯片,eic,electronic integrated chip)和光芯片(光子集成芯片pic,photonic integrated chip)由于采用不同的晶圆生成工艺制程,采用芯片级别的互连(例如打线或倒装的互连方式)来实现电芯片(eic)与光芯片(pic)之间的连接,形成三维互连结构。

4.在光芯片(pic)和电芯片(eic)的三维封装中,为了避免打薄光芯片(pic)时造成翘曲从而导致光芯片(pic)和电芯片(eic)的连接点错位或失效,或者为了使光芯片(pic)和电芯片(eic)的封装具有较高的强度,通常需要在光芯片(pic)表面形成塑封层。然而,光芯片(pic)具有用于输入光的光纤耦合接口,直接对光芯片(pic)的表面进行塑封会导致光纤耦合界面的损坏,从而导致光纤耦合接口的插入损耗大幅增加并影响光电芯片的实际使用。

技术实现要素:

5.为了克服现有技术的不足,本发明的目的在于提供一种封装结构的制作方法及封装结构,其可以在使用塑封材料固定光电集成芯片以提高封装强度和避免光芯片翘曲的同时,实现对光芯片上的光纤耦合接口的保护。

6.本发明的目的采用以下技术方案实现:根据本发明的一方面,提供一种封装结构的制作方法,所述方法包括:提供第一半导体芯片,所述第一半导体芯片是光子集成芯片,所述第一半导体芯片包括光纤耦合区以及设置在所述光纤耦合区内的光耦合接口;在所述光纤耦合区上制作覆盖所述光纤耦合区的保护层;制作塑封层,并对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理,以露出所述保护层背离所述光纤耦合区的一侧表面;去除覆盖于所述光纤耦合区上的所述保护层。

7.可选地,在所述制作塑封层之前,提供至少一个第二半导体芯片,并将所述至少一个第二半导体芯片固定在所述第一半导体芯片上方,其中,所述第二半导体芯片是电子集成芯片。

8.可选地,在将所述至少一个第二半导体芯片固定在第一半导体芯片上之前,在所述第一半导体芯片内制作多个金属连接柱,并将每个所述金属连接柱的一侧表面从所述第一半导体芯片的表面露出。

9.进一步地,在将每个所述金属连接柱的一侧表面从所述第一半导体芯片的表面露出之后,在每个所述金属连接柱露出的表面上制作第一导电凸点。

10.进一步地,在将所述至少一个第二半导体芯片固定在第一半导体芯片上之前,在所述至少一个第二半导体芯片的一侧制作多个第二导电凸点,其中,所述多个第二导电凸点与每个所述金属连接柱上的第一导电凸点一一对应。

11.进一步地,将每个所述第二导电凸点与对应的所述第一导电凸点相键合,以将所述至少一个第二半导体芯片与所述第一半导体芯片连接在一起。

12.进一步地,在将所述至少一个第二半导体芯片与所述第一半导体芯片连接在一起之后,在所述至少一个第二半导体芯片和所述保护层的表面以及所述第一半导体芯片朝向所述至少一个第二半导体芯片的剩余表面上制作塑封层,所述塑封层包覆所述至少一个第二半导体芯片和所述保护层并完全覆盖所述第一半导体芯片朝向所述至少一个第二半导体芯片的一侧表面。

13.进一步地,在所述塑封层制作完成之后,在所述第一半导体芯片远离所述至少一个第二半导体芯片的一侧对所述第一半导体芯片的本体进行减薄处理,以露出所述金属连接柱远离所述至少一个第二半导体芯片一侧的表面。

14.进一步地,在露出所述金属连接柱远离所述至少一个第二半导体芯片一侧的表面之后,将所述第一半导体芯片远离所述光纤耦合区的一侧表面与第一承载基板进行临时键合。

15.进一步地,在将所述第一半导体芯片与所述第一承载基板临时键合后,对所述塑封层进行减薄处理,以露出所述至少一个第二半导体芯片背离所述第一半导体芯片的一侧表面,并随之对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理。

16.进一步地,在所述塑封层制作完成之后,对所述塑封层进行减薄处理,以露出所述至少一个第二半导体芯片背离所述第一半导体芯片的一侧表面。

17.进一步地,在露出所述第二半导体芯片背离所述第一半导体芯片的一侧表面后,将所述塑封层远离所述第一半导体芯片的一侧表面以及所述第二半导体芯片远离所述第一半导体芯片的一侧表面与第二承载基板临时键合。

18.进一步地,在将所述塑封层远离所述第一半导体芯片的一侧表面以及所述第二半导体芯片远离所述第一半导体芯片的一侧表面与第二承载基板临时键合之后,在所述第一半导体芯片远离所述第二半导体芯片的一侧对所述第一半导体芯片的本体进行减薄处理,以露出所述金属连接柱远离所述第二半导体芯片一侧的表面。

19.进一步地,在露出所述金属连接柱远离所述第二半导体芯片一侧的表面之后,将所述第一半导体芯片与第一承载基板临时键合。

20.进一步地,在将每个所述第一半导体芯片与第一承载基板临时键合之后,将所述第二承载基板解键合,以露出所述塑封层,并对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理。

21.进一步地,在去除覆盖于所述光纤耦合区上的所述保护层之后,将所述第一承载基板解键合。

22.进一步地,在去除覆盖于所述光纤耦合区上的所述保护层之后,将导光结构或者激光器芯片安装至所述光耦合接口上。所述导光结构是光纤阵列或者棱镜,当所述导光结构是棱镜时,通过激光整合的方式将激光束引导到光耦合接口。

23.进一步地,所述保护层是不透光材料的非有机材料层,所述不透光材料与第一半

导体芯片的基材具有高的刻蚀选择比。

24.可选地,所述保护层是不透光的无机材料层。

25.可选地,所述保护层是不透光的金属层。

26.可选地,所述保护层与所述第一导电凸点采用同一材料在同一形成工艺中形成。

27.可选地,所述去除覆盖于所述光纤耦合区上的所述保护层的方法包括:采用干法刻蚀工艺、湿法刻蚀工艺中的至少一种去除覆盖于所述光纤耦合区上的所述保护层。

28.根据本发明实施例的另一方面,还提供一种封装结构,包括:第一半导体芯片,所述第一半导体芯片包括第一表面,在所述第一表面的第一区域设置有光纤耦合区,所述光纤耦合区内设置有光耦合接口;保护层,所述保护层设置在所述第一表面的第一区域,并且在所述光纤耦合区设置有贯通所述保护层的开口;塑封层,所述塑封层位于所述第一表面上以及所述保护层上,所述开口不被所述塑封层填充和覆盖。

29.可选地,还包括:至少一个第二半导体芯片,所述至少一个第二半导体芯片固定在所述第一表面的第二区域,其中,所述第二半导体芯片是电子集成芯片。

30.进一步地,所述保护层是不透光材料的非有机材料层,所述不透光材料与所述第一半导体芯片的基材具有高的刻蚀选择比。

31.进一步地,所述保护层是不透光的无机材料层。

32.进一步地,所述保护层是不透光的金属层。

33.本发明实施例提供的封装结构的制作方法及封装结构,由于在第一半导体芯片的光纤耦合区上制作覆盖所述光纤耦合区的不透光的保护层,避免有机物材料直接接触光纤耦合区,故在对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理时,保护层能够阻挡高能量的激光进入光纤耦合区,能够保护光耦合接口不被激光损伤,在对覆盖于光纤耦合区上的塑封层进行开孔处理后,可以利用现有的蚀刻技术去除覆盖于光纤耦合区上的保护层,防止光耦合接口不被激光损伤的同时,由于光纤耦合区不直接接触有机物,还保证了光纤耦合区的表面纯净,有利于后续光耦合接口能够与光纤阵列维持较高的耦合效率。

附图说明

34.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的实施方式。

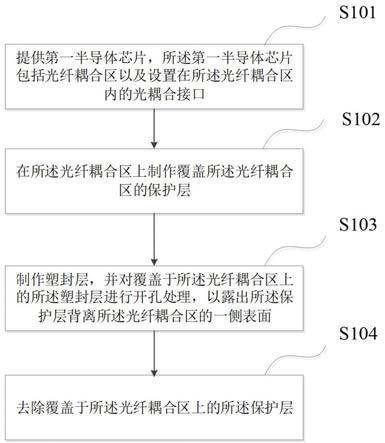

35.图1是根据本发明实施例的封装结构的制作方法的流程图。

36.图2a-图2d是根据本发明一实施例提供的封装结构的制作方法的制造工序示意图。

37.图3a-图3g是根据本发明又一实施例提供的封装结构的制作方法的制造工序示意图。

38.图4是根据本发明实施例一种封装结构的部分示意图。

39.图5a-图5i是根据本发明另一实施例提供的封装结构的制作方法的制造工序示意图。

40.图6是根据本发明实施例提出的封装结构与封装基板连接的示意图。

41.图7是根据本发明实施例提出的封装结构与导光结构连接的示意图。

42.图8是根据本发明的又一实施例提供的封装结构的部分剖面结构示意图。

43.图9是根据图8中的去除塑封层后的部分俯视结构示意图。

具体实施方式

44.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

45.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接或可以相互通讯;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

46.针对现有的光电芯片封装方式存在无法进行塑封、封装互连的可靠性较差、封装面积较大以及性能较差等问题,本发明实施例提出了一种带有光互连接口的封装结构的制作方法,采用将电芯片与光芯片堆叠后进行塑封,保证了封装互连的可靠性,同时又实现了光纤耦合接口的保护。

47.为使本发明的目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

48.图1是根据本发明实施例的封装结构的制作方法的流程图。所述封装结构的制作方法包括:s101,提供第一半导体芯片,所述第一半导体芯片是光子集成芯片,所述第一半导体芯片包括光纤耦合区以及设置在所述光纤耦合区内的光耦合接口;s102,在所述光纤耦合区上制作覆盖所述光纤耦合区的保护层;s103,制作塑封层,并对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理,以露出所述保护层背离所述光纤耦合区的一侧表面;s104,去除覆盖于所述光纤耦合区上的所述保护层。

49.图2a-图2d是根据本发明一实施例提供的封装结构的制作方法的制造工序示意图。以下将结合图2a-图2d对本发明实施例进行详细说明。

50.在本发明实施例中,示例性地,所述第一半导体芯片102是光芯片(光子集成电路芯片,pic),其中,所述光芯片是用光子为信息载体进行信息的处理与数据的传送,其可以是基于硅的光芯片,所述第二半导体芯片103是电芯片(电子集成电路芯片,eic),其中,所述电芯片是用电子为信息载体进行信息的处理与数据的传送,例如基于硅的电芯片、基于锗的电芯片或者化合物半导体电芯片,通过将所述第一半导体芯片102和所述第二半导体芯片103进行堆叠可实现光芯片和电芯片的集成。

51.所述第一半导体芯片102包括光纤耦合区1024以及设置在所述光纤耦合区1024内的光耦合接口104,外部光源提供的光可以通过光纤阵列(fiber array,fa)输入到光耦合接口104中,例如通过与光耦合接口104内的光栅耦合器耦合进第一半导体芯片102,光耦合进第一半导体芯片102之后继续以光子进行传输数据以及信息处理。需要说明的是,在其他

实施例中,也可以在光耦合接口104内相应的设置其他用于传输光信号的光互连接口或者器件。

52.由于塑封层等由有机物材料构成,有机物接触光纤耦合区会导致有机物残留,有机物残留会严重影响光耦合接口的耦合效率,导致光损耗严重,影响第一半导体芯片的运行。为了形成对光纤耦合区1024内的光耦合接口104的保护,本发明的实施例在所述光纤耦合区1024的上方制作覆盖所述光纤耦合区1024的保护层105,所述保护层105的材料选自不透光的非有机材料,例如二氧化钛等非金属氧化物、al等金属材料,假若所述保护层105的材料为有机材料,例如光刻胶(光阻),光刻胶(光阻)一般通过涂布工艺整面涂布,然后通过光刻掩膜工艺,去除不需要的部分,以及保留需要的部分(保留覆盖所述光纤耦合区1024的部分);由于在对塑封层106开孔处理完成后,还需要对遮挡所述光纤耦合区1024的保护层105进行去除。在去除光阻的过程中,光刻胶(光阻)的有机物分子只有在经过uv光照处理后才能形成易溶解于显影液的结构,对于正性光阻而言,在经过uv光照后处理后,正性光阻的有机物分子中的苯环上的羟基才会转变为羧基,而显影液是碱性的,正性光阻的有机物分子中的苯环上的羧基能够与碱性的显影液产生反应。但是,由于光纤耦合区1024的表面构造不平坦,容易导致部分正性光阻无法参与uv光照反应,而未被uv光照反应的光刻胶(光阻)则无法溶解于显影液,故最终可能无法被完全清除,导致残留的光刻胶(光阻)残留在光纤耦合区1024上,影响了后续光耦合接口104与光纤阵列(fiber array,fa)之间的耦合效率。

53.而本发明由于采用了非有机材料的保护层105,所述保护层105不透光,故不仅避免了有机物与光纤耦合区1024的直接接触,阻挡了高能量的激光透过保护层105入射到光纤耦合区1024,防止在对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理时所使用到的激光对位于孔下方的光纤耦合区1024造成不必要的损伤。而且,所述保护层105与第一半导体芯片102的基材相比还具有较高的刻蚀选择比,以便于在对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理后,能够采用现有的刻蚀工艺对其进行清除处理,防止了有机物在光纤耦合区的残留,以保证光纤耦合区1024的上表面纯净无其他杂质和异物,使后续光耦合接口104能够与光纤阵列(fiber array,fa)维持较高的耦合效率。较佳地,所述保护层105具有200nm-5μm的厚度,在该厚度范围的所述保护层105能够较好地阻挡激光进入到光纤耦合区,并且后续可以容易地采用刻蚀方式去除所述光纤耦合区上方的所述保护层。去除覆盖于所述光纤耦合区上的保护层105的方法包括:采用干法刻蚀工艺、湿法刻蚀工艺中的至少一种去除覆盖于所述光纤耦合区上的所述保护层。

54.优选地,所述保护层105为金属材料,例如,铝、钛、铜、以及铝或者钛的合金等材料,采用金属材料制作的保护层,一方面,由于金属膜不透光,能够防止在对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理时所使用到的激光对位于孔下方的光纤耦合区1024造成不必要的损伤,另一方面,金属膜可以采用pvd(physical vapor deposition)等镀膜技术制作,金属膜的附着性及粘附力较佳,能够完全覆盖并保护所述光纤耦合区1024,并且金属膜具有较高的刻蚀选择比,在完成对覆盖于所述光纤耦合区1024上的所述塑封层106的开孔处理后,可以利用湿蚀刻技术去除覆盖在所述光纤耦合区1024表面的金属膜以露出所述光纤耦合区1024,以保证所述光纤耦合区1024在整个封装过程中不被污染和损伤。

55.示例性地,如图2a所示,本发明实施例提供的封装结构的制作方法还包括:提供第二半导体芯片103,并将所述第二半导体芯片103固定在第一半导体芯片102上方。例如可以采用焊接或者其他方式进行固定。本实施例中示意了在所述第一半导体芯片102上方形成一个所述第二半导体芯片103,在实际使用中,可以是多于一个的所述第二半导体芯片103,例如2个、3个、4个或者更多,可以根据实际需要灵活选择。

56.在将所述第二半导体芯片103固定在所述第一半导体芯片102上之前,在所述第一半导体芯片102内制作多个金属连接柱1022,并将每个所述金属连接柱1022的一侧表面从所述第一半导体芯片102朝向所述第二半导体芯片103的一侧表面露出。

57.具体地,当第一半导体芯片102为基于硅的光芯片时,在第一半导体芯片102内制作多个导电通孔,该导电通孔也可称之为“硅通孔”(through silicon via,tsv),tsv是一项高密度封装技术,正在逐渐取代目前工艺比较成熟的引线键合技术,被认为是第四代封装技术。tsv技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。硅通孔技术可以通过垂直互连减小互联长度,减小信号延迟,降低电容/电感,实现芯片间的低功耗、高速通信,增加宽带和实现器件集成的小型化。tsv工艺可以包括深硅刻蚀形成微孔或盲孔、绝缘层/阻挡层/种子层的沉积、深孔填充、化学机械抛光、减薄、以及再分布引线制备等工艺技术,在光芯片中形成导电通孔的工艺方法包括但不限于激光刻蚀、深反应离子刻蚀等,在形成导电通孔后再采用例如深孔填充等工艺进行导电材料(例如金属)的填充。本发明在此不再赘述。

58.如图2b所示,在将每个所述金属连接柱1022的一侧表面从所述第一半导体芯片102朝向第二半导体芯片103的一侧表面露出之后,在每个所述金属连接柱1022露出的表面上制作第一导电凸点1023。该第一导电凸点1023例如是焊盘(金属凸块)或焊球等。在每个所述金属连接柱1022露出的表面上制作第一导电凸点1023,以实现所述金属连接柱1022与外部电连接点进行电连接。

59.可选地,为了实现将所述第一半导体芯片102的导电焊盘的位置重选分布,也可以在所述第一半导体芯片102的上方制作重布线层(图未示出),在其中一个实施例中,所述重布线层可以为单层重布线层也可以是多层重布线层。

60.在所述第二半导体芯片103的一侧制作多个第二导电凸点1033,其中,所述多个第二导电凸点1033与每个所述金属连接柱1022上的第一导电凸点1023一一对应。将每个所述第二导电凸点1033与对应的所述第一导电凸点1023相键合,以将所述第二半导体芯片103与所述第一半导体芯片102连接在一起。

61.本发明实施例中,所述第二半导体芯片103采用倒装焊接的方式焊接到所述第一半导体芯片102上。将每个所述第二导电凸点1033与对应的所述第一导电凸点1023相键合,其键合的方式可以采用热压焊(tcb,thermal compress bonding)、回流焊、激光键合或者金属直接键合等方式。如果所述第二半导体芯片103有金属焊球或者金属凸块等,还需要做底部填充的工艺。应理解,根据实际需要,还可以将多颗第二半导体芯片103连接到同一颗第一半导体芯片102上。

62.需要说明的是,上述所述多个第二导电凸点1033与每个所述金属连接柱1022上的第一导电凸点1023一一对应是为了电信号端子连接时进行一一对应连接,并非完全限定为上、下投影位置上的一一对应。应理解,当所述多个第二导电凸点1033与每个所述金属连接

柱1022上的第一导电凸点1023、下投影位置也对应时,第一半导体芯片102与所述第二半导体芯片10上、下垂直互连,所需要的连接距离最短,因此,可以避免所述第一半导体芯片102与所述第二半导体芯片103之间由于连接线过长所引起的阻抗较大,限制了电流的通过能力等问题,从而减少了所述第一半导体芯片102与所述第二半导体芯片103上、下互连的损耗。

63.此外,如图2b-图2c所示,在所述第一半导体芯片102的每个所述金属连接柱1022露出的表面上制作第一导电凸点1023后,在所述第一半导体芯片102的光纤耦合区1024的上方制作保护层105;接着,将上述所述多个第二导电凸点1033与每个所述金属连接柱1022上的第一导电凸点1023一一对应进行键合,以将所述第二半导体芯片103与所述第一半导体芯片102连接在一起。作为可选的方案,可以先制作所述保护层105再制作所述第一导电凸点1023。作为可选的方案,制作保护层105的工艺与将所述第二半导体芯片103与所述第一半导体芯片102连接在一起的工艺顺序不做限制。当保护层选自与第一导电凸点1023相同的金属材料时,优选地,在制作所述第一导电凸点1023的时同步制作所述保护层105,即所述保护层105与所述第一导电凸点1023在同一镀膜工艺以及同一光刻制程下进行制作,以减少制作工艺的步骤。

64.如图2d所示,在将所述第二半导体芯片103与所述第一半导体芯片102连接在一起之后,在所述第二半导体芯片103和所述保护层105的表面以及所述第一半导体芯片102朝向所述第二半导体芯片103的剩余表面上制作塑封层106,所述塑封层106包覆所述第二半导体芯片103和所述保护层105并完全覆盖所述第一半导体芯片102朝向所述第二半导体芯片103的一侧表面。

65.可选地,对连接之后的第一半导体芯片102和第二半导体芯片103进行晶圆级塑封工艺,应理解,也可以根据实际需要采用液态或者颗粒状的塑封材料。

66.图3a-图3g是根据本发明又一实施例提供的封装结构的制作方法的制造工序示意图。

67.如图3a所示,在本实施例中,在所述塑封层106制作完成之后,在所述第一半导体芯片102远离所述第二半导体芯片103的一侧对所述第一半导体芯片102的本体进行减薄处理,以露出所述金属连接柱1022远离所述第二半导体芯片103一侧的表面。

68.具体地,对所述第一半导体芯片102的本体的减薄处理,使得所述金属连接柱1022远离所述第二半导体芯片103的一端能够露出所述第一半导体芯片102,以便于后续外部电连接点能够与所述金属连接柱1022进行电气连接。

69.如图3b所示,在每个所述金属连接柱1022远离所述第二半导体芯片103一侧的表面及其他预设的位置制作第三导电凸点107,将所述第一半导体芯片102远离所述光纤耦合区1024的一侧表面通过所述第三导电凸点107与第一承载基板200进行临时键合。

70.如图3c所示,在将所述第一半导体芯片102远离所述光纤耦合区1024的一侧表面与所述第一承载基板200临时键合后,对所述塑封层106进行减薄处理,以露出所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面。

71.具体地,对所述塑封层106的减薄处理,例如采用研磨的技术手段,将所述塑封层106研磨至与所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面平齐的位置。

72.如图3d、图3e所示,通过激光开孔的工艺对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理,以露出覆盖于所述光纤耦合区1024上的保护层105,所述保护层105可以为金属膜层,所述覆盖于所述光纤耦合区1024上的所述保护层105可作为光纤耦合区的保护层和激光烧蚀的停止层,基于所述保护层105覆盖的区域与激光开孔尺寸无法做到完全一致,为了保护第一半导体芯片102上的光耦合接口104不受开孔时激光的损坏,优选地,如图3e所示,该保护层105的尺寸设置得比激光开孔70的尺寸大。

73.当所述保护层105为金属膜层时,在去除光纤耦合区域1024上方露出的金属膜层时,可以根据不同的金属膜层种类,采用对应的湿法或者干法蚀刻工艺去除。

74.可选地,如图3f所示,通过对所述保护层105采用对应的湿法或者干法蚀刻工艺去除,以使得所述光纤耦合区1024露出。

75.可选地,如图3g所示,在露出所述保护层105背离所述第一半导体芯片102的一侧表面之后,在所述保护层105对应所述光纤耦合区1024的位置制作贯穿所述保护层105的开口80以使得所述光纤耦合区1024露出。

76.需要说明的是,上述对于封装结构的承载基板安排解键合,可以根据临时键合所选的材料,可以选择激光解键合、热机械解键合等方式。在对芯片封装结构进行解键合的前或后,可以进行后续的切割工艺,将承载在基板上的多个光电芯片的封装结构进行切割分离,分割为单颗光电芯片的封装结构。

77.图4是根据本发明实施例一种封装结构的部分示意图。

78.示例性地,如图4所示,在对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理并且去除覆盖于所述光纤耦合区1024上的所述保护层105之后,将所述第一承载基板200解键合。至此,可以得到具有所述第三导电凸点107的封装结构1000。

79.图5a-图5i是根据本发明另一实施例提供的封装结构的制作方法的制造工序示意图。

80.在本实施例中,制作塑封层106的步骤与图2a-2d相同,在此不再赘述,在所述塑封层106制作完成之后,如图5a所示,对所述塑封层106进行减薄处理,以露出所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面。

81.具体地,对所述塑封层106的减薄处理,例如采用研磨的手段,将所述塑封层106研磨至与所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面平齐的位置。

82.如图5b所示,在露出所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面后,将所述塑封层106远离所述第一半导体芯片102的一侧表面以及所述第二半导体芯片103远离所述第一半导体芯片102的一侧表面与第二承载基板300临时键合。

83.可选地,可在所述塑封层106远离所述第一半导体芯片102的一侧表面以及所述第二半导体芯片103远离所述第一半导体芯片102的一侧表面涂上胶层301与所述第二承载基板300临时键合,后续可以通过加热等方式进行键合分离。

84.如图5c所示,在将所述塑封层106远离所述第一半导体芯片102的一侧表面以及所述第二半导体芯片103远离所述第一半导体芯片102的一侧表面与第二承载基板300临时键合之后,在所述第一半导体芯片102远离所述第二半导体芯片103的一侧对所述第一半导体芯片102的本体进行减薄处理,以露出所述金属连接柱1022远离所述第二半导体芯片103一侧的表面。

85.如图5d所示,在露出所述金属连接柱1022远离所述第二半导体芯片103一侧的表面之后,在每个所述金属连接柱1022远离所述第二半导体芯片103一侧的表面及其他预设的位置制作第三导电凸点107。

86.如图5e所示,在露出所述金属连接柱1022远离所述第二半导体芯片103一侧的表面之后,将所述第一半导体芯片102与第一承载基板400临时键合。

87.示例性地,例如也可在所述第三导电凸点107制作完成之后,所述第一半导体芯片102远离所述光纤耦合区1024的一侧表面通过每个所述第三导电凸点107与第一承载基板400临时键合。

88.此时,所述第一半导体芯片102和所述第二半导体芯片103夹设在所述第二承载基板300与所述第一承载基板400之间。

89.如图5f所示,在将每个所述第一半导体芯片102与第一承载基板400临时键合之后,将所述第二承载基板300解键合,以露出所述塑封层106。

90.如图5g所示,在露出所述第二半导体芯片103背离所述第一半导体芯片102的一侧表面之后,对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理,以露出所述保护层105背离所述第一半导体芯片102的一侧表面。

91.如图5h所示,在露出所述保护层105背离所述第一半导体芯片102的一侧表面之后,去除覆盖于所述光纤耦合区1024上的所述保护层105,以露出所述光纤耦合区1024。

92.同样地,所述覆盖于所述光纤耦合区1024上的所述保护层105可作为光纤耦合区的保护层和激光烧蚀的停止层,基于所述保护层105覆盖的区域与激光开孔尺寸无法做到完全一致,为了保护第一半导体芯片102上的光耦合接口104不受开孔时激光的损坏,优选地,该保护层105的尺寸设置的比激光开孔的尺寸大。

93.如图5i所示,在露出所述保护层105背离所述第一半导体芯片102的一侧表面之后,在所述保护层105对应所述光纤耦合区1024的位置制作贯穿所述保护层105的开口80以使得所述光纤耦合区1024露出。

94.同样地,可以参考图4所示,在对覆盖于所述光纤耦合区1024上的所述塑封层106进行开孔处理并且去除覆盖于所述光纤耦合区1024上的所述保护层105之后,将所述第一承载基板400解键合。至此,可以得到具有所述第三导电凸点107的封装结构1000。

95.图6是根据本发明实施例提出的封装结构与封装基板连接的示意图。

96.如图6所示,在得到具有所述第三导电凸点107的封装结构1000之后,将至少一个具有所述第三导电凸点107的封装结构1000上的所述第三导电凸点107与封装基板500上的电连接点接合。根据实际需要还可以额外在封装基板上贴装或者集成有电容、电阻、电感等分立器件。

97.图7是根据本发明实施例提出的封装结构与导光结构连接的示意图。

98.如图7所示,在将至少一个具有所述第三导电凸点107的封装结构1000与封装基板500上的电连接点接合后,将导光结构600或者激光器芯片安装至所述光耦合接口104上。

99.示例性地,该导光结构600为光纤阵列(fiber array,fa)。可选的,该导光结构600可以是棱镜,其通过激光整合的方法将激光束引导到光耦合接口104,具体的,激光芯片发出的激光束穿过透镜并入射到棱镜,所述棱镜将所述激光束通过光耦合接口104耦合进入所述第一半导体芯片102。

100.可选的,可以将激光器芯片直接安装在光耦合接口104上方,使激光器芯片发出的激光束对准所述光耦合接口104,所述激光束可以直接耦合到所述第一半导体芯片102。将激光器芯片安装在光耦合接口104上方,可以大大简化器件结构,提高集成度。

101.图8是根据本发明的又一实施例提供的封装结构的部分剖面结构示意图,图9是根据图8中的去除塑封层后的部分俯视结构示意图。

102.如图8和图9所示,在本发明实施例提供的封装结构1000中,包括:第一半导体芯片102、保护层105以及塑封层106,其中,所述第一半导体芯片102包括第一表面102a,在所述第一表面102a的第一区域设置有光纤耦合区1024,所述光纤耦合区1024内设置有光耦合接口104;所述保护层105设置在所述第一表面102a的第一区域,并且在所述光纤耦合区1024设置有贯通所述保护层105的开口80;所述塑封层106位于所述第一表面102a上以及所述保护层105上,所述开口80不被所述塑封层106填充和覆盖。

103.所述保护层105是不透光的非有机材料,所述不透光的非有机材料与所述第一半导体芯片102的基材具有高的刻蚀选择比。例如,所述保护层是不透光的金属层或者无机材料层,所述保护层的厚度在200nm和5μm之间。

104.示例性地,所述保护层105可以为金属膜层,所述覆盖于所述光纤耦合区1024上的所述保护层105可作为光纤耦合区的保护层和激光烧蚀的停止层,既避免有机物在光纤耦合区1024的残留也阻挡了激光入射到第一半导体芯片102损伤光纤耦合区1024,基于所述保护层105覆盖的区域与激光开孔尺寸无法做到完全一致,为了保护第一半导体芯片102上的光耦合接口104不受开孔时激光的损坏,优选地,该保护层105的尺寸设置的比激光开孔的尺寸大。示例性地,在露出所述保护层105背离所述第一半导体芯片102的一侧表面之后,在所述保护层105对应所述光纤耦合区1024的位置制作贯穿所述保护层105的开口80以使得所述光纤耦合区1024露出。

105.示例性地,对所述保护层105进行开口处理后,剩余的保护层105可构成一个封闭的环形。应理解,剩余的保护层105的形状可以根据的开口80的形状而定,本发明实施例在此不做限制。

106.可选地,所述封装结构1000还包括:至少一个第二半导体芯片103,所述至少一个第二半导体芯片固定在所述第一表面的第二区域。应理解,在垂直于所述第一表面102a的方向上,所述第一区域与所述第二区域不交叠。

107.由上述内容可知,本发明实施例提供的封装结构的制作方法及封装结构,由于在光子集成芯片的光纤耦合区上制作覆盖所述光纤耦合区的不透光的保护层,避免有机物材料直接接触光纤耦合区,故在对覆盖于所述光纤耦合区上的所述塑封层进行开孔处理时,保护层能够阻挡高能量的激光进入光纤耦合区,能够保护光耦合接口不被激光损伤,在对覆盖于光纤耦合区上的塑封层进行开孔处理后,可以利用现有的蚀刻技术去除覆盖于光纤耦合区上的保护层,防止光耦合接口不被激光损伤的同时,由于光纤耦合区不接触有机物,还保证了光纤耦合区的表面纯净,有利于后续光耦合接口能够与光纤阵列维持较高的耦合效率。

108.上文仅为本发明的较佳实施例而已,并非用来限定本发明实施的范围,凡依本发明权利要求范围所述的形状、构造、特征及精神所为的均等变化与修饰,均应包括于本发明的权利要求范围内。