1.本发明涉及电子元件卷盘组、电子元件模块和电路。

背景技术:

2.一直以来,电阻器、线圈或电容器等的电子元件,例如在制造后的检查中合格了的产品才会从工厂出售给使用者。在这些检查中,关于电子元件,根据作为基准的电特性值(基准特性值)来挑选出处于规定的允许误差范围(如果是电阻器,例如是自基准电阻值起的不足1%的范围)内的电子元件,并将其作为产品来出售。此时,以包含大量电子元件的电子元件卷盘的状态来出售。电子元件卷盘包括将大量电子元件呈线状地进行收纳的电子元件包装体;和将该电子元件包装体卷绕的卷盘主体(例如参照专利文献1)。另一方面,在上述检查中成为不合格的电子元件不被使用(例如被废弃),会使产品制造的成品率降低。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2017-171393号公报。

技术实现要素:

6.发明要解决的问题

7.鉴于上述情况,本发明的问题在于有效利用特性值超过了允许误差范围的电子元件,使电子元件制造的成品率提高。

8.用于解决问题的技术手段

9.通过本发明的一个方面提供的电子元件卷盘组包括第一电子元件卷盘和第二电子元件卷盘。所述第一电子元件卷盘包括:分别具有比基准特性值大的规定范围的第一特性值的多个第一电子元件;将所述多个第一电子元件呈线状地进行收纳的第一电子元件包装体;卷绕所述第一电子元件包装体的第一卷盘主体;和显示所述第一特性值的第一显示部。所述第二电子元件卷盘包括:分别具有比所述基准特性值小的规定范围的第二特性值的多个第二电子元件;将所述多个第二电子元件呈线状地进行收纳的第二电子元件包装体;卷绕所述第二电子元件包装体的第二卷盘主体;和显示所述第二特性值的第二显示部。

10.本发明的其他的特征和优点通过参照附图在以下进行的详细说明而能够更加明确。

附图说明

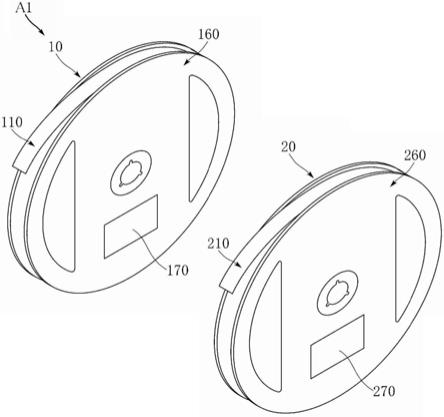

11.图1是表示第一实施方式的电子元件卷盘组的立体图。

12.图2是表示构成电子元件卷盘组的电子元件包装体的部分立体图。

13.图3是图2所示的电子元件包装体的部分平面图。

14.图4是沿着图3的iv-iv线的截面图。

15.图5是表示电子元件的一例的立体图。

16.图6是表示第二实施方式的电子元件模块的立体图。

17.图7是图6所示的电子元件模块的平面图。

18.图8是沿着图7的viii-viii线的截面图。

19.图9是沿着图7的ix-ix线的截面图。

20.图10是表示第三实施方式的电子元件模块的截面图。

21.图11是表示第四实施方式的电路的概略结构的模块图。

22.图12是表示电流检测用电阻的结构例的图。

23.图13是表示第五实施方式的电路的概略结构的模块图。

24.图14是表示第一和第二分压用电阻的结构例的图。

具体实施方式

25.以下,基于本发明的优选的实施方式,参照附图进行具体的说明。

26.本发明中的“第一”、“第二”等的用语仅作为标签使用,不一定是意图对这些对象物赋予顺序。

27.基于图1~图5,对第一实施方式的电子元件卷盘组a1进行说明。图示的电子元件卷盘组a1包括第一电子元件卷盘10和第二电子元件卷盘20。第一电子元件卷盘10包括第一电子元件包装体110和第一卷盘主体160。第二电子元件卷盘20包括第二电子元件包装体210和第二卷盘主体260。

28.第一电子元件卷盘10和第二电子元件卷盘20中,第一电子元件150与第二电子元件250不同,其他的结构实质上是相同的。以下,主要对于第一电子元件卷盘10参照附图进行说明,对于第二电子元件卷盘20适当地省略说明。

29.如图2~图4所示,第一电子元件包装体110包括载带120、覆盖带130、接合部140和多个第一电子元件150。图2是表示从载带120将覆盖带130的一部分剥离的状态。图3是没有剥离覆盖带130的状态的第一电子元件包装体110的部分平面图。图4是沿着图3的iv-iv线的截面图。

30.载带120例如由不透明的聚对苯二甲酸乙二醇酯(pet)树脂或者聚苯乙烯(ps)树脂形成,是在长边方向上延伸的带状。图示的载带120例如由通过压花加工形成有多个收纳凹部122的树脂片构成。举例载带120的尺寸的一例,可以是厚度为0.1~1.1mm程度,宽度为4~12mm程度。作为载带120的材质,可以代替树脂而例如是纸。作为由纸形成的载带120的一例,能够举例将厚度比较厚的厚纸的一部分的厚度通过使其变薄的加工而形成多个收纳凹部122的结构。多个收纳凹部122沿着载带120的长边方向等间隔地配置,是为了将多个第一电子元件150分别地收纳而设置的。在图示的例子中,多个收纳凹部122配置在载带120的宽度方向中央。各收纳凹部122从载带120的主面121凹陷,在图示的例子中,俯视为矩形形状。收纳凹部122的俯视形状也可以是矩形形状以外的多边形形状、圆形形状、椭圆形状等,能够采用适合于被收纳的第一电子元件150的各种形状。

31.覆盖带130是形成为与载带120同程度的宽度的带状。覆盖带130例如形成为基材层与接合层层叠的结构。基材层例如由透明或者半透明的聚对苯二甲酸乙二醇酯(pet)树脂形成。接合层是通过施加热和压力而能够发挥接合功能的层,例如由聚乙烯(pe)类树脂构成。覆盖带130通过接合于载带120的主面121,而将多个收纳凹部122覆盖。由此,第一电

子元件150在收纳凹部122内以从外部被完全封闭的方式被收纳。为了允许多个第一电子元件150的取出,覆盖带130能够从载带120剥离。载带120由纸形成的情况下,覆盖带130形成为相对于纸能够适当地接合和剥离。

32.接合部140是载带120与覆盖带130直接接合的部分。在图示的例子中,接合部140是通过热压接而发挥覆盖带130的上述接合层的接合功能而形成的部位,由2个线状部构成。2个线状部夹着多个收纳凹部122在载带120的宽度方向上隔开间隔地配置,各自沿着载带120的长边方向连续地延伸。

33.多个第一电子元件150例如是芯片电阻器或芯片电感器(线圈)、电容器之类的比较小型的电子元件,本发明并不限定于此。在图示的例子中,第一电子元件150是俯视为长矩形的芯片状无源元件。第一电子元件150具有规定的电特性值。多个第一电子元件150分别收纳在多个收纳凹部122中,在第一电子元件包装体110中呈线状(排状)地进行收纳。在以下的说明中,以第一电子元件150为芯片电阻器的情况进行说明,但本发明并不限定于此。

34.如图5所示,芯片电阻器(第一电子元件)150例如具有基材151、一对电极152、153和绝缘膜154、155。在图示的例子中,芯片电阻器150为厚膜型,基材151是由规定的金属材料形成的电阻体。基材151是厚度一定的长矩形的芯片状。基材151的材质没有特别的限定,例如可以适当地选择具有与芯片电阻器150的目标电阻值相匹配的电阻率的金属材料。或者,可以适当选择适合于将芯片电阻器150形成为所希望的尺寸的材料(例如金属材料)。或者可以考察多个项目(目标电阻值、芯片电阻器的尺寸等)来选择基材151的材料。

35.电极152、153在基材151的长边方向上隔开间隔地设置。这些电极152、153是由与基材151相比焊料的浸润性高的导电性材料形成,例如由cu等的金属形成。例如图5所示,各电极152、153的截面为大致u字状,覆盖基材151的一个端面(基材151的在长边方向上离开的2个端面之中的一方)以及基材151的上表面和下表面。在图示的例子中,各电极152、153覆盖基材151的上述端面的整体。另外,各电极152、153覆盖基材151的上述上表面的一部分和上述下表面的一部分。如图8所示,各电极152、153具有上侧部分(覆盖基材151的上表面的部分)和下侧部分(覆盖基材151的下表面的部分)。在图示的例子中,各电极的上侧部分比下侧部分短(在方向y上的尺寸较小),但本发明并不限定于此。

36.绝缘膜154、155例如是由环氧树脂类的树脂形成的涂装膜。下方的绝缘膜154以覆盖在基材151的下表面之中的电极152、153之间的区域的方式设置。上方的绝缘膜155以覆盖在基材151的上表面之中的电极152、153之间的区域的方式设置。

37.第一电子元件150的大小能够适当地设定。举例非限定的尺寸的一个例子,基材151的长边方向的尺寸为0.4~7.0mm,宽度方向尺寸为0.2~3.5mm,厚度为0.1~2.0mm。

38.多个第一电子元件150分别具有比关于该电子元件的电特性值(基准特性值)大的第一特性值(第一特性值>基准特性值)。作为芯片电阻器的第一电子元件150具有作为第一特性值的第一电阻值。该第一电阻值相对于基准特性值(基准电阻值)具有正误差(第一电阻值-基准电阻值=误差>0)。在本实施方式中,第一电阻值处于规定的范围(后述的“第一误差范围”)中。在芯片电阻器的检查中,其电阻值处于规定的“允许误差范围”(或者“通常误差范围”)内时,将该芯片电阻器作为“通常的产品”挑选。“允许误差范围”是由规定的上限值和下限值规定的区间,是包含基准电阻值的区间。上限值和下限值可能包含在该

区间中,也可能不包含在该区间中。另外,也存在基准电阻值与下限值相等的情况下(在该情况下,下限值包含在该区间中)。例如,设上限值为vmax、下限值为vmin、基准电阻值为rref时,它们与“允许误差范围”的关系能够如下所表示。vmin<允许误差范围<vmax、rref∈允许误差范围。(“∈”是“属于”的意思)。在此2个不等号(<)之中的至少一个也可以是包含等号(≤)。另外,下限值与基准电阻值相等的情况下,该关系能够表示为(vmin=)rref≤允许误差范围<vmax其中,(<也可以是≤)。第一电子元件150是其电阻值超过上述允许误差范围向正侧偏离的元件(即,该电阻值比vmax大,或者是vmax以上)。超过对于通常产品的电阻值的“允许误差范围”,设定对于第一电子元件150的电阻值(“第一电阻值”)的误差范围、即“第一误差范围”。第一误差范围与允许误差范围同样地,能够作为预先设定的下限值(v1min)和上限值(v1max)之间的区间规定。第一电阻值处于第一误差范围内。允许误差范围(对于通常产品的指标)和第一误差范围(对于第一电子元件150的指标)根据电子元件要求的性能适当地设定。

39.上述下限值(v1min)为与基准电阻值(rref)之差的绝对值(|v1min-rref|或者|rref-v1min|)成为最小的值,上述上限值(v1max)为与基准电阻值之差的绝对值(|v1max-rref|或者|rref-v1max|)成为最大的值。关于第一电阻值的下限值和上限值,例如根据与基准电阻值之差的绝对值相对于该基准电阻值成为什么比例来决定。举一个例子,在通常产品的电阻值的允许误差范围(尤其是上限值vmax)自基准电阻值起不足1%的情况下,关于第一电阻值(电子元件150的电阻值)成为自基准电阻值向正侧1~2%的范围(+1~+2%)。换言之,第一电子元件150的电阻值的下限值为基准电阻值

×

1.01,上限值为基准电阻值

×

1.02。

40.第一电子元件包装体110以被卷绕在第一卷盘主体160的状态从制造工厂向使用者的工厂运送,并根据需要来保管。第一电子元件包装体110为在避开多个收纳凹部122的靠宽度方向一端,具有在长边方向上排列的多个定位孔(未图示)的结构。这些定位孔是为了将第一电子元件包装体110以规定速度且仅以规定长度送出而使用的。这与后述的第二电子元件包装体210是同样的。

41.在本实施方式中,在第一卷盘主体160设置有第一显示部170。第一显示部170显示关于第一电子元件150的基准电阻值(基准特性值)和第一特性值(第一电阻值)。第一显示部170的显示方式没有特别的限定,举一个例子,基准电阻值为100ω、电阻值(第一电阻值)的误差范围为自基准电阻值向正侧1~2%的情况下,成为“100ω+1~2ω”或者“基准电阻值100ω电阻值误差范围+1~+2%”等。第一显示部170例如由粘贴在第一卷盘主体160的适当部位的显示标签构成。第一显示部的结构没有特别的限定,可以在第一电子元件包装体110的适当部位(例如覆盖带130)通过印刷显示,也可以在第一卷盘主体160和第一电子元件包装体110的双方设置。

42.第二电子元件包装体210与上述的第一电子元件包装体110是同样的结构,包括载带220、覆盖带230、接合部240和多个第二电子元件250。在图2~图4中,对与载带220、覆盖带230、接合部240、第二电子元件250对应的各要素用括号标注附图标记,而省略具体部分的说明。

43.多个第二电子元件250例如是芯片电阻器、芯片电感器(线圈)、电容器之类的比较小型的电子元件。在本实施方式中,第二电子元件250形成为俯视时长矩形的芯片状,是无

源元件。第二电子元件250具有关于该电子元件的电特性值。多个第二电子元件250分别地收纳在多个收纳凹部222中,在第二电子元件包装体210中呈线状地被收纳。在以下的说明中,主要对于第二电子元件250为芯片电阻器的情况进行说明。

44.如图5所示,作为芯片电阻器的第二电子元件250与上述的第一电子元件150是同样的结构,例如具有基材251、一对电极252、253和绝缘膜254、255。在图5中,对与基材251、电极252、253、绝缘膜254、255对应的各要素标注带括号的附图标记,省略详细部分的说明。

45.多个第二电子元件250分别具有比关于该电子元件成为基准的电特性值(基准特性值)小的第二特性值。在作为芯片电阻器的第二电子元件250中,作为第二特性值具有第二电阻值。该第二电阻值相对于作为基准特性值的基准电阻值具有负侧的误差,在本实施方式中,与基准电阻值之差处于规定的误差范围中。第二电子元件250在芯片电阻器的检查中,其电阻值超过允许误差范围向负侧偏离。通常产品的电阻值的允许误差范围和超过了该范围的第二电子元件250的电阻值的误差范围,根据该电子元件要求的性能能够适当地设定。第二电子元件250的电阻值(第二电阻值)处于例如预先设定的上限值与下限值之间的范围中。该上限值为与基准电阻值之差的绝对值成为最小的值,该下限值为与基准电阻值之差的绝对值成为最大的值。关于第二电阻值的上限值和下限值,例如根据与基准电阻值之差的绝对值相对于该基准电阻值为什么样的比例来决定。举一个例子,例如通常产品的电阻值的允许误差范围自基准电阻值起不足1%的情况下,关于第二电子元件250的第二电阻值,为自基准电阻值向负侧1~2%(-1~-2%)的范围。在该情况下,第二电子元件250的电阻值的上限值为基准电阻值

×

0.99,该电阻值的下限值为基准电阻值

×

0.98。

46.在本实施方式中,例如相对基准电阻值(基准特性值)的第二电阻值(第二特性值)的范围(第二误差范围)与第一误差范围(相对基准电阻值的第一电阻值的范围)是“同等”的。这是指,基准电阻值与第一电子元件150的电阻值的下限值之差(绝对值)和基准电阻值与第二电子元件250的电阻值的上限值之差(绝对值)相等,并且基准电阻值与第一电子元件150的电阻值的上限值之差(绝对值)和基准电阻值与第二电子元件250的电阻值的下限值之差(绝对值)相等。换言之,第一误差范围和第二误差范围关于基准特性值(在本实施方式中基准电阻值)是彼此对称的。或者,第一误差范围和第二误差范围自基准特性值仅以相同程度(向正侧和负侧)偏离,并且各自的长度(误差的宽度)是相同的。

47.第二电子元件包装体210以被卷绕在第二卷盘主体260的状态从制造工厂向使用者的工厂运送,并根据需要被保管。在本实施方式中,在第二卷盘主体260设置有第二显示部270。第二显示部270显示关于第二电子元件250的基准电阻值(基准特性值)和第二特性值(第二电阻值)。第二显示部270的显示方式没有特别的限定,举一个例子,基准电阻值为100ω、电阻值(第二电阻值)的误差范围自基准电阻值向负侧1~2%的情况下,成为“100ω-1~-2ω”或者“基准电阻值100ω电阻值误差范围-1~-2%”等。第二显示部270例如由粘贴在第二卷盘主体260的适当部位的显示标签构成。第二显示部的结构没有特别的限定,可以在第二电子元件包装体210的适当部位(例如覆盖带230)通过印刷来显示,也可以在第二卷盘主体260和第二电子元件包装体210的双方设置。

48.接着,关于电子元件卷盘组a1的作用进行说明。

49.电子元件卷盘组a1具有第一电子元件卷盘10和第二电子元件卷盘20。第一电子元件卷盘10包括多个第一电子元件150,第二电子元件卷盘20包括多个第二电子元件250。使

用者在使用第一电子元件150和第二电子元件250时,例如从第一卷盘主体160将第一电子元件包装体110送出,将收纳在该第一电子元件包装体110中的第一电子元件150取出。同样地,从第二卷盘主体260将第二电子元件包装体210送出,将收纳在该第二电子元件包装体210中的第二电子元件250取出。将所取出的第一电子元件150和第二电子元件250例如安装在电路基板。

50.第一电子元件150和第二电子元件250在电路基板中并联连接。第一电子元件150的电阻值比基准电阻值大,第二电子元件250的电阻值比基准电阻值小。由此,具有正侧误差的第一电子元件150和具有负侧误差的第二电子元件250的合成电阻,与将第一电子元件150或者第二电子元件250以单体使用的情况相比,相对基准电阻值的误差变小,能够成为通常产品水平的误差。像这样,将通过电子元件卷盘组a1供给的第一电子元件150和第二电子元件250相组合地使用,由此能够实现第一电子元件150和第二电子元件250的有效利用,能够使产品制造的成品率提高。

51.在第一电子元件卷盘10(第一卷盘主体160)设置有第一显示部170,在第二电子元件卷盘20(第二卷盘主体260)设置有第二显示部270。依据这样的结构,能够准确地识别在第一和第二电子元件卷盘10、20各自中包含的第一和第二电子元件150、250。

52.在某个使用例中,基准电阻值与第一电阻值之差的绝对值和基准电阻值与第二电阻值之差的绝对值相等、或者实质上相等。依据这样的结构,能够抑制在将第一和第二电子元件150、250相组合地使用时的合成电阻的不一致。

53.例如,相对于基准电阻值rref,使第一电子元件150的电阻值的误差为向正侧1%、使第二电子元件250的电阻值的误差为向负侧1%。在该情况下,第一电子元件150的电阻值r1(1.01rref)与第二电子元件250的电阻值r2(0.99rref)的合成电阻r0通过r0=(r1

×

r2)/(r1+r2)算出,为r0=(1.01rref

×

0.99rref)/(1.01rref+0.99rref)=0.49995rref。因为没有误差的电阻器(基准电阻值rref)的并联连接的合成电阻为0.5rref,在将第一电子元件150与第二电子元件250并联连接的情况下的合成电阻的误差成为向负侧大约0.01%。通过像这样将第一电子元件150和第二电子元件250并联连接,能够大幅度地降低相对基准电阻值的误差。

54.第一和第二电子元件150、250为其他电子元件(例如线圈或者电容器等)的情况下,通过将2个相组合来使用,能够降低相对基准特性值的误差。在第一和第二电子元件150、250分别为线圈的情况下,第一电子元件150具有作为第一特性值的第一电感值,第二电子元件250具有作为第二特性值的第二电感值。第一电感值比作为基准特性值的基准电感值大(具有正侧的误差),第二电感值比基准电感值小(具有负侧的误差)。通过将这样的第一和第二电子元件150、250并联连接,能够有效地降低相对基准电感值(基准特性值)的误差。

55.在第一和第二电子元件150、250为电容器的情况下,第一电子元件150具有作为第一特性值的第一静电电容,第二电子元件250具有作为第二特性值的第二静电电容。第一静电电容比作为基准特性值的基准静电电容大(具有正侧的误差),第二静电电容比基准静电电容小(具有负侧的误差)。通过将这样的第一和第二电子元件150、250串联连接,能够有效地降低相对基准静电电容(基准特性值)的误差。

56.基于图6~图9,对第二实施方式的电子元件模块b1进行说明。图示的电子元件模

块b1包括第一电子元件150、第二电子元件250、一对端子部310、320和密封树脂400。

57.图6是表示电子元件模块b1的立体图。图7是表示电子元件模块b1的平面图。图8是沿着图7的viii-viii线的截面图。图9是沿着图7的ix-ix线的截面图。图6、图7中,透视了密封树脂400来表示(参照表示该密封树脂的外形的两点划线)。

58.电子元件模块b1例如表面安装在电路基板。电子元件模块b1是俯视为矩形的芯片状。将电子元件模块b1的厚度方向作为方向z。另外,将与方向z正交、并且彼此正交的2个方向作为方向x和方向y。在俯视(方向z看)时,方向x相对于电子元件模块b1的一个边平行,方向y相对于电子元件模块b1的另一个边平行。

59.电子元件模块b1的大小没有特别的限定,举一个例子,沿着方向x的尺寸为0.8~10mm,沿着方向y的尺寸为0.8~10mm,沿着方向z的尺寸为0.3~4mm。

60.端子部310、320是用于将电子元件模块b1安装在电路基板等的外部连接用端子,例如由金属板形成。该金属板的构成材料没有特别的限定,例如能够举例cu或cu合金。端子部310、320在方向y上彼此隔开间隔,并且各自为在方向x上延伸的长矩形状。

61.本实施方式的电子元件模块b1中的第一和第二电子元件150、250,因为与上述的电子元件卷盘组a1中的第一和第二电子元件150、250是同样的结构,所以省略详细构造的说明。

62.第一和第二电子元件150、250在方向x上彼此隔开间隔,并且以各自的长边方向沿着方向y的姿态配置。第一电子元件150中的一方的电极152和第二电子元件250中的一方的电极252分别经由导电性接合材料(省略图示)接合于端子部310的上表面。第一电子元件150中的另一方电极153和第二电子元件250中的另一方电极253分别经由导电性接合材料(省略图示)接合于端子部320的上表面。依据这样的结构,第一和第二电子元件150、250并联连接于端子部310、320。

63.密封树脂400如图6~图9所示,将第一和第二电子元件150、250整体地覆盖,并且覆盖各端子部310、320的一部分。密封树脂400的构成材料例如是黑色的环氧树脂。

64.端子部310的侧面的一部分和下表面从密封树脂400露出。另外,端子部320的侧面的一部分和下表面从密封树脂400露出。这些端子部310、320的露出部分经由焊料等的接合材料(省略图示)与电路基板的端子导通接合。

65.接着,关于电子元件模块b1的作用进行说明。

66.电子元件模块b1包括第一和第二电子元件150、250。这些第一和第二电子元件150、250并联连接于端子部310、320,利用密封树脂400形成一体化。依据这样的结构,能够将第一和第二电子元件150、250作为特性值的精度提高了的电子元件模块有效利用。并联连接于端子部310、320的第一和第二电子元件150、250根据关于第一实施方式的电子元件卷盘组a1的说明能够理解,例如是电阻器或者线圈。

67.在电子元件模块b1中,预先组装有第一和第二电子元件150、250,与端子部310、320导通。由此,不会将第一电子元件150与第二电子元件250弄错。因此,能够以将这些第一和第二电子元件150、250组合了的状态适当地向电路基板等搭载。

68.基于图10,关于第三实施方式的电子元件模块b2进行说明。图10是与图8同样的截面图。在电子元件模块b2中,与上述电子元件模块b1相比,主要是第一和第二电子元件150、250的配置和连接不同。

69.在电子元件模块b2中,追加地设置有内部端子330、340、350、连络部360、370和支承基板500。在图10中,对于与上述的电子元件模块b1相同或者类似的要素标注相同的附图标记,省略详细部分的说明。

70.支承基板500经由内部端子330、340、350支承第一和第二电子元件150、250。支承基板500由绝缘材料构成。支承基板500的材质没有特别的限定,例如能够举例环氧树脂或玻璃环氧树脂、陶瓷。支承基板500具有支承面510和底面520。支承面510是朝向方向z的平面。底面520是处于与支承面510相反侧的平面。

71.内部端子330、340、350设置在支承基板500的支承面510上,是构成向第一和第二电子元件150、250的导通路径的部位。内部端子330、340、350的材质没有特别的限定,能够举例cu、ni、ti、au等的金属。另外,内部端子330、340、350的形成方法没有特别限定,在图示的例子中,例如通过镀覆形成。

72.内部端子330、340、350在方向y上彼此隔开间隔地设置。在内部端子330经由接合材料(省略图示)导通地接合有第一电子元件150的一方的电极152。在内部端子340经由接合材(省略图示)分别导通地接合有第一电子元件150的另一方电极153和第二电子元件250的一方的电极252。在内部端子350经由接合材料(省略图示)导通地接合有第二电子元件250的另一方的电极253。

73.端子部310、320设置在支承基板500的底面520上。端子部310、320的材质没有特别的限定,能够举例cu、ni、ti、au等的金属。端子部310、320的形成方法没有特别的限定,在图示的例子中,例如通过镀覆形成。

74.连络部360使内部端子330与端子部310导通。连络部370使内部端子350与端子部320导通。连络部360、370的具体的结构没有特别的限定,在本实施方式中,在方向z看的支承基板500的内方区域中,将支承基板500在厚度方向上贯通。这样的连络部360、370通过在形成于支承基板500的贯通孔中填充金属而设置,到达支承面510和底面520。也可以与图示的例子不同,将连络部360、370通过在形成于支承基板500的贯通孔的内面形成由金属构成的镀层而设置,在该情况下,连络部360、370的内部被填充树脂。

75.密封树脂400配置在支承基板500的支承面510上,覆盖支承面510和第一以及第二电子元件150、250。

76.在电子元件模块b2中,通过上述的结构,第一和第二电子元件150、250串联连接于端子部310、320。

77.电子元件模块b2包括第一和第二电子元件150、250。这些第一和第二电子元件150、250串联连接于端子部310、320,利用密封树脂400形成一体化。依据这样的结构,能够将第一和第二电子元件150、250作为特性值的精度提高了的电子元件模块有效利用。串联连接于端子部310、320的第一和第二电子元件150、250,根据关于第一实施方式的电子元件卷盘组a1的说明能够理解,例如是电容器。

78.在电子元件模块b2中,预先组装有第一和第二电子元件150、250,与端子部310、320导通。由此,不会将第一电子元件150和第二电子元件250弄错。因此,在组合了这些第一和第二电子元件150、250的状态下,能够向电路基板等准确地进行搭载。

79.基于图11、图12,对第四实施方式的电路c1进行说明。图11是将作为电阻器的第一电子元件150和第二电子元件250组合使用的电路c1的概略结构的模块图。图11所示的电路

c1包括输入端子601、整流部602、变压部604、输出端子609、开关元件610、电流检测用电阻620、比较器630和控制部640,是适用于ac/dc转换器的例子。

80.输入端子601从电源部(省略图示)接收交流电压。整流部602是将交流电压进行全波整流的二极管桥式整流器,与输入端子601连接。整流部602的输出电压通过电容器603被平滑化,转变为直流电压。变压部604是具有一次线圈605和二次线圈606的变压器。

81.开关元件(功能部)610与变压部604的一次线圈605连接。开关元件610例如是场效应晶体管(n沟道mosfet)。

82.输出端子609与变压部604的二次线圈606连接。控制部640使开关元件610的导通关断切换驱动。通过切换开关元件610,一次线圈605侧的直流电压被降压,向连接于输出端子609的负载(省略图示)供给稳定为目标值的输出电压。在变压部604的输出侧设置有整流二极管607和输出用的电容器608。

83.电流检测用电阻(电阻部)620与开关元件610连接,连接于开关元件610与接地之间。当开关元件610为导通状态时,在电流检测用电阻620中流通向变压部604的一次线圈605流通的电流ids。因此,在电流检测用电阻620产生与电流ids成比例的检测电压vds。电流检测用电阻620的电阻值例如为数十mω~数百ω程度。因此,即使在电流检测用电阻620中流通的电流ids为数a~十数a,检测电压vds也被抑制得较低。

84.比较器630将电流检测用电阻620的电压(检测电压vds)与基准电压vref进行比较,输出比较结果。在检测电压vds比基准电压vref大的情况下,通过来自比较器630的输出信号使开关元件610成为关断状态。像这样,电流检测用电阻620起到防止对一次线圈605的过电流的功能。电流检测用电阻620和比较器630是对开关元件610起作用的功能部。

85.如图12所示,电流检测用电阻620包括与上述的结构同样的第一电子元件150和第二电子元件250(芯片电阻器)。第一电子元件150具有比基准电阻值大的电阻值(第一电阻值)。第二电子元件250具有比基准电阻值小的电阻值(第二电阻值)。这些第一和第二电子元件150、250被并联连接。

86.电流检测用电阻620是第一和第二电子元件150、250并联连接而成的结构。由此,电流检测用电阻620的电阻值(第一和第二电子元件150、250的合成电阻)近似于基准电阻值,能够实现高精度的电阻器。因此,在具有电流检测用电阻620的电路c1中,能够与目标值更近似地供给稳定化的输出电压。

87.基于图13、图14,对第五实施方式的电路c2进行说明。图13是表示将作为电阻器的第一电子元件150和第二电子元件250相组合来使用的电路c2的概略结构的模块图。在图13所示的电路c2具有输入端子701、控制部710、输出端子702、线圈720、电容器730、第一分压用电阻740和第二分压用电阻750,是适用于dc/dc转换器的例子。

88.输入端子701接受直流电压。控制部(功能部)710与输入端子701连接,使来自输入端子701的直流电压降压,将稳定化为目标值的输出电压供给到输出端子702。线圈720和电容器730构成低通滤波器,来自控制部710的输出电压通过线圈720和电容器730被平均化。

89.来自控制部710的输出电压由第一和第二分压用电阻740、750分压。分压了的电压反馈到控制部710,以使其与内部的基准电压一致的方式调节开关的驱动脉冲的占空比。其结果是,输出电压被稳定化为目标电压。

90.如图14所示,第一分压用电阻740和第二分压用电阻750分别包括与上述的结构同

样的第一电子元件150和第二电子元件250(芯片电阻器)。各第一电子元件150具有比基准电阻值大的电阻值(第一电阻值)。各第二电子元件250具有比基准电阻值小的电阻值(第二电阻值)。在第一和第二分压用电阻740、750各自中并联连接第一和第二电子元件150、250。

91.在本实施方式中,第一和第二分压用电阻740、750分别为并联连接有第一和第二电子元件150、250的结构。由此,第一和第二分压用电阻740、750各自的电阻值(第一和第二电子元件150、250的合成电阻)近似于基准电阻值,能够实现高精度的电阻器。因此,在具有第一和第二分压用电阻740、750(并联连接的第一和第二电子元件150、250)的电路c2中,能够与目标值更近似地供给稳定化的输出电压。

92.以上,对本发明的实施方式进行了说明,但本发明并不限定于此,在不脱离思想的范围内能够进行各种变更。

93.本发明包括以下的附记所记载的结构。

94.附记1.

95.一种电子元件卷盘组,其包括:

96.第一电子元件卷盘;和

97.第二电子元件卷盘,

98.所述第一电子元件卷盘包括:分别具有比基准特性值大的规定范围的第一特性值的多个第一电子元件;将所述多个第一电子元件呈线状地进行收纳的第一电子元件包装体;卷绕所述第一电子元件包装体的第一卷盘主体;和显示所述第一特性值的第一显示部,

99.所述第二电子元件卷盘包括:分别具有比所述基准特性值小的规定范围的第二特性值的多个第二电子元件;将所述多个第二电子元件呈线状地进行收纳的第二电子元件包装体;卷绕所述第二电子元件包装体的第二卷盘主体;和显示所述第二特性值的第二显示部。

100.附记2.

101.在附记1记载的电子元件卷盘组中,

102.所述第一显示部和所述第二显示部显示所述基准特性值。

103.附记3.

104.在附记1或2记载的电子元件卷盘组中,

105.所述第一电子元件和所述第二电子元件为电阻器,所述基准特性值为基准电阻值,

106.所述第一电子元件具有比所述基准电阻值大的第一电阻值作为所述第一特性值,

107.所述第二电子元件具有比所述基准电阻值小的第二电阻值作为所述第二特性值。

108.附记4.

109.在附记1或2记载的电子元件卷盘组中,

110.所述第一电子元件和所述第二电子元件为线圈,所述基准特性值为基准电感值,

111.所述第一电子元件具有比所述基准电感值大的第一电感值作为所述第一特性值,

112.所述第二电子元件具有比所述基准电感值小的第二电感值作为所述第二特性值。

113.附记5.

114.在附记1或2记载的电子元件卷盘组中,

115.所述第一电子元件和所述第二电子元件为电容器,所述基准特性值为基准静电电

容,

116.所述第一电子元件具有比所述基准静电电容大的第一静电电容作为所述第一特性值,

117.所述第二电子元件具有比所述基准静电电容小的第二静电电容作为所述第二特性值。

118.附记6.

119.在附记1~5中任一项记载的电子元件卷盘组中,

120.与所述基准特性值和所述第一特性值之差对应的第一误差范围和与所述基准特性值和所述第二特性值之差对应的第二误差范围是同等的。

121.附记7.

122.一种电子元件模块,其包括:

123.第一电子元件,其具有比基准特性值大的规定范围的第一特性值;

124.第二电子元件,其具有比所述基准特性值小的规定范围的第二特性值;

125.与所述第一电子元件和所述第二电子元件导通的外部连接用的端子部;和

126.覆盖所述第一电子元件和所述第二电子元件的密封树脂。

127.附记8.

128.在附记7记载的电子元件模块中,

129.所述第一电子元件和所述第二电子元件并联连接于所述端子部。

130.附记9.

131.在附记7或8记载的电子元件模块中,

132.所述第一电子元件和所述第二电子元件为电阻器。

133.附记10.

134.在附记7或8记载的电子元件模块中,

135.所述第一电子元件和所述第二电子元件为线圈。

136.附记11.

137.在附记7记载的电子元件模块中,

138.所述第一电子元件和所述第二电子元件串联连接于所述端子部。

139.附记12.

140.在附记11记载的电子元件模块中,

141.所述第一电子元件和所述第二电子元件为电容器。

142.附记13.

143.一种电路,其包括:

144.具有规定的功能的功能部;和

145.连接于所述功能部的至少1个电阻部,

146.所述电阻部包括:具有比基准电阻值大的规定范围的第一电阻值的第一电阻器;和具有比所述基准电阻值小的规定范围的第二电阻值的第二电阻器,

147.所述第一电阻器和所述第二电阻器并联连接。

148.附记14.

149.在附记13记载的电路中,还包括:

150.接受交流电压的输入端子;

151.与所述输入端子连接的整流部;

152.变压部,其包括一次线圈和二次线圈,所述一次线圈与所述整流部连接;

153.与所述二次线圈连接的输出端子;和

154.控制部,

155.所述功能部为与所述一次线圈连接的开关元件,所述控制部构成为能够驱动所述开关元件。

156.附记15.

157.在附记13记载的电路中,还包括:

158.接受直流电压的输入端子;和

159.输出端子,

160.所述功能部为与所述输入端子连接的控制部,来自所述控制部的输出电压被供给到所述输出端子,

161.所述电阻部包括第一分压用电阻和第二分压用电阻,构成为能够将来自所述控制部的输出电压进行分压。

162.符号说明

163.a1电子元件卷盘组

164.b1、b2电子元件模块

165.c1、c2电路

166.10第一电子元件卷盘

167.110第一电子元件包装体

168.120载带

169.121主面

170.122收纳凹部

171.130覆盖带

172.140接合部

173.150第一电子元件

174.151基材

175.152、153电极

176.154、155绝缘膜

177.160第一卷盘主体

178.170第一显示部

179.20第二电子元件卷盘

180.210第二电子元件包装体

181.220载带

182.221主面

183.222收纳凹部

184.230覆盖带

185.240接合部

186.250第二电子元件

187.251基材

188.252、253电极

189.254、255绝缘膜

190.260第二卷盘主体

191.270第二显示部

192.310、320端子部

193.330、340、350内部端子

194.360、370连络部

195.400密封树脂

196.500支承基板

197.510支承面

198.520底面

199.601输入端子

200.602整流部

201.603电容器

202.604变压部

203.605一次线圈

204.606二次线圈

205.607整流二极管

206.608电容器

207.609输出端子

208.610开关元件

209.620电流检测用电阻

210.630比较器

211.640控制部

212.701输入端子

213.702输出端子

214.710控制部

215.720线圈

216.730电容器

217.740第一分压用电阻

218.750第二分压用电阻

219.x方向

220.y方向

221.z方向。