goa电路及显示面板

技术领域

1.本发明涉及显示技术领域,尤其涉及一种goa电路及显示面板。

背景技术:

2.有源矩阵有机发光二极管(active-matrix organic light-emitting diode,amoled)显示装置由于具有对比度高、反应速度快和广视角的优点,已被广泛应用。amoled属于电流驱动型器件,其对像素电路的驱动晶体管的电性变异比较敏感,驱动晶体管的阈值电压的漂移会影响其显示效果,因此需要对驱动晶体管进行阈值电压补偿。

3.图1为现有技术的像素补偿电路的电路图和时序图,其中,第一晶体管t1为驱动晶体管,t1的栅极连接节点a,t1的源极连接电源正电压vdd,t1的漏极连接节点b;第二晶体管t2为数据写入晶体管,t2的栅极接入写入信号wr,t2的源极接入数据信号data,t2的漏极连接节点a;第三晶体管t3为读取晶体管,t3的栅极接入读取信号rd,t3的源极连接有机发光二极管的阳极,t3的漏极接入感测信号线sense;存储电容cst连接在节点a和节点b之间,有机发光二极管的阳极连接节点b,阴极连接电源负电压vss;存储电容cbt的一端连接节点a,一端连接节点b。

4.这样,在每帧的有效显示时间(也称为编程时间,program时间),通过向像素补偿电路输入写入信号wr和读取信号rd扫描对应的一行像素(此时感测线sense输入初始化电位),利用数据信号data使该行像素被点亮,然后在每帧的非有效显示时间(blank时间),通过向像素补偿电路输入写入信号wr和读取信号rd,用感测线sense侦测t1的源极电位,最后根据t1的栅源极电位差侦测到t1的阈值电压,进而通过改变数据信号data来对阈值电压进行外部补偿,从而使有机发光二极管的发光电流能保持稳定,不受t1的阈值电压的影响。

5.而阵列基板栅极驱动(gate driveron array,goa)技术是将栅极驱动电路集成在显示面板的阵列基板上以实现逐行扫描的驱动方式,从而可以省掉面板的栅极驱动电路部分,具有降低面板的生产成本和实现面板窄边框设计的优点,为多种显示器所使用,因此,为了对像素进行外部补偿,amoled显示装置的goa电路需要为图1中的像素外部补偿电路提供稳定的写入信号wr和读取信号rd。

6.然而,随着显示面板的分辨率和刷新率的不断提升,goa电路存在以下两个问题:1)、根据goa电路的动态消耗公式:p=fcv2,可知时钟信号(ck信号)的刷新频率越高,goa电路的动态消耗则越大;2)、需要用于控制写入信号wr和读取信号rd的时钟信号更多,因此时钟线的数量越多,这不利于实现显示面板的窄边框。

技术实现要素:

7.为了解决上述问题,本发明实施例提供一种goa电路及显示面板。

8.第一方面,本发明实施例提供一种goa电路,包括多级级联的goa单元,第n级所述goa单元包括上拉控制单元和上拉单元;

9.所述上拉控制单元连接第n-3级级传信号端、第一时钟信号端和第一节点,用于在

所述第一时钟信号端的控制下,通过所述第n-3级级传信号端提高所述第一节点的电位;

10.所述上拉单元连接所述第一节点、第二时钟信号端、第一低频时钟信号端和第二低频时钟信号端,用于在所述第一节点的控制下,通过所述第二时钟信号控制第n级级传信号端,通过所述第一低频时钟信号端控制第n级写入信号端,以及通过所述第二低频时钟信号端控制所述第n级读取信号端。

11.在一些实施例中,所述上拉控制单元包括第十一晶体管和第十二晶体管;所述第十一晶体管的栅极和所述第十二晶体管的栅极与所述第一时钟信号端连接,所述第十一晶体管的漏极和所述第十二晶体管的源极连接第三节点,所述第十一晶体管的源极连接所述第n-3级级传信号端,所述第十二晶体管的漏极连接所述第一节点。

12.在一些实施例中,所述上拉单元包括第二十一晶体管、第二十二晶体管、第二十三晶体管和第一自举电容;所述第二十一晶体管的栅极、所述第二十二晶体管和所述第二十三晶体管的栅极连接所述第一节点,所述第二十一晶体管的源极连接所述第二时钟信号端,所述第二十一晶体管的漏极连接第n级级传信号端,所述第二十二晶体管的源极连接所述第一低频时钟信号端,所述第二十二晶体管的漏极连接所述第n级写入信号端,所述第二十三晶体管的源极连接所述第二低频时钟信号端,所述第二十三晶体管的漏极连接所述第n级读取信号;所述第一自举电容的第一端连接所述第一节点,所述第一自举电容的第二端连接所述第n级级传信号端。

13.在一些实施例中,第n级所述goa单元还包括逻辑寻址侦测单元,所述逻辑寻址侦测单元包括第七十一晶体管、第七十二晶体管、第七十三晶体管、第七十四晶体管、第七十五晶体管和第二自举电容;所述第七十一晶体管的栅极连接重置信号端,所述第七十一晶体管的源极和所述第七十二晶体管的漏极连接,所述第七十一晶体管的漏极连接所述第一节点;所述第七十二晶体管的栅极、所述第七十五晶体管的栅极和所述第二自举电容的第一端互相连接,所述第七十二晶体管的源极、所述第七十五晶体管的源极和所述第二自举电容的第二端连接恒压高电位端;所述第七十五晶体管的漏极、所述第七十四晶体管的漏极、所述第七十三晶体管的源极互相连接,所述第七十四晶体管的源极连接所述第n-3级级传信号,所述第七十三晶体管的栅极和所述第七十四晶体管的栅极连接第一控制信号端,所述第七十三晶体管的漏极连接第四节点。

14.在一些实施例中,第n级所述goa单元还包括第一下拉单元,所述第一下拉单元包括第三十三晶体管和第三十四晶体管;所述第三十三晶体管的栅极和所述第三十四晶体管的栅极连接第二控制信号端,所述第三十四晶体管的源极连接所述第一节点,所述第三十四晶体管的漏极和所述第三十三晶体管的源极连接第三节点,所述第三十三晶体管的漏极连接第一恒压低电位端。

15.在一些实施例中,第n级所述goa单元还包括第一下拉维持单元,所述第一下拉维持单元包括第四十四晶体管和第四十五晶体管;所述第四十四晶体管的栅极和所述第四十五晶体管的栅极连接第二节点,所述第四十四晶体管的漏极和所述第四十五晶体管的源极连接第三节点,所述第四十四晶体管的源极连接所述第一节点,所述第四十五晶体管的漏极连接第一恒压低电位端。

16.在一些实施例中,第n级所述goa单元还包括反相器单元,所述反相器单元包括第五十一晶体管、第五十二晶体管、第五十三晶体管和第五十四晶体管;所述第五十一晶体管

的栅极和源极、以及所述第五十三晶体管的源极连接恒压高电位端,所述第五十一晶体管的漏极、所述第五十二晶体管的源极和所述第五十三晶体管的栅极互相连接,所述第五十二晶体管的漏极和所述第五十四晶体管的漏极连接第一恒压低电位端,所述第五十二晶体管的栅极和所述第五十四晶体管的栅极连接所述第一节点,所述第五十三晶体管的漏极和所述第五十四晶体管的源极连接第二节点。

17.在一些实施例中,第n级所述goa单元还包括第二下拉单元,所述第二下拉单元包括第三十一晶体管和第三十二晶体管;所述第三十一晶体管的栅极和所述第三十二晶体管的栅极连接第n+1级级传信号端,所述第三十二晶体管的源极连接所述第一节点,所述第三十二晶体管的漏极和所述第三十一晶体管的源极连接第三节点,所述第三十一晶体管的漏极连接第一恒压低电位端。

18.在一些实施例中,第n级所述goa单元还包括第三下拉单元,所述第三下拉单元包括第三十五晶体管和第三十六晶体管;所述第三十六晶体管的栅极连接重置信号端,所述第三十五晶体管的栅极连接第四节点,所述第三十六晶体管的源极连接第二节点,所述第三十六晶体管的漏极和所述第三十五晶体管的源极连接,所述第三十五晶体管的漏极连接第一恒压低电位端。

19.在一些实施例中,第n级所述goa单元还包括第四下拉单元,所述第四下拉单元包括第三十七晶体管和第三十八晶体管;所述第三十八晶体管的栅极和所述第三十七晶体管的栅极连接第n+1级级传信号端,所述第三十八晶体管的源极连接所述第n级写入信号,所述第三十八晶体管的漏极和所述第三十七晶体管的漏极连接第二恒压低电位端,所述第三十七晶体管的源极连接所述第n级写入信号端。

20.在一些实施例中,第n级所述goa单元还包括所述第二下拉维持单元,所述第二下拉维持单元包括第四十一晶体管、第四十二晶体管和第四十三晶体管;所述第四十一晶体管的栅极、所述第四十二晶体管的栅极和所述第四十三晶体管的栅极连接第二节点,所述第四十一晶体管的源极连接所述第n级级传信号端,所述第四十二晶体管的源极连接所述第n级写入信号端,所述第四十三晶体管的源极连接所述第n级写入读取信号端,所述第四十一晶体管的漏极、所述第四十二晶体管的漏极和所述第四十三晶体管的的漏极连接第二恒压低电位端。

21.第二方面,本发明实施例还提供一种显示面板,包括如上所述的goa电路。

22.本发明实施例提供的goa电路及显示面板,通过第一低频时钟信号和第二低频时钟信号替代多个高频时钟信号用于分别控制写入信号和读取信号,且第一低频时钟信号和第二低频时钟信号在显示面板的有效显示时间内为直流信号,从而大大减少了显示面板的动态功耗,同时,由于利用仅两条低频时钟信号线替代了多条高频时钟信号线,从而减少了时钟信号线的数量,减少了goa电路的占用面积,有利于显示面板实现窄边框设计。

附图说明

23.下面结合附图,通过对本发明的具体实施方式详细描述,将使本发明的技术方案及其它有益效果显而易见。

24.图1为现有技术的一种像素补偿电路的电路图;

25.图2为现有技术的一种goa电路的电路图;

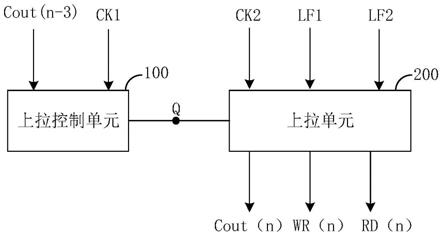

26.图3为现有技术的goa电路的一组时钟信号线的波形图;

27.图4为本发明实施例提供的goa电路的电路图;

28.图5为本发明实施例提供的goa电路的另一种电路图;

29.图6为本发明实施例提供的goa电路的时序图。

具体实施方式

30.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

31.现有的goa电路一般需要多组高频时钟信号进行驱动,例如,图2为现有技术的一种goa电路的电路图,该goa电路采用四组高频时钟信号:ck1(cka1~cka4),ck2(ckb1~ckb4),ck3(ck~ckc4),ck4(ckd1~ckd4),即,总共至少需要16根时钟线,图3所示为其中任意一组时钟线cka1~cka4的波形图,图4为现有goa电路的电路图,级联的每级goa单元接收每组高频时钟信号中的一个高频时钟信号,即,每条时钟线输入的时钟信号都会根据需要输出的级传信号或栅极驱动信号周期变化,这样随着显示面板尺寸和频率的增加,不仅会由于时钟线频率的增加使得goa电路的动态损耗较高,同时也会由于需要更多组时钟线,使goa电路的占用面积的较大,不利于显示面板实现窄边框。

32.有鉴于此,如图4所示,本发明实施例提供一种goa电路,包括多级级联的goa单元,第n级goa单元包括上拉控制单元100和上拉单元200。

33.上拉控制单元100连接第n-3级级传信号端cout(n-3)、第一时钟信号端ck1和第一节点q,用于在第一时钟信号端ck1的控制下,通过第n-3级级传信号端cout(n-3)提高第一节点q的电位;

34.上拉单元200连接第一节点q、第二时钟信号端ck2、第一低频时钟信号端lf1和第二低频时钟信号端lf2,用于在第一节点q的控制下,通过第二时钟信号ck2控制第n级级传信号端cout(n),通过第一低频时钟信号端lf1控制第n级写入信号端wr(n),以及通过第二低频时钟信号端lf2控制第n级读取信号端rd(n)。

35.也就是说,相比于图2所示的goa电路,本发明实施例提供的goa电路通过第一低频时钟信号lf1替代用于输出写入信号的多个时钟信号,以及通过第二低频时钟信号lf2替代用于输出读取信号的多个时钟信号,并且使第一低频时钟lf1和第二低频时钟信号lf2在显示面板的有效显示时间内为直流信号,从而减少时钟信号在有效显示时间内的刷新频率,同时减少时钟信号线的数量。

36.本发明实施例提供的goa电路,通过第一低频时钟信号lf1和第二低频时钟信号lf2替代多个高频时钟信号用于分别控制写入信号wr和读取信号rd,且第一低频时钟信号lf1和第二低频时钟信号lf2在显示面板的有效显示时间内为直流信号,从而大大减少了显示面板的动态功耗,同时,由于利用仅两条低频时钟信号线替代了多条高频时钟信号线,从而减少了时钟信号线的数量,减少了goa电路的占用面积,有利于显示面板实现窄边框设计。

37.进一步地,图5为本发明实施例提供的goa电路的具体电路图,需要说明的是,为了

方便比较,现有技术的goa电路(图2)和本发明实施例提供的goa电路(图5)中的部分晶体管采用相同的标号,本发明实施例提供的goa电路的电路图以图5为准。

38.如图5所示,上拉控制单元100包括第十一晶体管t11和第十二晶体管t12;其中,第十一晶体管t11的栅极和第十二晶体管t12的栅极与第一时钟信号端ck1连接,第十一晶体管t11的漏极和第十二晶体管t12的源极连接第三节点n,第十一晶体管t11的源极连接第n-3级级传信号端cout(n-3),第十二晶体管t12的漏极连接第一节点q。

39.请继续参阅图5,上拉单元200包括第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23和第一自举电容cbt1;其中,第二十一晶体管t21的栅极、第二十二晶体管t22和第二十三晶体管t23的栅极连接第一节点q,第二十一晶体管t21的源极连接第二时钟信号端ck2,第二十一晶体管t21的漏极连接第n级级传信号端cout(n),第二十二晶体管t22的源极连接第一低频时钟信号端lf1,第二十二晶体管t22的漏极连接第n级写入信号端wr(n),第二十三晶体管t23的源极连接第二低频时钟信号端lf2,第二十三晶体管t23的漏极连接第n级读取信号rd(n);第一自举电容cbt1的第一端连接第一节点q,第一自举电容cbt1的第二端连接第n级级传信号cout(n)。

40.请继续参阅图5,第n级goa单元还包括逻辑寻址侦测单元300,逻辑寻址侦测单元300包括第七十一晶体管t71、第七十二晶体管t72、第七十三晶体管t73、第七十四晶体管t74、第七十五晶体管t75和第二自举电容cbt2;其中,第七十一晶体管t71的栅极连接重置信号端reset,第七十一晶体管t71的源极和第七十二晶体管t72的漏极连接,第七十一晶体管t71的漏极连接第一节点q;第七十二晶体管t72的栅极、第七十五晶体管t75的栅极和第二自举电容cbt2的第一端互相连接,第七十二晶体管t72的源极、第七十五晶体管t75的源极和第二自举电容cbt2的第二端连接恒压高电位端vgh;第七十五晶体管t75的漏极、第七十四晶体管t74的漏极、第七十三晶体管t73的源极互相连接,第七十四晶体管t74的源极连接第n-3级级传信号cout(n-3),第七十三晶体管t73的栅极和第七十四晶体管t74的栅极连接第一控制信号端lsp,第七十三晶体管t73的漏极连接第四节点m。

41.请继续参阅图5,第n级所述goa单元还包括第一下拉单元400,第一下拉单元400包括第三十三晶体管t33和第三十四晶体管t34;其中,第三十三晶体管t33的栅极和第三十四晶体管t34的栅极连接第二控制信号端vst,第三十四晶体管t34的源极连接第一节点q,第三十四晶体管t34的漏极和第三十三晶体管t33的源极连接第三节点n,第三十三晶体管t33的漏极连接第一恒压低电位端vgl1。

42.请继续参阅图5,第n级所述goa单元还包括第一下拉维持单元500,第一下拉维持单元500包括第四十四晶体管t44和第四十五晶体管t45;其中,第四十四晶体管t44的栅极和第四十五晶体管t45的栅极连接第二节点p,第四十四晶体管t44的漏极和第四十五晶体管t45的源极连接第三节点n,第四十四晶体管t44的源极连接第一节点q,第四十五晶体管t45的漏极连接第一恒压低电位端vgl1。

43.请继续参阅图5,第n级所述goa单元还包括反相器单元600,反相器单元600包括第五十一晶体管t51、第五十二晶体管t52、第五十三晶体管t53和第五十四晶体管t54;其中,第五十一晶体管t51的栅极和源极、以及第五十三晶体管t53的源极连接恒压高电位端vgh,第五十一晶体管t51的漏极、第五十二晶体管t52的源极和第五十三晶体管t53的栅极互相连接,第五十二晶体管t52的漏极和第五十四晶体管t54的漏极连接第一恒压低电位端

vgl1,第五十二晶体管t52的栅极和第五十四晶体管t54的栅极连接第一节点q,第五十三晶体管t53的漏极和第五十四晶体管t54的源极连接第二节点p。

44.请继续参阅图5,第n级所述goa单元还包括第二下拉单元700,第二下拉单元700包括第三十一晶体管t31和第三十二晶体管t32;第三十一晶体管t31的栅极和第三十二晶体管t32的栅极连接第n+1级级传信号cout(n+1),第三十二晶体管t32的源极连接第一节点q,第三十二晶体管t32的漏极和第三十一晶体管t31的源极连接第三节点n,第三十一晶体管t31的漏极连接第一恒压低电位端vgl1。

45.请继续参阅图5,第n级所述goa单元还包括第三下拉单元800,第三下拉单元800包括第三十五晶体管t35和第三十六晶体管t36;其中,第三十六晶体管t36的栅极连接重置信号端reset,第三十五晶体管t35的栅极连接第四节点m,第三十六晶体管t36的源极连接第二节点p,第三十六晶体管t36的漏极和第三十五晶体管t35的源极连接,第三十五晶体管t35的漏极连接第一恒压低电位端vgl1。

46.请继续参阅图5,第n级所述goa单元还包括第四下拉单元900,第四下拉单元900包括第三十七晶体管t37和第三十八晶体管t38;其中,第三十八晶体管t38的栅极和第三十七晶体管t37的栅极连接第n+1级级传信号cout(n+1),第三十八晶体管t38的源极连接第n级写入信号端wr(n),第三十八晶体管t38的漏极和第三十七晶体管t37的漏极连接第二恒压低电位端vgl2,第三十七晶体管t37的源极连接第n级写入信号端wr(n)。

47.请继续参阅图5,第n级所述goa单元还包括第二下拉维持单元1000,第二下拉维持单元1000包括第四十一晶体管t41、第四十二晶体管t42和第四十三晶体管t43;其中,第四十一晶体管t41的栅极、第四十二晶体管t42的栅极和第四十三晶体管t43的栅极连接第二节点p,第四十一晶体管t41的源极连接第n级级传信号端cout(n),第四十二晶体管t42的源极连接第n级写入信号端wr(n),第四十三晶体管t43的源极连接第n级写入读取信号端rd(n),第四十一晶体管t41的漏极、第四十二晶体管t42的漏极和第四十三晶体管t43的的漏极连接第二恒压低电位端vgl2。

48.基于上述实施例,结合图5和图6所示,本发明实施例提供的goa电路在每帧图像的显示时间(program时间)内的工作流程为:

49.在a1阶段,第n-3级级传信号cout(n-3)和第一时钟信号ck1为高电位,使得第十一晶体管t11和第十二晶体管t12打开,第一节点q的电位被拉升至高电位,使得第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23、第五十二晶体管t52和第五十四晶体管t54均打开。由于第一节点q与第二节点p之间连接反相器单元600(由第五十一晶体管t51、第五十二晶体管t52、第五十三晶体管t53和第五十四晶体管t54组成),使得第一节点q的电位与第二节点p的电位反相,因此此时第二节点p的电位为低电位,使得第四十一晶体管t41、第四十二晶体管t42、第四十三晶体管t43、第四十四晶体管t44和第四十五晶体管t45均关闭。

50.同时,第n+1级级传信号cout(n+1)为低电位,使第三十一晶体管t31、第三十二晶体管t32、第三十七晶体管t37、第三十八晶体管t38关闭;第二时钟信号ck2为低电位,使得第n级级传信号cout(n)为低电位;第一低频时钟信号lf1和第二低频时钟信号lf2为高电位,使得第n级写入信号wr(n)和第n级读取信号rd(n)为高电位;第一控制信号lsp为高电位,使第四节点m的电位被拉升至高电位,从而使得第七十二晶体管t72和第七十五晶体管

t75打开。

51.在a2阶段,第n-3级级传信号cout(n-3)和第一控制信号lsp降为低电位,使得第七十三晶体管t73和第七十四晶体管t74关闭,此时第四节点m仍为高电位,使第七十二晶体管t72和第七十五晶体管t75打开,由恒压高电位vgh使第七十三晶体管t73的源极为高电位,从而使第七十三晶体管t73的栅源极电位差vgs为负值,使得第七十三晶体管t73的漏电流极小,因此能使得第四节点m点维持高电位。此时;第一节点q保持高电位,使第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23打开,第二时钟信号ck2为低电位,使第n级级传信号cout(n)为低电位,第一低频时钟信号lf1和第二低频时钟信号lf2为高电位,使第n级写入信号wr(n)和第n级读取信号rd(n)为高电位。

52.在a3阶段,第二时钟信号ck2为高电位,使得第n级级传信号cout(n)为高电位,由于第一自举电容cbt1的存在,第一节点q被耦合至更高的电位,从而有利于维持第n级写入信号wd(n)和第n级读取信号rd(n)的高电位。

53.在a4阶段,第n+1级级传信号cout(n+1)为高电位,使第三十一晶体管t31、第三十二晶体管t32、第三十七晶体管t37、第三十八晶体管t38打开,从而使第一节点q被拉低为低电位,此时由反相器单元600将第二节点p拉升至高电位,使得第四十一晶体管t41、第四十二晶体管t42、第四十三晶体管t43、第四十四晶体管t44和第四十五晶体管t45打开,从而使第一节点q、第n级级传信号cout(n)、第n级写入信号wr(n)和第n级读取信号rd(n)为低电位。

54.进一步地,本发明实施例提供的goa电路在每帧图像的非有效显示时间(blank时间)内的工作流程为:

55.在b1阶段:在上述有效显示时间时,第二自举电容cbt2使第四节点m点保持高电位,此时重置信号reset为高电位,使第七十一晶体管t71打开,第一节点q的电位被拉升为高电位,使得第二十一晶体管t21、第二十二晶体管t22、第二十三晶体管t23、第五十二晶体管t52和第五十四晶体管t54均打开;此时反相器单元600使第二节点p为低电位,使得第四十一晶体管t41、第四十二晶体管t42、第四十三晶体管t43、第四十四晶体管t44和第四十五晶体管t45关闭。

56.同时,第n+1级级传信号cout(n+1)为低电位,使第三十一晶体管t31、第三十二晶体管t32、第三十七晶体管t37、第三十八晶体管t38关闭;第二控制信号为低电位,使第三十三晶体管t33和第三十四晶体管t34关闭;第二时钟信号ck2为低电位,使第n级级传信号cout(n)为低电位,第一低频时钟信号和第二低频时钟信号为低电位,使得第n级写入信号wr(n)和第n级读取信号rd(n)为低电位。

57.在b2阶段:重置信号reset为低电位,使第七十一晶体管t71关闭;第二时钟信号ck2为低电位,使第n级级传信号cout(n)为低电位;第一低频时钟信号lf1为低电位,使第n级写入信号wr(n)为低电位;第二低频时钟信号lf2为高电位,使第n级读取信号rd(n)为高电位。

58.在b3阶段:第一低频时钟信号lf1和第二低频时钟信号lf2为高电位,使第n级写入信号wr(n)和第n级读取信号rd(n)为高电位。

59.在b4阶段:第一低频时钟信号lf1为低电位,使第n级写入信号wr(n)为低电位;第二低频时钟信号lf2为高电位,使第n级读取信号rd(n)为高电位。

60.在b5阶段:第二控制信号vst为高电位,使得第三十三晶体管t33和第三十四晶体管t34打开,从而使第一节点q被拉低至低电位,此时反相器单元600使第二节点p为高电位,从而使得第四十一晶体管t41、第四十二晶体管t42、第四十三晶体管t43、第四十四晶体管t44和第四十五晶体管t45打开,从而使第一节点q、第n级级传信号cout(n)、第n级写入信号wr(n)和第n级读取信号rd(n)为低电位。

61.本发明实施例提供的goa电路,通过第一低频时钟信号lf1和第二低频时钟信号lf2替代多个高频时钟信号用于分别控制写入信号wr和读取信号rd,且第一低频时钟信号lf1和第二低频时钟信号lf2在显示面板的有效显示时间(program时间)内为直流信号,从而大大减少了显示面板的动态功耗,同时,由于利用仅两条低频时钟信号线替代了多条高频时钟信号线,从而减少了时钟信号线的数量,减少了goa电路的占用面积,有利于显示面板实现窄边框设计。

62.基于上述实施例,本发明实施例还提供一种显示面板,该显示面板包括如上所述的goa电路,该显示面板与上述的goa电路具有相同的结构和有益效果,由于上述各实施例已经对该goa电路进行了详细的描述,此处不再赘述。

63.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

64.以上实施例的说明只是用于帮助理解本发明的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例的技术方案的范围。