1.本发明涉及一种显示技术,特别涉及一种显示装置。

背景技术:

2.在驱动led时面板时,显示装置是依据脉冲宽度调制(pulse-width modulation,pwm)信号进行操作。通过pwm信号进行操作可能导致在显示装置中累积大量电流,驱动装置的电路需要复杂的设计,以及容易导致屏幕闪烁(flicker)等等风险。因此,要如何发展能够克服上述问题的相关技术为本领域重要的课题。

技术实现要素:

3.本发明实施例包含一种显示装置,包括串联耦接的多个像素驱动电路。多个像素驱动电路中的一第一像素驱动电路包括发光元件、第一驱动单元、第二驱动单元及控制单元。发光元件用以依据一电流发光。第一驱动单元用以产生电流。第二驱动单元用以依据一第一扫描信号驱动第一驱动单元以调整电流。控制单元用以依据一第一发光信号控制第一驱动单元以调整电流。第一扫描信号的一电压电平分别在一第一期间、一第二期间及一第三期间具有彼此不同的一第一斜率、一第二斜率及一第三斜率。第一发光信号在第一期间及第三期间具有一致能电压电平,且在第二期间具有一禁能电压电平。第一期间、第二期间及第三期间按序且连续排列。

附图说明

4.图1为根据本公开的一实施例所示出的显示器的示意图。

5.图2为根据本公开的一实施例所示出的显示装置中的像素驱动电路的方框图。

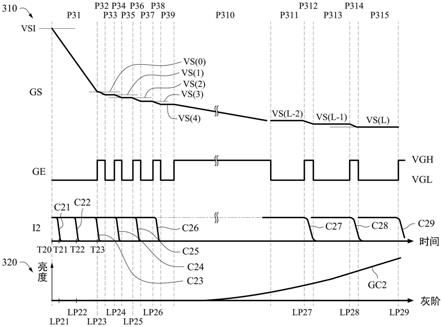

6.图3为根据本发明的一实施例中的像素驱动电路进行发光操作所示出的时序图及对应的灰阶亮度关系图。

7.图4为根据本公开的一实施例所示出的显示装置中的像素驱动电路的方框图。

8.图5为根据本发明的一实施例中的像素驱动电路进行发光操作所示出的时序图。

9.图6为根据本公开的一实施例所示出的显示装置的示意图。

10.图7为根据本发明的一实施例中的像素驱动电路及进行发光操作所示出的时序图。

11.图8为根据本发明的一实施例中的显示装置进行发光操作所示出的时序图。

12.附图标记说明:

13.100:显示器

14.110、600:显示装置

15.120:扫描装置

16.130:数据输入装置

17.140:发光控制装置

18.sl(0)~sl(n):扫描线

19.gs、gs61、gs62、gs(1)~gs(n):扫描信号

20.dl(1)~dl(m):数据线

21.dtw(m)、dta(m):数据信号

22.el(1)~el(n):发光线

23.em、ge、ge61、ge62、ge(1)~ge(n):发光信号

24.pwmd、ampd:驱动信号

25.ppo:夹止信号

26.dv(1)~dv(n)、112、200、400、610、620:像素驱动电路

27.l2、l4:发光元件

28.210、220、410、420:控制单元

29.230、240、430、440:驱动单元

30.ss、dd、rstd:电压信号

31.310、500、700、800:时序图

32.320:灰阶亮度关系图

33.c21~c29、gc2:曲线

34.t20~t23:时刻

35.lp21~lp29:灰阶

36.g1(n)、g2(n):控制信号

37.rst:重置信号

38.k~n25、n51~n53、n55、n56、n61~n63、n65~n68、n41~n47:节点

39.p31~p315、p51~p57、p71~p721、p81(1)~p81(n)、p82(1)~p82(n)、p83(1)~p83(n)、p84(1)~p84(n):期间

40.vgh:禁能电压电平

41.vgl:致能电压电平

42.vsi、vs(0)~vs(l)、vdd、vss:电压电平

43.i2、i4:电流

44.t41~t410:开关

45.c2、c41、c42:电容

具体实施方式

46.于本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。“连接”或“耦接”亦可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。除非上下文清楚指明,否则该用语并非特别指称或暗示次序或顺位,亦非用以限定本发明。

47.除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本发明所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本发明的上下文中的含义一致的

含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

48.这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括多个形式,包括“至少一个”。“或”表示“及/或”。如本文所使用的,术语“及/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”及/或“包含”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

49.以下将以附图公开本公开的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本公开。也就是说,在本公开内容部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些现有惯用的结构与元件在附图中将以简单示意的方式示出的。

50.图1为根据本公开的一实施例所示出的显示器100的示意图。请参照图1,显示器100包括显示装置110、扫描装置120、数据输入装置130与发光控制装置140。在一些实施例中,显示器100可以由玻璃基板或塑胶基板所制成,但不限于此。

51.在一些实施例中,扫描装置120通过扫描线sl(0)~sl(n)提供扫描信号,例如图2所示的扫描信号gs,至显示装置110。数据输入装置130通过数据线dl(1)~dl(m)提供数据信号,例如图2所示的数据信号dtw(m)及dta(m),至显示装置110。发光控制装置140通过发光线el(1)~el(n)提供发光信号,例如图2所示的发光信号em,至显示装置110。其中n与m皆为正整数。

52.在一些实施例中,扫描装置120、数据输入装置130及发光控制装置140更用以提供如图2中所示的其他信号,例如驱动信号pwmd、ampd及夹止(pinch off)信号ppo,至显示装置110,但本发明实施例不限于此。在各种实施例中,提供驱动信号pwmd、ampd及夹止(pinch off)信号ppo至显示装置110的各种配置方式亦在本发明实施例思及范围内。

53.如图1所示,显示装置110包含多级彼此串接的像素驱动电路dv(1)~dv(n),其中包含像素驱动电路112。在一些实施例中,显示装置110中的像素驱动电路112依据扫描装置120、数据输入装置130与发光控制装置140提供的信号进行驱动操作。

54.图2为根据本公开的一实施例所示出的显示装置110中的像素驱动电路200的方框图。像素驱动电路200为显示装置110中的像素驱动电路112的一种实施例。

55.如图2所示,像素驱动电路200包括控制单元210、220及驱动单元230、240。如图2所示,在一些实施例中,像素驱动电路200还包括电容c2及发光元件l2。在不同的实施例中,发光元件l2可以是微发光二极管(mled)、有机发光二极管(oled)或其他不同类型的发光元件。

56.如图2所示,驱动单元240用以依据数据信号dta(m)产生电流i2,使得发光元件l2依据电流i2发光。在一些实施例中,数据信号dta(m)是脉冲幅度调制(pulse amplitude modulation,pam)数据信号。在一些实施例中,驱动单元240更用以依据驱动信号ampd调整电流i2的电流值,使得电流i2维持在发光元件l2的最佳效率点。

57.如图2所示,控制单元220用以接收电流i2,并依据发光信号em提供电流i2至发光元件l2,使得发光元件l2依据电流i2发光。

58.如图2所示,控制单元210用以依据发光信号ge控制驱动单元240,以调整电流i2。

在一些实施例中,控制单元210更用以接收具有电压电平vdd的电压信号dd。

59.如图2所示,驱动单元230用以通过电容c2接收扫描信号gs,并依据扫描信号gs操作驱动单元240,以调整电流i2。在一些实施例中,驱动单元230更用以依据夹止信号ppo将电流i2在特定时间截止。

60.如图2所示,发光元件l2的一端耦接控制单元220,发光元件l2的另一端用以接收具有电压电平vss的电压信号ss。在一些实施例中,电压电平vdd大于电压电平vss。

61.图3为根据本发明的一实施例中的像素驱动电路200进行发光操作所示出的时序图310及对应的灰阶亮度关系图320。

62.如图3所示,时序图310的横轴对应时间,时序图310的纵轴对应电压电平或电流电平。时序图310包括按序且连续排列的期间p31~p315。在一些实施例中,期间p31~p315对应一框时间(frame time)。在一些实施例中,时序图310对应图2所示的不同信号,例如扫描信号gs及发光信号ge的操作。

63.在一些实施例中,时序图310包含曲线c21~c29,曲线c21~c29对应图2所示的电流i2的依据像素驱动电路200的不同情况进行的不同操作。举例来说,曲线c21对应电流i2在时刻t21截止的实施例,曲线c22对应电流i2在时刻t22截止的实施例,且曲线c23对应电流i2在时刻t23截止的实施例,以此类推。在一些实施例中,电流i2截止代表通过发光元件l2的电流i2的电流电平被拉至零电流电平,因此发光元件l2不发光。换言之,在曲线c21对应的实施例中,发光元件l2从时刻t20发光至时刻t21,并在时刻t21停止发光。在曲线c22对应的实施例中,发光元件l2从时刻t20发光至时刻t22,并在时刻t22停止发光。在曲线c23对应的实施例中,发光元件l2从时刻t20发光至时刻t23,并在时刻t23停止发光,以此类推。

64.如图3所示,灰阶亮度关系图320的横轴对应人眼观察像素驱动电路200时所感受到的灰阶,灰阶亮度关系图320的纵轴对应像素驱动电路200的亮度。在一些实施例中,灰阶会随着亮度增加而增加。如图3所示,灰阶亮度关系图320包含曲线gc2。曲线gc2代表像素驱动电路200的不同亮度所对应的不同灰阶。在一些实施例中,曲线gc2为单调递增函数。如图3所示,曲线gc2在灰阶较低时的斜率较小,且曲线gc2在灰阶较高时的斜率较大。换言之,相较于较高灰阶的状况,在较低灰阶时,灰阶受到亮度的影响较为剧烈。在一些实施例中,灰阶亮度关系图320对应伽马校正(gamma correction)的关系图,亦即伽马曲线(gamma curve)图。

65.请参照灰阶亮度关系图320及时序图310,在一些实施例中,灰阶会随着发光元件l2发光的时间长度增加而增加。举例来说,在曲线c21对应的实施例中,发光元件l2从时刻t20发光至时刻t21,像素驱动电路200具有对应的灰阶lp21。在曲线c22对应的实施例中,发光元件l2从时刻t20发光至时刻t22,像素驱动电路200具有对应的灰阶lp22。如图3所示,从时刻t20至时刻t22的时间长度大于从时刻t20至时刻t21的时间长度。对应地,灰阶lp22大于灰阶lp21。类似地,曲线c23对应的灰阶lp23大于曲线c22对应的灰阶lp22。如上所述,像素驱动电路200可以通过在不同的时刻截止电流i2以调整像素驱动电路200的灰阶。

66.如图3所示,在期间p31,扫描信号gs从电压电平vsi降至电压电平vs(0),并且具有一第一斜率。在一些实施例中,第一斜率为((vsi-vs(0))/期间p31的时间长度)。在一些实施例中,第一斜率对应低灰阶。举例来说,第一斜率对应小于或等于三十二的灰阶值。

67.在期间p31,发光信号ge具有致能电压电平vgl,控制单元210依据发光信号ge控制

驱动单元240,且驱动单元230可以依据夹止信号ppo控制驱动单元240截止电流i2。举例来说,依据不同的夹止信号ppo,驱动单元240可以在时刻t21、t22或t23截止电流i2,但本发明实施例不限于此。在各种实施例中,驱动单元240可以依据夹止信号ppo在期间p31中的任一时刻截止电流i2。

68.如图3所示,在期间p32,扫描信号gs从电压电平vs(0)降至电压电平vs(1),并且具有一第二斜率。在一些实施例中,第二斜率为((vs(0)-vs(1))/期间p32的时间长度)。在一些实施例中,第一斜率大于第二斜率。

69.在期间p32,发光信号ge具有禁能电压电平vgh,且驱动单元240可以依据夹止信号ppo在期间p32中截止电流i2。在一些实施例中,若电流i2在期间p32中截止,则像素驱动电路200具有灰阶值三十二。

70.如图3所示,在期间p33,扫描信号gs具有电压电平vs(1),且斜率实质上等同于零。在一些实施例中,期间p32对应的第二斜率大于零。

71.在期间p33,发光信号ge具有致能电压电平vgl,控制单元210依据发光信号ge控制驱动单元240,使得驱动单元240提供电流i2至发光元件l2。若电流i2在期间p32中未被截止,则在期间p33,发光元件l2依据电流i2发光。

72.如图3所示,在期间p34,扫描信号gs从电压电平vs(1)降至电压电平vs(2),并且具有一第三斜率。在一些实施例中,第三斜率为((vs(1)-vs(2))/期间p34的时间长度)。在一些实施例中,第一斜率大于第三斜率。在不同实施例中,第三斜率与第二斜率可以相同也可以不同。在一些实施例中,第三斜率大于零。

73.在期间p34,发光信号ge具有禁能电压电平vgh,且驱动单元240可以依据夹止信号ppo在期间p34中截止电流i2。曲线c24对应在期间p34中截止电流i2的实施例。

74.请参照灰阶亮度关系图320及时序图310,在一些实施例中,若电流i2在期间p34中截止,则像素驱动电路200具有灰阶lp24。在一些实施例中,灰阶lp24对应灰阶值三十三。

75.如图3所示,在期间p35,扫描信号gs具有电压电平vs(2),且扫描信号gs的斜率实质上等同于零。

76.在期间p35,发光信号ge具有致能电压电平vgl,控制单元210依据发光信号ge控制驱动单元240,使得驱动单元240提供电流i2至发光元件l2。若电流i2在期间p34中未被截止,则在期间p35,发光元件l2依据电流i2发光。

77.如图3所示,在期间p36,扫描信号gs从电压电平vs(2)降至电压电平vs(3),并且具有一第四斜率。在一些实施例中,第四斜率为((vs(2)-vs(3))/期间p36的时间长度)。在一些实施例中,第一斜率大于第四斜率。在不同实施例中,第四斜率与第二斜率及/或第三斜率可以相同也可以不同。在一些实施例中,第四斜率大于零。

78.在期间p36,发光信号ge具有禁能电压电平vgh,且驱动单元240可以依据夹止信号ppo在期间p36中截止电流i2。曲线c25对应在期间p36中截止电流i2的实施例。

79.请参照灰阶亮度关系图320及时序图310,在一些实施例中,若电流i2在期间p36中截止,则像素驱动电路200具有灰阶lp25。在一些实施例中,灰阶lp25对应灰阶值三十四。

80.如灰阶亮度关系图320所示,在灰阶较高时,进一步提升灰阶所需要的发光时间长度较长。换言之,相较于从灰阶值三十二提升至灰阶值三十三所对应的期间p33的时间长度,从灰阶值三十三提升至灰阶值三十四所对应的期间p35的时间长度较长。

81.如图3所示,在期间p37,扫描信号gs具有电压电平vs(3),且扫描信号gs的斜率实质上等同于零。

82.在期间p37,发光信号ge具有致能电压电平vgl,控制单元210依据发光信号ge控制驱动单元240,使得驱动单元240提供电流i2至发光元件l2。若电流i2在期间p36中未被截止,则在期间p37,发光元件l2依据电流i2发光。

83.如图3所示,在期间p38,扫描信号gs从电压电平vs(3)降至电压电平vs(4),并且具有一第五斜率。在一些实施例中,第五斜率为((vs(3)-vs(4))/期间p38的时间长度)。在一些实施例中,第一斜率大于第五斜率。在不同实施例中,第五斜率与第二斜率、第三斜率及/或第四斜率可以相同也可以不同。

84.在期间p38,发光信号ge具有禁能电压电平vgh,且驱动单元240可以依据夹止信号ppo在期间p38中截止电流i2。曲线c26对应在期间p38中截止电流i2的实施例。

85.请参照灰阶亮度关系图320及时序图310,在一些实施例中,若电流i2在期间p38中截止,则像素驱动电路200具有灰阶lp26。在一些实施例中,灰阶lp26对应灰阶值三十五。

86.如灰阶亮度关系图320所示,在灰阶较高时,进一步提升灰阶所需要的发光时间长度较长。换言之,相较于从灰阶值三十三提升至灰阶值三十四所对应的期间p35的时间长度,从灰阶值三十四提升至灰阶值三十五所对应的期间p35的时间长度较长。

87.在一些实施例中,从期间p33开始,发光信号ge具有致能电压电平vgl的期间(例如期间p35、p37)的时间长度依据曲线gc2对应灰阶按序递增。举例来说,相较于从灰阶值k提升至灰阶值(k+1)所对应的期间的时间长度,从灰阶值(k+1)提升至灰阶值(k+2)所对应的期间的时间长度较长。

88.在一些实施例中,k为大于三十二的整数。

89.期间p39的操作类似于期间p37的操作,因此部分细节不再重复说明。在一些实施例中,期间p39的时间长度大于期间p37的时间长度。

90.在期间p310中,像素驱动电路200进行类似于期间p32~p39的操作。在期间p310中,发光信号ge在致能电压电平vgl及禁能电压电平vgh之间切换,且发光信号ge具有致能电压电平vgl的多个期间的多个时间长度对应灰阶的增加而逐渐增加。扫描信号gs在发光信号ge具有禁能电压电平vgh时降低,并具有彼此相同或彼此不同的斜率。扫描信号gs在发光信号ge具有致能电压电平vgl时具有实质上等同于零的斜率。驱动单元240可以依据夹止信号ppo在发光信号ge具有禁能电压电平vgh的期间中截止电流i2,以达到所欲灰阶。

91.像素驱动电路200在期间p311~p315对应电压电平vs(l-2)、vs(l-1)及vs(l)的操作类似于像素驱动电路200在期间p35~p37对应电压电平vs(1)、vs(2)及vs(3)的操作,因此部分细节不再重复说明。在一些实施例中,正整数l对应像素驱动电路200的最高灰阶lp29。在一些实施例中,正整数l大于二百四十。

92.请参照灰阶亮度关系图320及时序图310,曲线c27~c29分别对应像素驱动电路200具有灰阶lp27~lp29的实施例。

93.在一些实施例中,在期间p32、p34、p36、p38、p312及p314中,扫描信号gs的电压电平下降。对应地,期间p32、p34、p36、p38、p312及p314被称为下降期间。在一些实施例中,在期间p33、p35、p37、p39、p311、p13及p315中,发光元件l2依据电流i4发光。对应地,期间p33、p35、p37、p39、p311、p13及p315被称为发光期间。

94.如图3所示,在期间p32~p315中,多个下降期间及多个发光期间交替排列。发光信号ge在发光期间中具有禁能电压电平vgh,并且在下降期间中具有致能电压电平vgl。

95.如图3所示,发光期间的时间长度在框时间中按序递增。举例来说,期间p33、p35、p37、p39、p311、p13及p315的时间长度按序递增。每一发光期间对应像素驱动电路200的一个灰阶,且期间p31可以对应像素驱动电路200的多个灰阶。举例来说,发光期间p32、p34及p36分别对应灰阶lp23、lp24、lp25及lp26,且期间p31可以对应小于或等于灰阶lp23的任意灰阶。

96.在一些先前的作法中,由于低灰阶的情况所对应的发光时间非常短,低发光时间驱动类型(例如多脉冲模式(multi-pulse mode))的面板会面临非常短暂的发光时间,使用者不容易控制及调整像素驱动电路的灰阶。

97.相较于上述作法,在本发明实施例中,通过期间p31的操作精细地控制低灰阶的发光时间,并且在中灰阶及高灰阶通过多个下降期间及按序递增的多个发光期间,以类数字的方式依据伽马曲线调控灰阶。如此一来,通过扫描信号gs及发光信号ge的操作,像素驱动电路200可以更精确的调控灰阶。

98.图4为根据本公开的一实施例所示出的显示装置110中的像素驱动电路400的方框图。像素驱动电路400为显示装置110中的像素驱动电路112的一种实施例。像素驱动电路400亦为图2所示的像素驱动电路200的一种实施例。

99.请参照图2及图4,像素驱动电路400包括控制单元410、420、驱动单元430、440、发光元件l4及电容c41。控制单元410、420、驱动单元430、440、发光元件l4及电容c41的功能及操作方式分别类似于控制单元210、220、驱动单元230、240、发光元件l2及电容c2,因此重复的处于此不再赘述。

100.如图4所示,控制单元410包括开关t41及电容c42。开关t41的控制端用以接收发光信号ge,开关t41的一端用以接收电压信号dd,开关t41的另一端耦接节点n41。电容c42的一端耦接开关t41于节点n42,电容c42的一端耦接节点n43。

101.如图4所示,控制单元420包括开关t42。开关t42的一端耦接节点n44,开关t42的另一端耦接发光元件l4于节点n45。

102.如图4所示,驱动单元430包括开关t43~t46。开关t43的控制端用以接收发光信号em,开关t43的一端用以接收夹止信号ppo,开关t43的另一端耦接节点n46。开关t44的控制端用以接收控制信号g1(n),开关t44的一端用以接收数据信号dtw(m),开关t44的另一端耦接节点n46。开关t45的控制端用以接收控制信号g1(n),开关t45的一端耦接节点n43,开关t45的另一端耦接电容c41于节点n47。开关t46的控制端耦接节点n47,开关t46的一端耦接节点n43,开关t46的另一端耦接节点n46。

103.如图4所示,驱动单元440包括开关t47~t410。开关t47的控制端用以接收控制信号g2(n),开关t47的一端用以接收数据信号dta(m),开关t47的另一端耦接节点n41。开关t48的控制端用以接收控制信号g2(n),开关t48的一端耦接节点n43,开关t48的另一端耦接节点n44。开关t49的控制端耦接节点n43,开关t49的一端耦接节点n41,开关t49的另一端耦接节点n44。开关t410的控制端用以接收重置信号rst,开关t410的一端耦接节点n43,开关t410的另一端用以接收电压信号rstd。

104.在一些实施例中,发光元件l4用以依据按序流经开关t41、t49、t42的电流i4发光。

105.在图4所示的实施例中,开关t41~t410是通过p型金属氧化物半导体(pmos)场效晶体管实施,但本发明实施例不限于此。在不同的实施例中,开关t41~t410也可以通过n型金属氧化物半导体(nmos)场效晶体管、薄膜晶体管(tft)或其他不同类型的开关元件实施。

106.图5为根据本发明的一实施例中的像素驱动电路400进行发光操作所示出的时序图500。时序图500按序包括期间p51~p57。在一些实施例中,时序图500对应图4所示的不同信号,例如扫描信号gs、发光信号em、ge、重置信号rst及控制信号g1(n)、g2(n)的操作。

107.如图5所示,在期间p51,重置信号rst及控制信号g1(n)具有致能电压电平vgl,使得开关t410、t44及t45导通。此时电压信号rstd按序经由开关t410及t45写入节点n43及n47以重置节点n43及n47的电压。

108.如图5所示,在期间p52,控制信号g1(n)具有致能电压电平vgl,使得开关t44及t45导通。扫描信号gs具有致能电压电平vsl,使得电容c41依据扫描信号gs将节点n47的电压拉至致能电压电平,以导通开关t46。数据信号dtw(m)按序经由开关t44、t46及t45写入节点n47。此时驱动单元430依据开关t46的临界电压电平补偿节点n47的电压。

109.如图5所示,在期间p53,扫描信号gs被拉至电压电平vsh,使得像素驱动电路400可以在随后的发光期间(例如期间p57)中依据电压电平逐渐降低的扫描信号gs进行发光操作。此时电容c41用以存储数据信号dtw(m)于节点n47,使得发光元件l4在之后的期间(例如期间p57)中可以依据数据信号dtw(m)发光。

110.如图5所示,在期间p54,重置信号rst具有致能电压电平vgl,使得开关t410导通。此时电压信号rstd经由开关t410写入节点n43以重置节点n43的电压,并且导通开关t49。

111.如图5所示,在期间p55,控制信号g2(n)具有致能电压电平vgl,使得开关t47及t48导通。数据信号dta(m)按序经由开关t47、t49及t48写入节点n43。此时驱动单元440依据开关t49的临界电压电平补偿节点n43的电压。

112.如图5所示,在期间p56,发光信号em具有致能电压电平vgl,使得开关t43及t42导通。在一些实施例中,开关t43及t42在发光期间(例如期间p57)之前导通,以确保发光元件t42可以在发光期间依据扫描信号gs及发光信号ge进行发光操作。

113.如图5所示,在期间p57,发光信号em具有致能电压电平vgl,使得开关t43及t42导通。开关t41接收具有电压电平dd的电压信号vdd,并且依据发光信号ge导通。开关t49依据节点n43的电压导通。此时电流i4按序通过开关t41、t49、t42及发光元件l4,使得发光元件l4依据电流i4的电流电平发光。在一些实施例中,开关t41依据发光信号ge调整电流i4的电流电平,且开关t49依据节点n43的电压调整电流i4的电流电平。

114.在期间p57,开关t46依据扫描信号gs导通,使得夹止信号ppo按序通过开关t43及t46写入节点n43,以调整节点n43的电压。换言之,开关t49依据夹止信号ppo及扫描信号gs调整电流i4的电流电平。

115.在一些实施例中,电流i4、扫描信号gs及发光信号ge在期间p57的操作类似于图2及图3所示的电流i2、扫描信号gs及发光信号ge在期间p31~p315的操作,因此部分细节不再重复说明。在一些实施例中,期间p57包含期间p31~p315。

116.图6为根据本公开的一实施例所示出的显示装置600的示意图。请参照图1及图6,显示装置600为显示装置110的一种实施例。如图6所示,显示装置600包含像素驱动电路610及620。请参照图2、图4及图6,像素驱动电路610及620的每一者可以具有类似于像素驱动电

路200及/或像素驱动电路400的配置方式及连接关系。

117.如图6所示,像素驱动电路610用以接收扫描信号gs61及发光信号ge61,并且像素驱动电路620用以接收扫描信号gs62及发光信号ge62。在一些实施例中,像素驱动电路610对应扫描信号gs61及发光信号ge61的操作类似于像素驱动电路200及/或像素驱动电路400对应扫描信号gs及发光信号ge的操作。在一些实施例中,像素驱动电路620对应扫描信号gs62及发光信号ge62的操作类似于像素驱动电路200及/或像素驱动电路400对应扫描信号gs及发光信号ge的操作。因此,部分细节不再重复说明。

118.图7为根据本发明的一实施例中的像素驱动电路610及620进行发光操作所示出的时序图700。

119.如图7所示,时序图700的横轴对应时间,时序图700的纵轴对应电压电平或电流电平。时序图700包括按序且连续排列的期间p71~p721。在一些实施例中,期间p71~p721对应一框时间。在一些实施例中,时序图700对应图6所示的不同信号,例如扫描信号gs61、gs62及发光信号ge61、ge62的操作。

120.如图7所示,在期间p71,扫描信号gs61降低并且具有第一斜率。发光信号ge61具有致能电压电平vgl。像素驱动电路610可以在期间p71中截止流经像素驱动电路610的电流以决定像素驱动电路610的灰阶。

121.如图7所示,在期间p72~p74,扫描信号gs61降低并且具有不同于第一斜率的第二斜率。发光信号ge61具有禁能电压电平vgh。像素驱动电路610可以在期间p72~p74中截止流经像素驱动电路610的电流以决定像素驱动电路610的灰阶。

122.如图7所示,在期间p75,扫描信号gs61的斜率实质上等同于零。发光信号ge61具有致能电压电平vgl。像素驱动电路610依据电流在期间p72~p74中是否截止而发光或不发光。

123.如图7所示,在期间p76~p78,扫描信号gs61降低并且具有不同于第一斜率的第三斜率。在各种实施例中,第三斜率及第二斜率可以相同也可以不同。发光信号ge61具有禁能电压电平vgh。像素驱动电路610可以在期间p76~p78中截止流经像素驱动电路610的电流以决定像素驱动电路610的灰阶。

124.如图7所示,在期间p79,扫描信号gs61的斜率实质上等同于零。发光信号ge61具有致能电压电平vgl。像素驱动电路610依据电流在期间p76~p78中是否截止而发光或不发光。

125.如图7所示,在期间p710~p712,扫描信号gs61降低并且具有不同于第一斜率的第四斜率。在各种实施例中,第三斜率及第四斜率可以相同也可以不同。发光信号ge61具有禁能电压电平vgh。像素驱动电路610可以在期间p710~p712中截止流经像素驱动电路610的电流以决定像素驱动电路610的灰阶。

126.在一些实施例中,期间p72~p74、p76~p78及p710~p712的时间长度按序递增。在一些实施例中,期间p75及p79的时间长度按序递增。

127.在期间p713中,像素驱动电路610进行类似于期间p72~p712的操作。在期间p713中,发光信号ge61在致能电压电平vgl及禁能电压电平vgh之间切换,且发光信号ge61具有致能电压电平vgl的多个期间的多个时间长度以及具有禁能电压电平vgh的多个期间的多个时间长度对应灰阶的增加而逐渐增加。扫描信号gs61在发光信号ge61具有禁能电压电平

vgh时降低,并具有彼此相同或彼此不同的斜率。扫描信号gs61在发光信号ge61具有致能电压电平vgl时具有实质上等同于零的斜率。驱动单元610可以依据夹止信号(例如图2所示的夹止信号ppo)在发光信号ge61具有禁能电压电平vgh的期间中截止流经像素驱动电路610的电流,以达到所欲灰阶。

128.像素驱动电路610在期间p714、p715、p716~p718、p719、p720~p721的操作分别类似于像素驱动电路610在期间p74、p75、p76~p78、p79、p710~p711的操作,因此部分细节不再重复说明。在一些实施例中,期间p79、p715及p719的时间长度按序递增。在一些实施例中,期间p710~p712及p716~p718的时间长度按序递增。

129.请参照图3及图6,扫描信号gs61及发光信号ge61在期间p71~p721的操作类似于扫描信号gs及发光信号ge在期间p31~p315的操作。举例来说,期间p71对应期间p31,期间p72~p74对应期间p32,期间p75对应期间p33,期间p76~p78对应期间p34,且期间p79对应期间p35。

130.如图7所示,在期间p73,扫描信号gs62降低并且具有第一斜率。发光信号ge62具有致能电压电平vgl。像素驱动电路620可以在期间p73中截止流经像素驱动电路620的电流以决定像素驱动电路620的灰阶。

131.如图7所示,在期间p74~p76,扫描信号gs62降低并且具有第二斜率。发光信号ge62具有禁能电压电平vgh。像素驱动电路620可以在期间p74~p76中截止流经像素驱动电路620的电流以决定像素驱动电路620的灰阶。

132.如图7所示,在期间p77,扫描信号gs62的斜率实质上等同于零。发光信号ge62具有致能电压电平vgl。像素驱动电路620依据电流在期间p74~p76中是否截止而发光或不发光。

133.如图7所示,在期间p78~p710,扫描信号gs62降低并且具有第三斜率。发光信号ge62具有禁能电压电平vgh。像素驱动电路620可以在期间p78~p710中截止流经像素驱动电路620的电流以决定像素驱动电路620的灰阶。

134.如图7所示,在期间p711,扫描信号gs62的斜率实质上等同于零。发光信号ge具有致能电压电平vgl。像素驱动电路620依据电流在期间p78~p710中是否截止而发光或不发光。

135.在一些实施例中,期间p74~p76及p78~p710的时间长度按序递增。在一些实施例中,期间p77及p711的时间长度按序递增。

136.在期间p712~p713中,像素驱动电路620进行类似于期间p73~p711的操作。在期间p713中,发光信号ge62在致能电压电平vgl及禁能电压电平vgh之间切换,且发光信号ge62具有致能电压电平vgl的多个期间的多个时间长度以及具有禁能电压电平vgh的多个期间的多个时间长度对应灰阶的增加而逐渐增加。扫描信号gs62在发光信号ge62具有禁能电压电平vgh时降低,并具有彼此相同或彼此不同的斜率。扫描信号gs62在发光信号ge62具有致能电压电平vgl时具有实质上等同于零的斜率。驱动单元620可以依据夹止信号(例如图2所示的夹止信号ppo)在发光信号ge62具有禁能电压电平vgh的期间中截止流经像素驱动电路620的电流,以达到所欲灰阶。

137.像素驱动电路620在期间p714~p716、p717、p718~p720、p721的操作分别类似于像素驱动电路620在期间p74~p76、p77、p78~p710、p711的操作,因此部分细节不再重复说

明。在一些实施例中,期间p711、p717及p721的时间长度按序递增。在一些实施例中,期间p78~p710、p714~p716及p718~p720的时间长度按序递增。

138.请参照图3及图6,扫描信号gs62及发光信号ge62在期间p73~p721的操作类似于扫描信号gs及发光信号ge在期间p31~p315的操作。举例来说,期间p73对应期间p31,期间p74~p76对应期间p32,期间p77对应期间p33,期间p78~p710对应期间p34,且期间p711对应期间p35。

139.如上所述,发光信号ge61及ge62交替地(例如在期间p73、p75、p77及p79中)具有致能电压电平vgl及禁能电压电平vgh,使得流经显示装置600的总电流下降。

140.图8为根据本发明的一实施例中的显示装置110进行发光操作所示出的时序图800。时序图800包括按序且连续排列的期间p81(i)~p85(i),其中i为小于或等于n的正整数。时序图800对应扫描信号gs(i)及发光信号ge(i)的操作。请参照图1及图8,在一些实施例中,像素驱动电路dv(i)用以依据扫描信号gs(i)及发光信号ge(i)进行发光操作。像素驱动电路dv(i)依据扫描信号gs(i)及发光信号ge(i)进行的操作类似于如图2及图3所示的像素驱动电路200依据扫描信号gs及发光信号ge进行的操作,因此部分细节不再重复说明。

141.如图8所示,在图8中具体示出了扫描信号gs(1)、gs(2)、gs(n)及发光信号ge(1)、ge(2)、ge(n)在期间p81(1)~p85(1)、p81(2)~p85(2)及p81(n)~p85(n)的波形。为了简洁起见,扫描信号gs(3)~gs(n-1)及发光信号ge(3)~ge(n-1)的波形在图8中未示出。

142.在期间p81(1),像素驱动电路dv(1)进行类似于图5所示的期间p51~p55的数据写入操作,使得数据信号被写入像素驱动电路dv(1)。

143.在期间p82(1),像素驱动电路dv(1)进行类似于图5所示的期间p57的发光操作,使得像素驱动电路dv(1)依据在期间p81(1)写入的数据信号发光。

144.在期间p83(1),像素驱动电路dv(1)截止用于发光的电流,使得像素驱动电路dv(1)不发光。在一些实施例中,期间p83(1)被称为发光间隔(emission blanking)期间。

145.在期间p84(1),像素驱动电路dv(1)进行类似于图5所示的期间p54~p55的重置操作,使得像素驱动电路dv(1)内部的节点电压被重置。

146.在期间p85(1),像素驱动电路dv(1)进行类似于图5所示的期间p57的发光操作,使得像素驱动电路dv(1)依据在期间p81(1)写入的数据信号发光。

147.在一些实施例中,期间p81(1)~p85(1)对应一个框时间。在一个框时间中,像素驱动电路dv(1)进行一次数据写入操作(例如在期间p81(1)中的操作),并且依据写入的数据信号进行两次发光操作(例如在期间p82(1)及p85(1)中的操作),但本发明实施例不限于此。在各种实施例中,在一个框时间中,像素驱动电路dv(1)可以再进行一次数据写入操作后,依据写入的数据信号进行多次发光操作。举例来说,在一个框时间中,像素驱动电路dv(1)重复进行多次对应期间p84(1)~p85(1)的重置操作及发光操作。

148.在一些先前的作法中,在一个框时间中,像素驱动电路在数据写入操作后,仅进行一次发光操作。在上述作法中,框时间中发光间隔期间较长,使得闪烁(flicker)现象较为严重。

149.相较于上述作法,在本发明实施例中,在一个框时间(例如期间p81(1)~p85(1))中,像素驱动电路dv(1)进行多次发光操作,使得框时间中的总发光时间增加且发光间隔期间对应减少。如此一来,显示装置110的闪烁现象降低。

150.如图8所示,扫描信号gs(i)及发光信号ge(i)在期间p81(i)~p85(i)的操作类似于扫描信号gs(1)及发光信号ge(1)在期间p81(1)~p85(1)的操作,因此部分细节不再重复说明。

151.如图8所示,期间p81(1)~p81(n)按序排列。举例来说,期间p81(i+1)在期间p81(i)开始之后开始。在一些实施例中,期间p81(i+1)及期间p81(i)可能有部分重叠的时间。

152.类似地,期间p82(1)~p82(n)按序排列,期间期间p83(1)~p83(n)按序排列,p84(1)~p84(n)按序排列,且期间p85(1)~p85(n)按序排列。如此一来,图1所示的显示装置110中的多列像素驱动电路依据扫描信号gs(1)~gs(n)及发光信号ge(1)~ge(n)按序进行发光操作。

153.举例来说,在期间p82(1)~p82(n)的每一者中,扫描信号gs(1)~gs(n)的每一者按序具有第一斜率、第二斜率及第三斜率。由于期间p82(1)~p82(n)按序排列,扫描信号gs(1)~gs(n)按序具有第一斜率。对应地,像素驱动电路dv(1)~dv(n)按序依据第一斜率发光。

154.在一些实施例中,期间p82(i+1)及期间p82(i)可能有部分重叠的时间,期间p83(i+1)及期间p83(i)可能有部分重叠的时间,且期间p84(i+1)及期间p84(i)可能有部分重叠的时间。

155.本公开前述各种检测方式及发光操作的方式用于说明,其他各种检测方式以及发光操作的方式都在本公开思及的范围中。

156.综上所述,在本发明实施例中,像素驱动电路200在期间p31中依据第一斜率进行低灰阶的发光操作,且在期间p32~p315中依据按序递增的多个发光期间进行中高灰阶的发光操作,使得像素驱动电路200可以更精确的调控灰阶。

157.虽然本发明已以实施例公开如上,然其并非用以限定本发明,任何所属技术领域中技术人员,在不脱离本发明的构思和范围内,当可作些许的变动与润饰,故本发明的保护范围当视权利要求所界定者为准。