1.本技术涉及显示技术领域,具体涉及一种阵列基板及显示装置。

背景技术:

2.液晶显示面板(liquid crystal display pane1,lcd pane1)已经成为相当普遍的产品,双栅线(dual gate)技术是目前lcd产品中常用的技术。双栅线(dual gate)技术是将显示装置中的数据线的数量减少一半,栅线的数量增加一倍的驱动技术,即,将与数据线连接的源极驱动集成电路数量减半,将与栅线连接的栅极驱动集成电路的数量加倍。由于栅极驱动集成电路的单价比源极驱动集成电路的单价便宜,从而实现成本的降低。

3.目前在液晶显示面板的像素驱动电路中,常采用行反转(column inversion)结构的驱动电路以降低驱动电路功耗,并搭配双栅线(dual gate)技术实现成本的降低,但是搭配双栅极(dual gate)驱动电路架构或其类似架构在显示纯色画面时会出现摇头纹(vertical line)的现象。且双栅线(dual gate)技术的使用,导致薄膜晶体管的源极与数据线连接时存在长短差异,导致各个线两侧的像素电极受到不同大小的栅极(gate)电压的拉动,像素存储电容的均一性较差,进一步导致摇头纹现象严重,大大影响了显示效果。

4.因此,亟需一种新的液晶显示面板的阵列结构以改善液晶显示面板的摇头纹的问题。

技术实现要素:

5.针对上述问题,本技术提供了一种阵列基板及显示装置,解决了现有技术中液晶显示面板的摇头纹现象严重的技术问题。

6.第一方面,本技术提供一种阵列基板,包括:

7.衬底基板;

8.间隔设置于所述衬底基板上且沿行方向延伸的多个栅线组,以及沿列方向延伸的多条公共线和多条数据线;其中,所述公共线和所述数据线交替设置,所述栅线组与所述公共线和所述数据线绝缘交叠以限定出多个像素区域;

9.设置于所述衬底基板上且位于所述多个像素区域内的多个像素电极;

10.其中,每一列所述多个像素电极包括沿列方向交替排列的第一子像素电极和第二子像素电极;位于同一列的所述第一子像素电极和所述第二子像素电极分别通过第一薄膜晶体管和第二薄膜晶体管连接至与该列所述像素电极相邻的两条所述数据线;所述第一子像素电极与其连接的所述数据线之间的距离,小于所述第二子像素电极与其连接的所述数据线之间的距离;

11.在所述第一薄膜晶体管远离其连接的所述数据线的一侧设置有第一连接部,所述第一连接部与相邻的所述公共线绝缘交叠。

12.在一些实施例中,上述阵列基板中,所述第一薄膜晶体管的源极和漏极分别连接所述第一子像素电极和对应的所述数据线,所述第二薄膜晶体管的源极和漏极分别连接所

述第二子像素电极和对应的所述数据线。

13.在一些实施例中,上述阵列基板中,所述第一连接部与所述第一薄膜晶体管的源极连接,并延伸至其相邻的所述公共线与所述衬底基板之间。

14.在一些实施例中,上述阵列基板中,所述第一连接部延伸至相邻的所述公共线远离对应的所述第一薄膜晶体管的一侧。

15.在一些实施例中,上述阵列基板中,所述第二薄膜晶体管的源极通过第二连接部连接所述第二子像素电极;

16.其中,所述第二连接部与相邻的所述公共线交叉绝缘。

17.在一些实施例中,上述阵列基板中,所述第一薄膜晶体管位于其对应的所述第一子像素电极和相邻的所述栅线组之间;

18.所述第二薄膜晶体管位于其对应的所述第二子像素电极和相邻的所述栅线组之间;

19.所述第一连接部和所述第二连接部在衬底基板上的正投影不覆盖所述栅线组在所述衬底基板上的正投影。

20.在一些实施例中,上述阵列基板中,所述第一连接部和所述第二连接部与所述栅线组位于同一层。

21.在一些实施例中,上述阵列基板中,所述第一连接部与其相邻的所述栅线组之间的间距,等于所述第二连接部与其相邻的所述栅线组之间的间距。

22.在一些实施例中,上述阵列基板中,所述公共线包括沿所述列方向延伸的总线,以及与所述总线连接并向相邻的所述第一薄膜晶体管延伸的第三连接部;

23.其中,所述第三连接部与相邻的所述第一连接部绝缘交叠。

24.在一些实施例中,上述阵列基板中,所述第一连接部连接对应的所述第一子像素电极。

25.在一些实施例中,上述阵列基板中,所述第一薄膜晶体管的源极通过第四连接部连接对应的所述第一子像素电极。

26.在一些实施例中,上述阵列基板中,所述阵列基板还包括:

27.覆盖所述栅线组、所述公共线、所述数据线和所述像素电极的第一绝缘层;

28.设置于所述第一绝缘层上方的公共电极;

29.其中,所述公共电极在所述衬底基板上的正投影至少覆盖部分所述公共线和部分像素电极在所述衬底基板上的正投影。

30.在一些实施例中,上述阵列基板中,所述第四连接部包括与所述第一子像素电极连接的第一子连接件,以及连接所述第一子连接件和所述第一薄膜晶体管的源极的第二子连接件。

31.在一些实施例中,上述阵列基板中,所述第二子连接件与所述公共电极位于同一层,所述第一子连接件与所述像素电极位于同一层,所述第二子连接件分别通过第一接触孔和第二接触孔与所述第一子连接件和所述第一薄膜晶体管的源极连接。

32.在一些实施例中,上述阵列基板中,所述公共电极通过至少一个贯穿所述第一绝缘层的第三接触孔与所述公共线连接。

33.在一些实施例中,上述阵列基板中,每个所述栅线组包括间隔设置的第一栅极线

和第二栅极线;

34.所述第一薄膜晶体管和所述第二薄膜晶体管的栅极分别连接所述第一栅极线和所述第二栅极线。

35.在一些实施例中,上述阵列基板中,所述第三接触孔在所述衬底基板上的正投影落入所述栅线组中所述第一栅极线和所述第二栅极线在所述衬底基板上的正投影之间。

36.在一些实施例中,上述阵列基板中,位于同一列的所述像素电极对应显示同一种颜色,且在任意时刻任意相邻两条所述数据线上的数据信号的电平相反。

37.在一些实施例中,上述阵列基板中,分别位于所述公共线两侧的两列所述像素电极中,同一行的两个所述像素电极均为所述第一子像素电极或均为所述第二子像素电极;

38.分别位于所述数据线两侧的两列所述像素电极中,同一行的两个所述像素电极分别为所述第一子像素电极和所述第二子像素电极。

39.在一些实施例中,上述阵列基板中,所述数据线和所述公共线包括在所述衬底基板上方依次叠层设置的第一导电层和第二导电层;

40.其中,所述第一导电层在所述衬底基板上的正投影至少覆盖部分所述第二导电层在所述衬底基板上的正投影;

41.所述第一导电层与所述第一薄膜晶体管和所述第二薄膜晶体管的有源层位于同一层,所述第二导电层与所述第一薄膜晶体管和所述第二薄膜晶体管的源极和漏极位于同一层。

42.在一些实施例中,上述阵列基板中,所述栅线组包括在所述衬底基板上方依次叠层设置的第三导电层和第四导电层;

43.其中,所述第三导电层在所述衬底基板上的正投影至少覆盖部分所述第四导电层在所述衬底基板上的正投影;

44.所述第三导电层与所述像素电极位于同一层。

45.第二方面,本技术提供一种显示装置,包括如第一方面中任一项所述的阵列基板。

46.采用上述技术方案,至少能够达到如下技术效果:

47.本技术提供了一种阵列基板及显示装置,每一列所述多个像素电极包括沿列方向交替排列的第一子像素电极和第二子像素电极;位于同一列的所述第一子像素电极和所述第二子像素电极分别通过第一薄膜晶体管和第二薄膜晶体管连接至与该列所述像素电极相邻的两条所述数据线;所述第一子像素电极与其连接的所述数据线之间的距离,小于所述第二子像素电极与其连接的所述数据线之间的距离;在所述第一薄膜晶体管远离其连接的所述数据线的一侧设置有第一连接部,所述第一连接部与相邻的所述公共线绝缘交叠。本技术中通过在与数据线的连接距离较短的第一薄膜晶体管的一侧设置第一连接部,与公共线绝缘交叠,大大增加了对应像素的存储电容cst,提高了像素存储电容的均一性,确保了本行栅极线关断时,对各个像素电极的电压拉动相同,漏电后的灰阶差异减小,大大避免了摇头纹的出现。

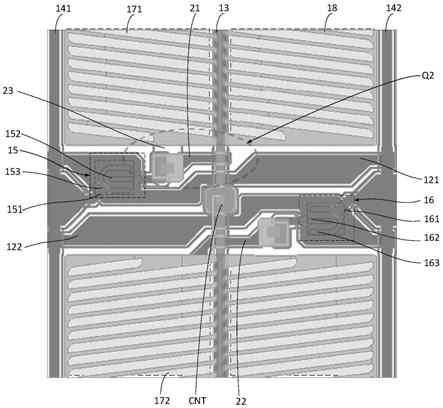

附图说明

48.附图是用来提供对本技术的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本技术,但并不构成对本技术的限制。在附图中:

49.图1是本技术一示例性实施例示出的一种阵列基板的正面俯视示意图;

50.图2是图1中区域q1的一种局部放大图;

51.图3是图2中区域q2的局部放大图;

52.图4是图3沿切线a-a’的剖面结构示意图;

53.图5是图3沿切线b-b’的剖面结构示意图;

54.图6是本技术一示例性实施例示出的像素的亮度分布示意图;

55.图7是图1中区域q1的另一种局部放大图;

56.图8是图7中区域q3的局部放大图;

57.在附图中,相同的部件使用相同的附图标记,附图并未按照实际的比例绘制;

58.附图标记为:

59.11-衬底基板;12-栅线组;121-第一栅极线;122-第二栅极线;13-公共线;131-总线;132-第三连接部;14-数据线;141-第一数据线;142-第二数据线;15-第一薄膜晶体管;151-第一薄膜晶体管的有源层;152-第一薄膜晶体管的源极;153-第一薄膜晶体管的漏极;16-第二薄膜晶体管;161-第二薄膜晶体管的有源层;162-第二薄膜晶体管的源极;163-第二薄膜晶体管的漏极;171-第一子像素电极;172-第二子像素电极;18-公共电极;191-第二绝缘层;192-第一绝缘层;21-第一连接部;211-第三导电层;212-第四导电层;22-第二连接部;23-第四连接部;231-第一子连接件;232-第二子连接件;cnt-第三接触孔。

具体实施方式

60.以下将结合附图及实施例来详细说明本技术的实施方式,借此对本技术如何应用技术手段来解决技术问题,并达到相应技术效果的实现过程能充分理解并据以实施。本技术实施例以及实施例中的各个特征,在不相冲突前提下可以相互结合,所形成的技术方案均在本技术的保护范围之内。在附图中,为了清楚,层和区的尺寸以及相对尺寸可能被夸大。自始至终相同附图标记表示相同的元件。

61.应理解,尽管可使用术语“第一”、“第二”、“第三”等描述各种元件、部件、区、层和/或部分,这些元件、部件、区、层和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层或部分与另一个元件、部件、区、层或部分。因此,在不脱离本技术教导之下,下面讨论的第一元件、部件、区、层或部分可表示为第二元件、部件、区、层或部分。

62.在此使用的术语的目的仅在于描述具体实施例并且不作为本技术的限制。在此使用时,单数形式的“一”、“一个”和“所述/该”也意图包括复数形式,除非上下文清楚指出另外的方式。还应明白术语“组成”和/或“包括”,当在该说明书中使用时,确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

63.为了彻底理解本技术,将在下列的描述中提出详细的结构以及步骤,以便阐释本技术提出的技术方案。本技术的较佳实施例详细描述如下,然而除了这些详细描述外,本技术还可以具有其他实施方式。

64.本技术实施例提供一种阵列基板,请参阅图1,该阵列基板包括衬底基板11、多个栅线组12、多条数据线14、多条公共线13、像素电极、第一薄膜晶体管15和第二薄膜晶体管

16。

65.多个栅线组12间隔设置于衬底基板11上且沿行方向延伸。

66.多条公共线13间隔设置于衬底基板11上且沿列方向延伸,且多条公共线13沿行方向排列。

67.多条数据线14间隔设置于衬底基板11上且沿列方向延伸,且多条数据线14沿行方向排列。

68.公共线13和数据线14沿行方向交替设置,栅线组12与公共线13和数据线14绝缘交叠以限定出多个像素区域(图中未标注)。

69.像素电极设置于衬底基板11上且位于上述像素区域内,像素电极在衬底基板11上的正投影不覆盖栅线组12、公共线13和数据线14在衬底基板11上的正投影。

70.其中,每一列多个像素电极包括沿列方向交替排列的第一子像素电极171和第二子像素电极172。

71.位于同一列的第一子像素电极171和第二子像素电极172分别通过第一薄膜晶体管15和第二薄膜晶体管16连接至与该列像素电极相邻的两条数据线14;第一子像素电极171与其连接的数据线14之间的距离,小于第二子像素电极172与其连接的数据线14之间的距离。在第一薄膜晶体管15远离其连接的数据线14的一侧设置有第一连接部21,第一连接部21与相邻的公共线13绝缘交叠。

72.公共线13在衬底基板11上的正投影至少覆盖部分第一连接部21在衬底基板上的正投影。

73.多条数据线14包括沿行方向交替排列的第一数据线141和第二数据线142。

74.如图2所示,第一列的像素电极中,第一子像素电极171连接第一数据线141(左侧的数据线14),第二子像素电极172连接第二数据线142(右侧的数据线14)。如图1中所示,第一子像素电极171与其连接的第一数据线141的距离远小于第二子像素电极172与其连接的第二数据线142的距离,所以第一薄膜晶体管15与其连接的第一子像素电极171的连接距离较小,受栅极的电压拉动较小,而第二薄膜晶体管16与其连接的第二子像素电极172的距离较大,受栅极的电压拉动较大,产生存储电容差异。

75.而在第一薄膜晶体管15一侧设置的第一连接部21与公共线13绝缘交叠,形成存储电容cst,从而增大了像素存储电容,提高了像素存储电容的均一性,确保了本行栅极线关断时,对第一子像素电极171和第二子像素电极172的电压拉动相同,漏电后的灰阶差异减小,大大避免了摇头纹的出现。

76.第一薄膜晶体管15包括栅极(图中未标注)、有源层151、源极152和漏极153,第二薄膜晶体管16包括栅极(图中未标注)、有源层161、源极162和漏极163。

77.第一薄膜晶体管15的源极152和漏极153分别连接第一子像素电极171和对应的数据线14,第二薄膜晶体管16的源极162和漏极163分别连接第二子像素电极172和对应的数据线14。

78.在一些实施例中,如图2和3所示,第一连接部21与第一薄膜晶体管15的源极152连接,并延伸至其相邻的公共线13与衬底基板11之间。其中,第一连接部21与公共线13之间通过第二绝缘层191隔离。

79.这种结构,在形成存储电容的同时,在第一连接部21与公共线13绝缘交叠的位置,

可以在像素修复时使用。由于第一连接部21与第一薄膜晶体管15的源极152连接,所以在第一薄膜晶体管15对应的像素点由于缺陷导致为亮点时,在第一连接部21与公共线13绝缘交叠的位置通过激光打孔和焊接的方法,将第一连接部21与公共线13焊接在一起,将亮点变成暗点,以不影响整个显示面板的显示画面。

80.在一些实施例中,如图3和图4所示,第一连接部21延伸至相邻的公共线13远离第一薄膜晶体管15的一侧,即使在工艺过程中,工艺或设备误差导致公共线13和第一连接部21的位置发生偏差,也不会影响述公共线13和第一连接部21的交叠面积,仍然能够确保精准的cst补偿,无差异化现象,防止因cst不同而导致的串扰(crosstalk)、显示不良(mura)等问题,确保画质,进一步提高显示效果。

81.在一些实施例中,第二薄膜晶体管16的源极162通过第二连接部22连接第二子像素电极172;其中,由于第二子像素电极172与其连接的数据线14之间的距离较远,所以其对应的第二薄膜晶体管16的源极162与像素电极连接的跨度较大,第二连接部22与相邻的公共线13交叉绝缘,横跨该公共线13与第二子像素电极172连接。

82.第二连接部22与相邻的公共线13交叉绝缘,形成电容,增大了第二像素电极的存储电容cst。这也是第一薄膜晶体管15和第二薄膜晶体管16对应的像素电极的存储电容cst差异的主要原因之一。

83.而本技术中,通过第一连接部21的设置,第一连接部21与公共线13形成另一个存储电容cst,减小了第一薄膜晶体管15和第二薄膜晶体管16对应的像素电极的存储电容cst差异,提高了像素存储电容的均一性,确保了本行栅极线关断时,对第一子像素电极171和第二子像素电极172的电压拉动相同,漏电后的灰阶差异减小,大大避免了摇头纹的出现。

84.第一薄膜晶体管15位于其对应的第一子像素电极171和相邻的栅线组12之间,第二薄膜晶体管16位于其对应的第二子像素电极172和相邻的栅线组12之间。

85.第一连接部21和第二连接部22在衬底基板11上的正投影不覆盖栅线组12在衬底基板11上的正投影。

86.在一些实施例中,第一连接部21和第二连接部22与栅线组12位于同一层。

87.在一些实施例中,第一连接部21和第二连接部22与栅线组12的材料相同,可以为钼、铌、铜等金属层。

88.在一些实施例中,第一连接部21靠近其相邻的栅线组12的一侧各个位置处与该相邻的栅线组12之间的间距相等,第二连接部22靠近其相邻的栅线组12一侧各个位置处与该相邻的栅线组12之间的间距相等。

89.每个栅线组12包括间隔设置的第一栅极线121和第二栅极线122。

90.第一薄膜晶体管15和第二薄膜晶体管16的栅极分别连接第一栅极线121和第二栅极线122。

91.可以理解为,第一连接部21和第二连接部22分别沿第一栅极线121和第二栅极线122的轮廓设置。这种结构使得第一连接部21和第二连接部22各处与栅极线形成的侧向电容相同。

92.在一些实施例中,第一连接部21与其相邻的栅线组12之间的间距,等于第二连接部22与其相邻的栅线组12之间的间距。

93.这种结构使得第一连接部21与第二连接部22与栅线组12之间的侧向电容相同,无

差异化,弥补栅线组12与薄膜晶体管源极之间形成的存储电容cgs的差异,进一步提高像素存储电容的均一性,进一步确保本行栅极线关断时,对第一子像素电极171和第二子像素电极172的电压拉动相同,漏电后的灰阶差异减小,大大避免了摇头纹的出现。

94.在一些实施例中,第一薄膜晶体管15的源极152通过第四连接部23连接第一子像素电极171。

95.如图2所示,第四连接部23的长度小于第二连接部22的长度,所以本实施例中,第一连接部21的设置也是对第四连接部23的补偿。

96.在一些实施例中,阵列基板还包括:覆盖栅线组12、公共线13、数据线14和像素电极的第一绝缘层192,以及设置于第一绝缘层192上方的公共电极18。其中,公共电极18在衬底基板11上的正投影至少覆盖部分公共线13和部分像素电极在衬底基板11上的正投影。

97.在一些实施例中,如图3所示,第四连接部23包括与第一子像素电极171连接的第一子连接件231,以及连接第一子连接件231和第一薄膜晶体管15的源极152的第二子连接件232。

98.在一些实施例中,第一子连接件231在衬底基板11上的正投影与第一薄膜晶体管15的源极152在衬底基板11上的正投影部分重叠。

99.在一些实施例中,第二子连接件232与公共电极18位于同一层。

100.在一些实施例中,第二子连接件232与公共电极18的材料可以均包括氧化铟锡(indium tin oxide,ito),即2ito层。

101.在一些实施例中,第一子连接件231与像素电极位于同一层,两者的材料可以均包括氧化铟锡(indium tin oxide,ito),即1ito层。

102.在一些实施例中,当第一连接部21与栅线组12位于同一层时,第一连接部21可以与第一子连接件231直接接触,如图5所示。

103.所以,在一些实施例中,第一子连接件231与第一薄膜晶体管15的源极152正在不同的层,中间通过第二绝缘层191隔离,可以通过贯穿第二绝缘层191的接触孔实现第一子连接件231与第一薄膜晶体管15的源极152的相互连接。

104.但是上述连接方式,在二者的线宽较小时,接触孔工艺的限制导致二者的接触电阻较大,接触效果较差,所以在一些实施例中,如图5所示,第二子连接件232还可以分别通过第一接触孔(图中未标注)和第二接触孔(图中未标注)与第一子连接件231和第一薄膜晶体管15的源极152连接。第二子连接件232可以减小第一子连接件231和第一薄膜晶体管15的源极152连接之间的接触电阻,保证良好的接触效果。

105.第二薄膜晶体管16位置处,第二薄膜晶体管16的源极162与第二连接部22之间的连接方式与第一薄膜晶体管15相同,此处不再赘述。

106.在一些实施例中,公共电极18在衬底基板11上的正投影还覆盖公共线13在衬底基板11上的正投影。

107.在一些实施例中,如图2所示,公共电极18通过至少一个贯穿第一绝缘层192的第三接触孔cnt与公共线13连接。这种结构可以增加公共线13的电阻,降低压降,避免信号的延迟,提高了显示面板的显示效果。

108.在一些实施例中,第三接触孔cnt在衬底基板11上的正投影落入栅线组12中第一栅极线121和第二栅极线122在衬底基板11上的正投影之间,以降低公共线13与栅线组12之

间的电容。

109.在一些实施例中,第三接触孔cnt位置处,公共线13和公共电极18的线宽均比较大,以保证良好的接触效果。

110.在一些实施例中,公共电极18在衬底基板11上的正投影与像素电极在衬底基板11上的正投影的重合部分呈条纹状(两条纹之间形成狭缝slit),条纹状的公共电极18与其下方的像素电极之间提供不同的压差而形成电场,在条纹状电极的边缘会具有一最强的边缘垂直电场存在,因此液晶在此会趋向于和垂直方向电场平行排列,增强光线的穿透效果,可提高液晶层的显示效果。

111.在一些实施例中,公共电极18在衬底基板11上的正投影不覆盖数据线14、第一薄膜晶体管15和第二薄膜晶体管16。

112.在一些实施例中,位于同一列的像素电极对应显示同一种颜色,按照r、g、b的顺序排列,且在任意时刻(任意帧中)任意相邻两条数据线14上的数据信号的电平相反,即第一数据线141和第二数据线142上的数据信号的电平相反。

113.在一些实施例中,分别位于公共线13两侧的两列像素电极中,同一行的两个像素电极均为第一子像素电极171或第二子像素电极172,且分别位于数据线14两侧的两列像素电极中,同一行的两个像素电极分别为第一子像素电极171和第二子像素电极172。

114.由此,在显示过程中,各个像素电极对应的子像素的极性分布示意图如图6所示,在显示画面时,沿行方向或列方向排列的子像素在同一帧中被施加相反极性的数据信号,可以使各子像素在同一帧显示画面中亮度分布均匀,从而尽量避免摇头纹的出现。

115.在一些实施例中,数据线14和公共线13包括在衬底基板11上方依次叠层设置的第一导电层(图中未示出)和第二导电层(图中未示出)。

116.其中,第一导电层在衬底基板11上的正投影至少覆盖部分第二导电层在衬底基板11上的正投影。

117.第一导电层与第一薄膜晶体管15的有源层151和第二薄膜晶体管16的有源层161位于同一层,第二导电层与第一薄膜晶体管15和第二薄膜晶体管16的源极152、162和漏极153、163位于同一层。这种结构可以增加数据线14的电阻,降低压降,避免信号的延迟。

118.在一些实施例中,第一导电层与第一薄膜晶体管15的有源层151和第二薄膜晶体管16的有源层161的材料相同。

119.在一些实施例中,第二导电层与第一薄膜晶体管15和第二薄膜晶体管16的源极152、162和漏极153、163的材料相同。

120.在一些实施例中,栅线组12包括在衬底基板11上方依次叠层设置的第三导电层和第四导电层;其中,第三导电层在衬底基板11上的正投影至少覆盖部分第四导电层在衬底基板11上的正投影;第三导电层与像素电极位于同一层。这种结构可以增加栅线组12的电阻,降低压降,避免信号的延迟。

121.在一些实施例中,第三导电层与像素电极的材料相同。

122.在一些实施例中,如图4所示,当第一连接部21与栅线组12的材料相同时,第一连接部21包括在衬底基板11上方依次叠层设置的第三导电层211和第四导电层212,这也使得在一些实施例中,第一连接部21可以直接与第四连接部23的第一子连接件231接触,如图3所示。

123.在一些实施例中,如图7和8所示,公共线13包括沿列方向延伸的总线131,以及与总线131连接并向相邻的第一薄膜晶体管15延伸的第三连接部132;其中,第三连接部132与相邻的第一连接部21绝缘交叠。

124.第三连接部132在衬底基板11上的正投影至少覆盖部分第一连接部21在衬底基板上的正投影。

125.这种结构同样可以补偿第一子像素电极171的存储电容cst,但是这种结构,在工艺过程中,可能由于工艺或设备的误差,导致第三连接部132与第一连接部21之间产生偏差,存储电容无法确保,也无法弥补第一连接部21与栅线组12之间的侧向电容差异,从而导致在本行上栅极开始关闭时,对两个像素电极的电压拉动不同,使得漏电后产生灰阶差异,可能仍会呈现出少量的摇头纹。

126.在一些实施例中,第一连接部21连接对应的第一子像素电极171,第一像素电极通过第一薄膜晶体管15连接数据线14,所以第一连接部21仍连接数据信号。即第一连接部21的一端连接第一子像素电极171,一端延伸至第三连接部132下方。

127.本技术实施例中,上述阵列基板可以用于超级多维场开关(advanced super dimension switch,ads)显示模式的显示面板中。

128.本技术中通过在与数据线的连接距离较短的第一薄膜晶体管的一侧设置第一连接部,与公共线绝缘交叠,大大增加了对应像素的存储电容cst,提高了像素存储电容的均一性,确保了本行栅极线关断时,对各个像素电极的电压拉动相同,漏电后的灰阶差异减小,大大避免了摇头纹的出现。

129.本技术实施例还提供了一种显示装置,显示装置包括上述的阵列基板。

130.在一些实施例中,显示装置为显示面板,显示面板包括上述的显示基板及玻璃盖板。

131.在一些实施例中,显示装置可包括显示面板及壳体,显示面板与壳体相连接,例如,显示面板嵌入到壳体内。显示装置例如可以为手机、平板电脑、电视机、笔记本电脑、数码相框、导航仪等任何具有显示功能的设备。

132.以上仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。虽然本技术所公开的实施方式如上,但的内容只是为了便于理解本技术而采用的实施方式,并非用以限定本技术。任何本技术所属技术领域内的技术人员,在不脱离本技术所公开的精神和范围的前提下,可以在实施的形式上及细节上作任何的修改与变化,但本技术的保护范围,仍须以所附的权利要求书所界定的范围为准。