1.本发明涉及半导体技术领域,特别是涉及一种套刻测量方法、半导体器件的制作方法。

背景技术:

2.光刻是通过对准、曝光等一系列步骤将光罩上的掩膜图形转移到晶圆上的工艺过程,在半导体芯片的制造过程中,要通过多层光刻工艺才能完成整个制造过程。随着半导体制造技术的发展以及集成电路设计及制造的发展,光刻成像技术随之发展,半导体器件的特征尺寸也不断缩小。为了实现良好的产品性能以及高产率,如何控制当层光刻图形(晶圆上的图形)与前层光刻图形(晶圆上的图形)的位置对准,以满足套刻精度(overlay)的要求是多层光刻工艺中至关重要的步骤,套刻精度是指晶圆的层与层的光刻图形的位置对准误差,套刻精度将会严重影响产品的良率和性能,且提高光刻胶的套刻精度,也是决定最小单元尺寸的关键。故而,现有的半导体器件在制作过程中,有必要提供一种套刻量测方法来提高套刻测量精度。

技术实现要素:

3.本发明的目的在于提供一种套刻量测方法、光刻方法,以解决跨层的套刻量测问题。

4.为达到上述目的,本发明提供一种套刻量测方法,包括:

5.在第一层光刻工艺中采用光罩在晶圆上形成阵列布置的多个第一标记;

6.在第二层光刻工艺中采用所述光罩在所述晶圆上形成阵列布置的多个第二标记;且所述第一标记与相对应的所述第二标记相互嵌套;

7.获取相互嵌套的所述第一标记和所述第二标记的偏差值,以得到第一层和第二层的对准偏差。

8.可选的,所述第一标记与相对应的所述第二标记的嵌套方式包括:

9.位于所述第一层的第一标记与位于所述第二层的相应的第二标记左右相互嵌套;其中,所述光罩包括左右对称设置的第一套刻标记和第二套刻标记。

10.可选的,所述第一标记与相对应的所述第二标记的嵌套方式包括:

11.位于所述第一层的第一标记与位于所述第二层的相应的第二标记上下相互嵌套;其中,所述光罩包括上下对称设置的第一套刻标记和第二套刻标记。

12.可选的,所述获取相互嵌套的所述第一标记和所述第二标记的偏差值的步骤包括:

13.按照预设规律获取多个相互嵌套的第一标记和第二标记的偏差值。

14.可选的,所述第一层光刻工艺还包括:采用所述光罩在所述晶圆上形成阵列布置的多个第一单元阵列,且每个所述第一单元阵列的一侧边对应形成有所述第一标记;

15.所述第二层光刻工艺还包括:采用所述光罩在所述晶圆上形成阵列布置的多个第

二单元阵列,且每个所述第二单元阵列的一侧边对应形成有所述第二标记;

16.其中,所述光罩还包括单元阵列图形,且所述单元阵列图形的左右两侧对称设置第一套刻标记和第二套刻标记,和/或所述单元阵列图形的上下两侧对称设置第一套刻标记和第二套刻标记。

17.可选的,所述第一套刻标记的中心线至所述单元阵列图形的距离,与所述第二套刻标记的中心线至所述单元阵列图形的距离相同。

18.可选的,所述第一套刻标记和所第二套刻标记布置在所述单元阵列图形四周的切割道内。

19.可选的,所述第一标记和所第二标记的形状包括方形,所述第二标记嵌套在相对应的所述第一标记内。

20.可选的,所述第一标记和所第二标记包括呈扇状排列的条型阵列,所述第一标记和所述第二标记均包括四个套刻区域,其中,

21.所述第一标记内每一套刻区域均包括平行设置的多个第一条形部,且相邻两个所述套刻区域中的多个第一条形部的延伸方向相互垂直;

22.所述第二标记内每一套刻区域均包括平行设置的多个第二条形部,且相邻两个所述套刻区域中的多个第二条形部的延伸方向相互垂直;

23.所述第二标记嵌套在相对应的所述第一标记内,且每一所述套刻区域内,平行设置的多个第一条形部和平行设置的多个第二条形部的延伸方向相同,且多个所述第一条形部和多个所述第二条形部在所述延伸方向上一一对应设置。

24.本发明还提供一种半导体器件的制作方法,采用如上所述的任一项所述的套刻量测方法进行第一层和第二层对准的量测。

25.综上,本发明提供一种套刻量测方法、半导体器件的制作方法,包括:采用同一光罩,在第一层光刻工艺中在晶圆上形成阵列布置的多个第一标记,在第二层光刻工艺中在所述晶圆上形成阵列布置的多个第二标记,且所述第一标记与相对应的所述第二标记相互嵌套,通过获取相互嵌套的所述第一标记和所述第二标记的偏差值,以得到第一层和第二层的对准偏差。本发明针对第一层和第二层的结构相同的刻蚀工艺,采用相同的光罩,并分别在第一层和第二层刻蚀工艺依次在晶圆上形成多个第一标记和多个第二标记,利用第一标记和第二标记的相互嵌套,实现第一层和第二层对准的量测,解决了跨层的套刻量测问题,实现跨层光刻使用同一光罩,降低了光罩成本。

附图说明

26.图1为一光罩的结构示意图;

27.图2为第一层光刻工艺和第二层光刻工艺在晶圆上形成套刻量测标记的过程的结构示意图;

28.图3为本发明实施例一提供的套刻量测方法的流程图;

29.图4为本发明实施例一提供的套刻量测方法中使用的光罩的结构示意图;

30.图5a为本发明实施例一提供的套刻量测方法中遮挡第二套刻标记进行第一层光刻工艺的光罩的结构示意图;

31.图5b为本发明实施例一提供的套刻量测方法中遮挡第一套刻标记进行第二层光

刻工艺的光罩的结构示意图;

32.图6为本发明实施例一提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺在晶圆上形成套刻量测标记的过程的结构示意图;

33.图7为本发明实施例一提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺后在晶圆上形成的套刻量测标记的结构示意图;

34.图8为本发明实施例一提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺后在晶圆上形成的另一种套刻量测标记的结构示意图;

35.图9为本发明实施例二提供的套刻量测方法中使用的光罩的结构示意图;

36.图10为本发明实施例二提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺在晶圆上形成套刻量测标记的过程的结构示意图;

37.图11为本发明实施例三提供的套刻量测方法中使用的光罩的结构示意图;

38.图12为本发明实施例三提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺在晶圆上形成套刻量测标记的过程的结构示意图;

39.图13为本发明实施例三提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺后在晶圆上形成的套刻量测标记的结构示意图。

40.其中,附图标记为:

41.10、100、300-光罩;11、110、110

′

、310-单元阵列图形;12、120、120

′

、320-套刻标记;120a、120a

′

、320a-第一套刻标记;120b、120b

′

、320b-第二套刻标记;

42.20、200-晶圆;21、210、210

′

、310、410-单元阵列;22、220、220

′

、420-套刻量测标记;220a、220a

′

、420a-第一标记;220b、220b

′

、420b-第二标记;21a、210a、210a

′

、410a-第一层光刻图案;21b、210b、210b

′

、410b-第二层光刻图案;22a-第一层套刻量测标记;22b-第二层套刻量测标记。

具体实施方式

43.以下结合附图和具体实施例对本发明的套刻量测方法、半导体器件的制作方法作进一步详细说明。根据下面的说明和附图,本发明的优点和特征将更清楚,然而,需说明的是,本发明技术方案的构思可按照多种不同的形式实施,并不局限于在此阐述的特定实施例。附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

44.在说明书中的术语“第一”“第二”等用于在类似要素之间进行区分,且未必是用于描述特定次序或时间顺序。要理解,在适当情况下,如此使用的这些术语可替换,例如可使得本文所述的本发明实施例能够以不同于本文所述的或所示的其他顺序来操作。类似的,如果本文所述的方法包括一系列步骤,且本文所呈现的这些步骤的顺序并非必须是可执行这些步骤的唯一顺序,且一些所述的步骤可被省略和/或一些本文未描述的其他步骤可被添加到该方法。若某附图中的构件与其他附图中的构件相同,虽然在所有附图中都可轻易辨认出这些构件,但为了使附图的说明更为清楚,本说明书不会将所有相同构件的标号标于每一图中。

45.此外还应该认识到,此处描述的术语仅仅用来描述特定实施例,而不是用来限制本发明的范围。必须注意的是,此处的以及所附权利要求中使用的单数形式“一个”和“一

种”包括复数基准,除非上下文明确表示相反意思。例如,对“一个步骤”或“一个装置”的引述意味着对一个或多个步骤或装置的引述,并且可能包括次级步骤以及次级装置。应该以最广义的含义来理解使用的所有连词。以及,词语“或”应该被理解为具有逻辑“或”的定义,而不是逻辑“异或”的定义,除非上下文明确表示相反意思。此外,本发明实施例中的方法和/或设备的实现可包括手动、自动或组合地执行所选任务。

46.如背景技术所述,随着半导体制造技术的进一步发展,对套刻精度也有了更高的要求,因而,如何实现对套刻精度的监测也变得越来越重要,而现有为了实现对套刻精度的监测,一般在第一层光罩上具有套刻标记,在第二层光罩上具有配套的套刻标记,采用第一层光罩进行第一层光刻工艺,在晶圆上形成第一层套刻标记图形,采用第二层光罩进行第二层光刻工艺,在晶圆上对应形成第二层套刻标记图形,通过测量第一层套刻标记图形与第二层套刻标记图形之间的位置差异获得套刻精度,或者通过测量第一层套刻标记图形与第二层套刻标记图形之间的衍射光差异获得套刻精度。

47.在目前普遍使用3d存储时,如3d nand、3d pcm,会遇到上下两层之间的结构完全一样的情况,但使用的却是两块光罩(mask),这样会增加光罩的成本,为此,会想到让这种在上下层结构相同的层去使用相同的光罩。而在跨层使用同一块光罩时,如果直接曝光,那么前后两层的套刻标记也就会同时做出来,当第一层和第二层需要直接对准时,直接曝光是无法做套刻量测的。

48.举例来说,图1为一光罩的结构示意图,图2为第一层光刻工艺和第二层光刻工艺后晶圆上套刻量测标记的结构示意图。如图1和图2所示,所述光罩10包括单元阵列图形11和套刻标记12,在上下层结构相同的跨层使用该光罩,在进行第一层光刻工艺时,在晶圆20上形成多个第一层光刻图案21a和多个第一层套刻量测标记22a,接着,在进行第二层光刻工艺时,在晶圆20上形成多个第二层光刻图案21b和多个第二层套刻量测标记22b,进而在晶圆20上形成单元阵列21及套刻量测标记22,其中,套刻量测标记22中,第一层套刻量测标记22a和第二层套刻量测标记22b重叠。由于第一层刻蚀工艺中第一层套刻量测标记22a的inner mark和outer mark同步形成,第二层刻蚀工艺中第二层套刻量测标记22b也是同样的做出了inner mark和outer mark,当前后两层需要直接对准时,跨层采用同一光罩此工艺采用无法满足。

49.针对上述第一层套刻量测标记22a和第二层套刻量测标记22b重叠而无法进行第一层和第二层的对准量测的问题,发明人研究发现,在第一层第一次使用光罩曝光时只做出套刻标记的outer mark,而在第二层第二次使用光罩曝光时只做出套刻标记的inner mark,从而可以做overlay量测,解决了跨层使用同mask时解决overlay量测。

50.实施例一

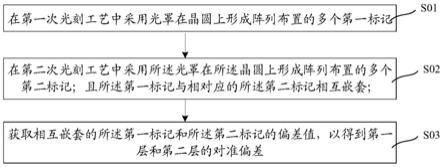

51.本实施例提供一种套刻量测方法及一种半导体器件的制作方法。图3为本本实施例提供的一种套刻量测方法的流程图。如图3所示,本实施例提供的套刻量测方法包括:

52.s01:在第一层光刻工艺中采用光罩在晶圆上形成阵列布置的多个第一标记;

53.s02:在第二层光刻工艺中采用所述光罩在所述晶圆上形成阵列布置的多个第二标记;且所述第一标记与相对应的所述第二标记相互嵌套;

54.s03:获取相互嵌套的所述第一标记和所述第二标记的偏差值,以得到第一层和第二层的对准偏差。

55.图4、图5a及图5b为本实施提供的套刻量测方法中使用的光罩的结构示意图,图6为本实施提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺在晶圆上套刻量测标记的过程的结构示意图。以下参考图3、图4、图5a及图5b及图6详细介绍本实施例提供的套刻量测方法。

56.首先,参考图4所示,提供光罩100,所述光罩100包括单元阵列图形110和位于所述单元阵列图形110外围的套刻标记120,其中,所述套刻标记120包括第一套刻标记120a和第二套刻标记120b。

57.本实施例中的套刻的量测方法可以采用基于图形的套刻测量技术(image-based overlay,ibo)进行套刻的测量,相应的套刻标记的形状可以采用基于图形的套刻测量技术所采用的套刻标记的形状。所述套刻标记120可以设置在所述单元阵列图形110四周切割道内的任意位置。在本实施例中,所述光罩包括左右对称设置的第一套刻标记120a和第二套刻标记120b,所述第一套刻标记120a和所第二套刻标记120b分别位于所述单元阵列图形110左右相对的两侧的切割道内,所述第一套刻标记120a的中心线至所述单元阵列图形110的距离,与所述第二套刻标记120b的中心线至所述单元阵列图形110的距离相同。

58.所述第一套刻标记120a和所第二套刻标记120b的形状包括方形,如图4所示,所述第一套刻标记120a和第二套刻标记120b为设置在单元阵列图形110左右两侧的方形结构,所述第一套刻标记120a(outer mark)的尺寸大于所述第二套刻标记120b(inner mark)的尺寸。作为优选,所述单元阵列图形110的一侧设置两个方形结构的第一套刻标记120a,相对的另一侧设置两个方形结构的第二套刻标记120b,一侧第一套刻标记120a的中心线和另一侧的所第二套刻标记120b的中心线与单元阵列图形110之间的距离相等,进一步的,一侧所述第一套刻标记120a的中心线和另一侧的所第二套刻标记120b的中心线关于所述单元阵列图形110对称。

59.接着,参考图5a、图5b及图6所示,采用所述光罩100进行第一层光刻工艺,在晶圆200上形成多个第一标记220a;采用所述光罩100进行第二层光刻工艺,在所述晶圆200上形成多个第二标记220b。

60.如图6所示,采用所述光罩100进行第一层光刻工艺,在晶圆200上形成多个第一层光刻图案210a和多个第一标记220a,接着,采用所述光罩100进行第二层光刻工艺,在所述晶圆200上形成多个第二层光刻图案210b和第二标记220b,进而在第一层光刻工艺和第二层光刻工艺后,将光罩图案转移至晶圆200,所述单元阵列图形110转移至晶圆200形成单元阵列210,所述套刻标记120转移至晶圆200形成套刻量测标记220,所述套刻量测标记220包括相互嵌套的第一标记220a和第二标记220b。

61.进一步的,采用所述光罩100进行第一层光刻工艺时,可以采用遮挡所述套刻标记120中的第二套刻标记120b,保留单元阵列图形110和第一套刻标记120a,进而在晶圆200上形成多个第一层光刻图案210a和多个第一标记220a;采用所述光罩100进行第二层光刻工艺时,可以采用遮挡所述套刻标记120中的第一套刻标记120a,保留单元阵列图形110和第二套刻标记120b,进而在晶圆200上形成多个第二层光刻图案210b和多个第二标记220b。示例性的,可以通过光刻机rema功能进行所述第一套刻标记120a或所述第二套刻标记120b的遮挡,以在晶圆200上形成相应的套刻测量标记220。

62.本实施例中,由于所述第一层光刻工艺和所述第二层光刻工艺采用同一光罩,即

所述第一层光刻工艺和所述第二层光刻工艺采用相同的单元阵列图形110,且由于单元阵列图形110一侧所述第一套刻标记120a的中心和另一侧的所第二套刻标记120b的中心关于所述单元阵列图形110对称,在所述第一层工艺和所述第二层工艺分别通过所述第一套刻标记120a和第二套刻标记120b先后在所述晶圆200上形成的第一标记220a和第二标记220b则相互嵌套,所述第二标记220b嵌套在所述第一标记220a内。且由于所述第一套刻标记120a和第二套刻标记120b关于所述单元阵列图形110左右对称设置,在晶圆200上相邻的两个所述单元阵列210中,位于所述第一层的第一标记220a与位于所述第二层的第二标记220b左右相互嵌套。具体的,如图6所示,晶圆200上的一单元阵列210对应的第二标记220b嵌套在相邻的另一单元阵列210b对应的第一标记220a内。即完成第一层光刻工艺和第二层光刻工艺后,在晶圆200上形成框图中套框图(frame in frame)的ibo套刻量测标记。

63.在本发明一些实施例中,所述第一套刻标记120a和所述第二套刻标记120b也均可以是柱状结构,先后完成第一层光刻工艺和第二层光刻工艺后,在晶圆上,相邻的两个所述单元阵列中,一单元阵列的第二标记220b嵌套在另一单元阵列的第一标记220a的内部,形成柱图中套柱图(bar in bar)的ibo套刻量测标记,如图8所示。

64.应当理解的,对于采用其他形状设置的套刻标记,控制第一套刻标记和第二套刻标记在光罩的相对位置关系,经过第一层光刻工艺和第二层光刻工艺后,以在晶圆上形成的具有嵌套关系的第一标记和第二标记,以形成套刻测量标记满足套刻量测的要求。

65.接着,获取相互嵌套的所述第一标记220a和所述第二标记220b的偏差值,以得到第一层和第二层的对准偏差。具体的,如图6所示,第一层光刻工艺和第二层光刻工艺后,所述晶圆200上第二标记220b嵌套在第一标记220a的内,通过测量第一标记220a(对应第一套刻标记)与第二标记220b(对应第二套刻标记)之间的位置偏差以获得套刻精度。可以按照预设规律获取多个相互嵌套的第一标记220a和第二标记220b的偏差值,完成第一层和第二层对准的量测。图7为晶圆上套刻量测标记220的结构示意图,示例性的如图7所示,测量第一层和第二层沿x方向的偏差δx,δx=(w1-w2)/2,测量第一层和第二层沿y方向的偏差δy,δx=(w3-w4)/2,通过第一层和第二层沿x方向的偏差δx和第一层和第二层沿y方向的偏差δy,完成第一层和第二层对准测量。

66.本实施例中,针对第一层和第二层的结构相同的刻蚀工艺,在第一层和第二层刻蚀工艺中采用相同的光罩,并将光罩中的不同的套刻标记分别在第一层和第二层刻蚀工艺依次形成在晶圆上,进而在晶圆上形成嵌套的套刻量测标记,解决了跨层的套刻量测问题,实现跨层光刻使用同一光罩,降低了光罩成本。

67.相应的,本实施例还提供一种半导体器件的制作方法,包括:第一层光刻工艺和第二层光刻工艺使用同一光罩,且采用如上述套刻量测方法进行第一层和第二层对准的量测。在3d存储器制造工艺中,如3d nand、3d pcm,上下两层之间的结构完全一样,采用上述半导体器件的制作方法,可以在上下层结构相同的层去使用相同的光罩,跨层使用同一块光罩,降低光罩成本的同时,可以完成套刻量测,保证工艺质量。

68.实施例二

69.本实施例提供一种套刻的量测方法,与实施例一的区别在于本实施例中光罩上的第一套刻标记和第二套刻标记关于所述单元阵列图形上下对称设置,在晶圆上形成的相邻的两个所述单元阵列中,位于所述第一层的第一标记与位于所述第二层的第二标记上下相

互嵌套。

70.图9为本实施提供的套刻量测方法中使用的光罩的结构示意图,图10为本实施提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺后晶圆上套刻量测标记的结构示意图。具体的,参考图9和图10所示,首先,提供光罩100,所述光罩100包括单元阵列图形110

′

和位于所述单元阵列图形110

′

外围的套刻标记120

′

,其中,所述套刻标记120

′

包括第一套刻标记120a

′

和第二套刻标记120b

′

,且所述第一套刻标记120a

′

和第二套刻标记120b

′

关于所述单元阵列图形110

′

上下对称设置。

71.示例性的,所述第一套刻标记120a

′

和第二套刻标记120b

′

的形状均为方形,所述第一套刻标记120a

′

(outer mark)的尺寸大于所述第二套刻标记120b

′

(inner mark)的尺寸。所述单元阵列图形110

′

的一侧设置两个框形结构的第一套刻标记120a

′

,相对的另一侧设置两个框形结构的第二套刻标记120b

′

,且一侧所述第一套刻标记120a

′

的中心和另一侧的所第二套刻标记120b

′

的中心关于所述单元阵列图形110

′

对称。

72.接着,参考图10所示,采用所述光罩100进行第一层光刻工艺,在晶圆200上形成多个第一标记220a

′

;采用所述光罩100进行第二层光刻工艺,在晶圆200上形成多个第二标记220b

′

,在第一层光刻工艺和第二层光刻工艺后,将光罩100图案转移至晶圆200,所述单元阵列图形110

′

转移至晶圆200

′

形成单元阵列210

′

,所述套刻标记120

′

转移至晶圆200形成套刻量测标记220

′

,所述套刻量测标记220

′

包括相互嵌套的第一标记220a

′

和第二标记220b

′

。

73.在先后完成所述第一层光刻工艺和所述第二层光刻工艺后,所述第一标记220a

′

和第二标记220b

′

上下嵌套,所述晶圆200上所述第二标记220b

′

嵌套在所述第一标记220a

′

内。如图10所示,晶圆200上的一单元阵列210

′

对应的第二标记220b

′

嵌套在相邻的另一单元阵列210b

′

对应的第一标记220a

′

的内部,即在晶圆200上形成框图中套框图(frame in frame)的ibo套刻量测标记。

74.接着,获取相互嵌套的所述第一标记220a

′

和所述第二标记220b

′

的偏差值,以得到第一层和第二层的对准偏差。如图10所示,可以按照预设规律获取多个相互嵌套的第一标记220a

′

和第二标记220b

′

的偏差值,完成第一层和第二层对准的量测。具体方法可参照实施例一。

75.需要说明的是,在本发明其他实施例中,光罩上的第一套刻标记和第二套刻标记除上述关于单元阵列图形的左右对称设置和上下对称设置,也可以采用其他形式的位置布置,例如第一套刻标记和第二套刻标记分别位于单元阵列图形对角位置;另外,同一所述单元阵列图形可以对应一组左右设置的第一套刻标记和第二套刻标记,或对应一组上下设置的第一套刻标记和第二套刻标记,也可以同时对应一组左右设置的第一套刻标记和第二套刻标记和一组上下设置的第一套刻标记和第二套刻标记。即关于第一套刻标记和第二套刻标记的位置设置,只需要在通过控制第一套刻标记和第二套刻标记在光罩的相对位置关系,在经过第一层光刻工艺和第二层光刻工艺后,能在晶圆上形成的具有嵌套关系的第一标记和第二标记,满足对第一层和第二层对准的套刻量测的要求即可。

76.实施例三

77.本实施例提供一种套刻的量测方法,与实施例一的区别在于光罩上的第一套刻标记和所述第二套刻标记均为呈扇状排列的条纹阵列,且第一套刻标记和所述第二套刻标记

的位置分布不同。

78.图11为本实施提供的套刻量测方法中使用的光罩的结构示意图,图12为本实施提供的套刻量测方法中第一层光刻工艺和第二层光刻工艺后晶圆上套刻量测标记的结构示意图。具体的,参考图11和图12所示,首先,提供光罩300,所述光罩300包括单元阵列图形310和套刻标记320,所述套刻标记320包括第一套刻标记320a和第二套刻标记320b,其中,所述第一套刻标记320a和所述第二套刻标记320b均为呈扇状排列的条形阵列,所述第二套刻标记320b镶嵌在所述第一套刻标记320a内,且所述第二套刻标记320b的对称中心和所述第一套刻标记320a的对称中心重合。

79.具体的,所述第一套刻标记320a和所述第二套刻标记320b均为中心对称图形,所述第一套刻标记320a和所述第二套刻标记320b均包括四个标记区域,所述第一套刻标记320a内每一套刻区域均包括平行设置的多个第一条形部,相邻两个所述标记区域中的多个第一条形部相互垂直;所述第二套刻标记320b内每一标记区域均包括多个平行设置的多个第二条形部,相邻两个所述标记区域中的多个第二条形部相互垂直;每一标记区域内,平行设置的多个第一条形部和平行设置的多个第二条形部的延伸方向相同,且多个第一条形部和多个第二条形部在所述延伸方向上一一对应设置。

80.本实施例中,所述第一套刻标记320a和所述第二套刻标记320b位于所述单元阵列图形310的同一侧,优选的,所述第一套刻标记320a和所述第二套刻标记320b的数量均为两个,且分别位于所述单元阵列图形310的同一侧的不同位置,且两个所述第一套刻标记320a的中心、两个所述第二套刻标记320b的中心到所述单元阵列图形310的距离相等。

81.需要说明的是,上述第一套刻标记和第二套刻标记图形均为中心对称图形仅仅是本发明适用所有实施例中的一种,对此本发明不做具体限制,且第一套刻标记和第二套刻标记的数量,及不同数量的排布方式可以根据第一层刻蚀和第二层刻蚀工艺具体设置,对此本发明也不做具体限制。

82.接着,采用所述光罩300进行第一层光刻工艺,在晶圆200上形成多个第一层光刻图案410a和多个第一标记420a,采用所述光罩300进行第二层光刻工艺,在所述晶圆200上形成多个第二层光刻图案410b和多个第二标记420b,进而在第一层光刻工艺和第二层光刻工艺后,将光罩图案转移至晶圆200,所述单元阵列图形310转移至所述晶圆200形成单元阵列410,所述套刻标记320转移至晶圆200形成套刻量测标记420。如图12所示,完成第一层光刻工艺和第二层光刻工艺后,相邻的两个所述单元阵列410中,一单元阵列的所述第二标记420b嵌套在另一单元阵列的所述第一标记420a内。

83.所述第一标记420a和所第二标记420b包括呈扇状排列的条型阵列,所述第一标记420a和所述第二标记420b均包括四个套刻区域,分别与光罩上第一套刻标记320a和第二套刻标记320b的四个标记区域相对应,其中,所述第一标记420a内每一套刻区域均包括平行设置的多个第一条形部,且相邻两个所述套刻区域中的多个第一条形部的延伸方向相互垂直;所述第二标记420b内每一套刻区域均包括平行设置的多个第二条形部,且相邻两个所述套刻区域中的多个第二条形部的延伸方向相互垂直;所述第二标记420b嵌套在相对应的所述第一标记420a内,且每一所述套刻区域内,平行设置的多个第一条形部和平行设置的多个第二条形部的延伸方向相同,且多个所述第一条形部和多个所述第二条形部在所述延伸方向上一一对应设置。

84.接着,获取相互嵌套的所述第一标记420a和所述第二标记420b的偏差值,以得到第一层和第二层的对准偏差。具体可以按照预设规律获取多个相互嵌套的第一标记420a和第二标记420b的偏差值,完成第一层和第二层对准的量测。图13为晶圆上套刻量测标记420的结构示意图,参考图11、图12及图13所示,经第一层刻蚀工艺和第二层刻蚀工艺后,所述第二套刻标记320b对应的第二标记420b嵌套在所述第一套刻标记320a对应的第一标记420a内,在第一层刻蚀工艺和第二层刻蚀工艺对准的情况下,所述第二标记420b的对称中心应该与所述第一标记420a的对称中心重合,因此,可以通过测量所述第二标记420b和所述第一标记420a的对称中心的偏差来测量第一层和第二层的对准偏差。

85.本实施例中通过将所述第二标记420b和所述第一标记420a的对称中心的偏差转化成沿x方向、y方向的偏差来测量第一层和第二层的对准偏差。具体的的,测量第一层和第二层沿x方向的偏差δx,δx=(d3-d4)/2,测量第一层和第二层沿y方向的偏差δy,δy=(d1-d2)/2,其中,所述d1、d2、d3及d4为第一标记420a和第二标记420b中相邻套刻区域之间相互垂直的的条形部之间的距离。采用上述方法获取第一层和第二层沿x方向的偏差δx和第一层和第二层沿y方向的偏差δy,完成第一层和第二层对准测量。当然,在本发明其他实施例中,也可采用其他方法计算相互嵌套的第一标记420a和第二标记420b的偏差值,在此不作具体限定。

86.综上所述,本发明提供一种套刻量测方法、半导体器件的制作方法,包括:采用同一光罩,在第一层光刻工艺中在晶圆上形成阵列布置的多个第一标记,在后层光刻工艺中在所述晶圆上形成阵列布置的多个第二标记,且所述第一标记与相对应的所述第二标记相互嵌套,,通过获取相互嵌套的所述第一标记和所述第二标记的偏差值,以得到第一层和第二层的对准偏差。本发明针对第一层和第二层的结构相同的刻蚀工艺,在第一层和第二层刻蚀工艺中采用相同的光罩,并分别在第一层和第二层刻蚀工艺依次在晶圆上形成多个第一标记和多个第二标记,利用第一标记和第二标记的相互嵌套,实现第一层和第二层对准的量测,解决了跨层的套刻量测问题,实现跨层光刻使用同一光罩,降低了光罩成本。

87.需要说明的是,本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

88.还需要说明的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围。