1.本技术涉及显示技术领域,尤其涉及一种显示装置。

背景技术:

2.随着显示技术日趋成熟,现有薄膜电晶体液晶显示装置(thin film transistor liquid crystal display,tft-lcd)已能实现窄边框和超高分辨率(如8k),并且朝着大尺寸、高分辨率、高对比等更高性能发展。

3.然而,现有的超高分辨率的显示装置容易出现多种显示不良缺陷,如黑白水平线、画面串扰、残影等。这些不良缺陷严重影响显示装置的显示质量和客户的观视体验。黑白水平线是由于超高分辨率的显示装置的面内负载较大而产生。并且,随着显示装置的尺寸增加,面内负载也随之增大。具体来说,对于设计在显示装置的面内(如显示面板的显示面)的逐行驱动的时钟信号线,位于不同行的时钟信号线之间存在明显的负载差异。显示装置通过控制位于面内的多个像素发光以呈现出所需画面。时钟信号线之间的负载差异会导致像素充电后的电位存在差异,进而导致不同像素行之间存在亮度差异。因此,显示出的画面中存在密集的黑白水平线。

4.目前,针对上述缺陷的一种改善方案为,通过改变制造工艺来调整时钟信号线之间的面内负载差异。然而,这种改善方案无法完全解决时钟信号线之间的负载差异,并且容易导致产品的良率降低、产能下降和效益降低等问题。

5.有鉴于此,有必要提出一种显示装置,以解决现有技术中存在的问题。

技术实现要素:

6.为解决上述现有技术的问题,本技术的目的在于提供一种显示装置,其能改善显示装置显示出非预期的黑白水平线的问题。

7.为达成上述目的,本技术提供一种显示装置,包括:电路板,配置为输出时钟信号,其中所述时钟信号为高电平和低电平交替出现的信号;显示面板,与所述电路板连接,包含显示区和非显示区;多条时钟信号线,配置为传递所述时钟信号,其中每一所述时钟信号线从所述电路板延伸至所述显示面板的所述非显示区;多个接地电阻,设置在所述电路板,其中每一所述接地电阻与对应的所述时钟信号线连接,配置为降低所述时钟信号的所述高电平的电压值;栅极驱动器,设置在所述显示面板的所述非显示区,且与所述时钟信号线连接,配置为根据降低所述高电平的电压值的所述时钟信号产生栅极信号;以及栅极线,设置在所述显示面板的所述显示区,且与所述栅极驱动器连接,配置为传递所述栅极信号。

8.在一些实施例中,所述多条时钟信号线从所述显示面板的所述显示区朝所述非显示区的方向依序排列,并且与其中两条所述时钟信号线对应连接的两个所述接地电阻的数值不同。

9.在一些实施例中,所述显示装置包含依序排列的第m条时钟信号线、第m-1条时钟信号线和第m-2条时钟信号线;以及与所述第m条时钟信号线连接的所述接地电阻的数值为

r(m),与所述第m-1条时钟信号线连接的所述接地电阻的数值为r(m-1),以及与所述第m-2条时钟信号线连接的所述接地电阻的数值为r(m-2),其中r(m)《r(m-1)《r(m-2)或r(m)》r(m-1)》r(m-2)。

10.在一些实施例中,所述显示装置包含相邻的第k条时钟信号线和第k-1条时钟信号线;以及与所述第k条时钟信号线连接的所述接地电阻的数值为r(k),与所述第k-1条时钟信号线连接的所述接地电阻的数值为r(k-1),其中r(k)=r(k-1)。

11.在一些实施例中,所述显示装置还包括多个匹配电阻,设置在所述电路板,以及每一所述匹配电阻与对应的所述时钟信号线连接。

12.在一些实施例中,每一所述时钟信号线包含第一段和与所述第一段连接的第二段,所述第一段设置在所述电路板,所述第二段设置在所述显示面板的所述非显示区,以及每一所述接地电阻与对应的所述时钟信号线的所述第一段连接。

13.在一些实施例中,所述电路板包含第一电路板和第二电路板;每一所述时钟信号线的所述第一段包含第一子段和第二子段,所述第一子段设置在所述第一电路板,以及所述第二子段设置在所述第二电路板;每一所述时钟信号线的所述第二段包含第三子段和第四子段,分别设置在所述显示面板的相对两侧;所述栅极驱动器包含第一栅极驱动器和第二栅极驱动器,所述第一栅极驱动器与所述第三子段连接,所述第二栅极驱动器与所述第四子段连接,所述第一栅极驱动器和所述第二栅极驱动器分别与所述栅极线的相对两端连接;每一所述接地电阻包含第一接地电阻和第二接地电阻,所述第一接地电阻设置在所述第一电路板并且与对应的所述时钟信号线的所述第一子段连接,所述第二接地电阻设置在所述第二电路板并且与对应的所述时钟信号线的所述第二子段连接。

14.在一些实施例中,与同一所述时钟信号线连接的所述第一接地电阻和所述第二接地电阻的数值相同。

15.在一些实施例中,与同一所述时钟信号线连接的所述第一接地电阻和所述第二接地电阻的数值不同。

16.在一些实施例中,同一所述时钟信号线与所述第一接地电阻、所述第二接地电阻的rc电路和对应的所述栅极线的rc电路构成电子回路。

17.相较于先前技术,本技术通过在显示装置的电路板上设置与时钟信号线连接的接地电阻和匹配电阻,可优化时钟信号线的电路设计和消除时钟信号线的负载差异,进而解决显示画面出现非预期的黑白水平线的问题,大幅提升产品的良率和产品质量。

附图说明

18.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

19.图1显示根据本技术的实施例的显示装置的示意图。

20.图2显示图1的显示装置的局部电路框图。

21.图3显示图1的显示装置的显示面板的非显示区的布线区的示意图。

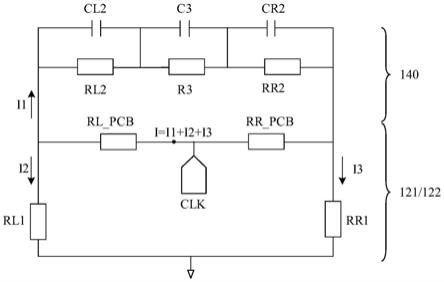

22.图4显示根据本技术的实施例的时钟信号线的电路图。

23.图5显示根据本技术的实施例的时钟信号的波形图。

具体实施方式

24.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

25.请参照图1,其显示根据本技术的实施例的显示装置10的示意图。显示装置10包括处理器100、时序控制器110、第一电路板121、第二电路板122、柔性电路板130、显示面板140、第一栅极驱动器151、第二栅极驱动器152和源极驱动器。时序控制器110与处理器100连接。第一电路板121和第二电路板122与时序控制器110连接,并且分别通过对应的柔性电路板130与显示面板140连接。显示面板140包括显示区141和围绕显示区141的非显示区142。第一栅极驱动器151和第二栅极驱动器152分别设置在显示面板140的相对两侧,并且设置在显示面板140的外周围143与显示区141之间的非显示区142。源极驱动器可集成在第一电路板121和第二电路板122中,集成在柔性电路板130中,或者是设置在显示面板140的非显示区142,不局限于此。显示面板140的显示区141包括多条栅极线gl、多条数据线和多个像素,其中每一栅极线gl可驱动至少一行像素。第一栅极驱动器151和第二栅极驱动器152与栅极线gl对应连接,并且分别连接栅极线gl的相对两端。源极驱动器与数据线连接。

26.请参照图1和图2,图2显示图1的显示装置的局部电路框图。显示装置10还包含电压产生单元101和时序产生单元123。在本实施例中,电压产生单元101可设置在处理器100中,以及时序产生单元123可设置在第一电路板121和第二电路板122中。时序产生单元123与电压产生单元101和时序控制器110连接。时序产生单元123通过多条信号线与第一栅极驱动器151和第二栅极驱动器152连接,如时钟信号线clk、扫描开始信号线、扫描顺序控制信号线等。在本实施例中,第一电路板121的时序产生单元123与第一栅极驱动器151之间的信号线包含12条时钟信号线(clk1至clk12),以及第二电路板122的时序产生单元123与第二栅极驱动器152之间的信号线也包含12条时钟信号线(clk1至clk12)。应当理解的是,在其他实施例中可采用其他数量的时钟信号线clk,不局限于此。

27.如图1和图2所示,在本实施例中,处理器100输出图像信号、使能信号、垂直同步信号、水平同步信号和时钟信号等驱动信号。时序控制器110从处理器100接收上述驱动信号。时序控制器110基于驱动信号产生数据控制信号。源极驱动器根据数据控制信号产生数据信号,并输出至对应的数据线。再者,电压产生单元101提供电压至时序产生单元123。时序控制器110基于驱动信号产生控制信号。时序产生单元123根据电压和控制信号产生包含时钟信号的栅极控制信号,并且控制对应的时钟信号线clk传递所述时钟信号至第一栅极驱动器151和/或第二栅极驱动器152。第一栅极驱动器151和第二栅极驱动器152根据栅极控制信号产生栅极信号,并输出至对应的栅极线。显示面板140中的像素响应于数据信号和栅极信号显示图像。

28.如图1所示,显示面板140的非显示区142包含第一布线区1421和第二布线区1422。第一布线区1421位于第一栅极驱动器151与显示面板140的外周围143之间,以及第二布线区1422位于第二栅极驱动器152与显示面板140的外周围143之间。

29.如图1和图2所示,每一时钟信号线clk从电路板121/122延伸至显示面板140的非显示区142的布线区1421/1422。具体来说,同一时钟信号线clk(如第一时钟信号线clk1)包

含设置在电路板121/122的第一段和设置在显示面板140的第二段。由于本实施例是采用双栅极驱动技术,因此同一时钟信号线clk会在显示装置10的相对两侧延伸。

30.如图1所示,在一条时钟信号线clk中,时钟信号线clk的第一段包含位于第一电路板121的第一子段161和位于第二电路板122的第二子段162。时钟信号线clk的第二段包含位于第一布线区1421的第三子段163和位于第二布线区1422的第四子段164。第一子段161和第二子段162接收基于时序控制器110的同一信号而产生的时钟信号,即第一子段161和第二子段162用于传递相同的时钟信号。第一子段161与第三子段163连接,以及第二子段162与第四子段164连接。第三子段163与第一栅极驱动器151连接,以及第四子段164与第二栅极驱动器152连接。第一栅极驱动器151和第二栅极驱动器152基于相同的时钟信号控制同一条栅极线gl。

31.应当注意的是,不同的时钟信号线clk之间会因为面板制程差异而导致不同的时钟信号线clk之间存在负载差异,进而影响传递至显示面板140的时钟信号。其次,电路板121/122的制程差异、显示面板140和电路板121/122的设计差异(如结构设计、走线布局设计等)也会导致上述负载差异的问题。举例来说,请参照图3,其显示图1的显示装置的显示面板140的非显示区142的布线区1421/1422的示意图。在显示面板140的布线区1421/1422中,从显示面板140的非显示区142(或外周围143)朝显示区141的方向包含依序排列的彩膜基板的公共电极线cf_com、dbs(data line bm less)公共电极线dbs、第十二时钟信号线clk12至第一时钟信号线clk1、第二下拉电路控制信号线lc2、第一下拉电路控制信号线lc1和基准电位线vss。在显示面板140内,每一时钟信号线clk的时钟信号会与周围信号线相互耦合。由于布线设计的影响,不同的时钟信号会产生不同的耦合量,进而使得不同时钟信号线之间具有不同的负载。为了改善时钟信号线之间的负载差异,本技术的显示装置还包含与时钟信号线连接的接地电阻,具体说明如下。

32.如图1和图2所示,接地电阻r设置在电路板121/122,且与对应的时钟信号线clk的第一段连接。具体来说,请参照图4,其显示根据本技术的实施例的时钟信号线的电路图。与同一条时钟信号线clk连接的接地电阻1包含第一接地电阻rl1和第二接地电阻rr1。第一接地电阻rl1设置在第一电路板121上,且与时钟信号线clk的第一子段161连接。第二接地电阻rr1设置在第二电路板122上,且与时钟信号线clk的第二子段162连接。时钟信号线clk的第三子段163由于制程差异和走线布局影响而具有第一负载(包含第一负载电阻rl2和第一负载电容cl2)。同理,时钟信号线clk的第四子段164具有第二负载(包含第二负载电阻rr2和第二负载电容cr2)。此外,基于同一时钟信号而驱动的栅极线gl也具有第三负载(包含第三负载电阻r3和第三负载电容c3)。同一条时钟信号线clk与第一接地电阻rl1、第二接地电阻rr1的rc电路和对应的栅极线gl的rc电路构成电子回路。时钟信号线clk在显示面板上的电流为i1,时钟信号线clk在第一电路板121上的电流为i2,时钟信号线clk在第二电路板122上的电流为i3。时钟信号线clk的总电流i为i1+i2+i3。

33.在本实施例中,通过设置接地电阻r,可增强时钟信号的电压降,使得时钟信号的高电平的电压值降低。具体来说,请参照图5,其显示根据本技术的实施例的时钟信号的波形图。时序产生单元123根据接收电压和时序控制器110的控制信号产生初始时钟信号w1,通过一对应的时钟信号线clk传递初始时钟信号w1。初始时钟信号w1为高电平vgh和低电平vgl交替出现的信号。与时钟信号线clk连接的接地电阻r可降低时钟信号的高电平的电压

值,进而获得调整后的时钟信号w2。具体来说,通过接地电阻r可使得电路的总电阻减小,并且使总电流i增大,使得时钟信号在电路板上的压降增大,进而降低输入到显示面板上的时钟信号的高电平的电压值。在一些实施例中,初始时钟信号w1的高电平vgh与调整后的时钟信号w2的高电平vgh’的差值δv约为0.375v。根据馈通(feed through)效应,当第n行的栅极线导通,第n-1行的栅极线关闭。此时,第n-1行的像素电极会因寄生电容影响而降低驱动电压,进而使得第n-1行的像素的亮度变暗。在本技术中,通过设置接地电阻r可减少因馈通效应而导致的驱动电压下降,进而使对应暗区像素的亮度提高。因此,消除了因时钟信号线clk之间负载差异所造成的黑白水平线的问题,从而提升画面质量。

34.在本技术中,接地电阻r设置在电路板121/122上,而不是设置在显示面板140的布线区1421/1422。因此,可避免接地电阻r占用显示面板140的布线空间,以及避免接地电阻r增加显示面板140的负载。

35.应当注意的是,接地电阻r的数值根据与其连接的时钟信号线的布线位置决定。在本实施例中,考量不同时钟信号线的布线位置差异,接地电阻r的数值介于1至500千欧姆(kω)之间。应当理解的是,若接地电阻r的数值超出此范围会影响面板正常显示,或对消除黑白水平线的作用不大。若电阻的数值太大(如大于500kω),由于电路原理使得对于显示面板内的时钟信号影响较小,进而无消除黑白水平线的改善效果。另一方面,若电阻的数值太小(如小于1kω),由于电路原理使得显示面板内的时钟信号线存在短路,从而影响显示。

36.在一些实施例中,显示装置10包含从显示面板140的非显示区142朝显示区141的方向依序排列的多条时钟信号线。通过将与其中至少两条时钟信号线对应连接的两个接地电阻的数值设计为不同,可消除因时钟信号线布线位置不同而造成的负载差异。举例来说,显示装置10包含从显示面板140的外周围143朝显示区141的方向依序排列的n条时钟信号线。与第n条时钟信号线连接的接地电阻的数值为r(n),以及与第一条时钟信号线连接的接地电阻的数值为r(1),其中r(n)≠r(1)。

37.在一些实施例中,显示装置10包含从显示面板140的外周围143朝显示区141的方向依序排列的n条时钟信号线。由于相邻近的时钟信号线之间的布线差异较小,因此将与其中两相邻的时钟信号线对应连接的两相邻的接地电阻r的数值设计为相同。举例来说,显示装置10包含相邻的第k条时钟信号线和第k-1条时钟信号线,其中n≤k《1。与第k条时钟信号线连接的接地电阻的数值为r(k),与第k-1条时钟信号线连接的接地电阻的数值为r(k-1),其中r(k)=r(k-1)。应当注意的是,r(k)≠r(n)或r(k)≠r(1)。通过部分的接地电阻r采用相同电阻值的设计,有利于降低电路板121/122的制造复杂性、提高良率和产能。

38.在一些实施例中,显示装置10包含从显示面板140的外周围143朝显示区141的方向依序排列的多条时钟信号线。由于不同的时钟信号线之间存在不同的制程差异,且不同的时钟信号也会因级传关系而存在不同的耦合值,因此与多条时钟信号线对应连接的接地电阻r的数值可设计为全部或大部分不同。响应于接地电阻r的数值不同,该些数值可采有序或无序的设置方案,其中有序的方案包含渐变。具体来说,该些接地电阻r的数值从外周围朝显示区的方向渐变,如渐增或渐减。举例来说,显示装置10包含从显示面板140的外周围143朝显示区141的方向依序排列的n条时钟信号线,其中包含依序排列的第m条时钟信号线、第m-1条时钟信号线和第m-2条时钟信号线,且n≤m《1。与第m条时钟信号线连接的接地电阻的数值为r(m),与第m-1条时钟信号线连接的接地电阻的数值为r(m-1),以及与第m-2

条时钟信号线连接的接地电阻的数值为r(m-2),其中r(m)《r(m-1)《r(m-2)或r(m)》r(m-1)》r(m-2)。在一些实施例中,该些接地电阻r的数值为等差数列,公差为1kω,如与第一时钟信号线clk1至第十二时钟信号线clk12连接的接地电阻r分别为1kω、2kω、3kω、4kω、5kω、6kω、7kω、8kω、9kω、10kω、11kω、12kω。全部或大部分的接地电阻r采用不同电阻值的设计,对于改善黑白水平线的效果更佳。

39.在一些实施例中,与同一条时钟信号线clk连接的接地电阻r的第一接地电阻rl1和第二接地电阻rr1可设计为相同(如上述的接地电阻r的数值等于第一接地电阻rl1,且等于第二接地电阻rr1)。通过将与同一条时钟信号线clk连接的第一接地电阻rl1和第二接地电阻rr1采用相同电阻值的设计,有利于降低制造复杂性、提高良率和产能。

40.在一些实施例中,考量同一条时钟信号线clk在显示装置10(包含电路板和显示面板)的两侧可能存在制程差异和布线差异,与同一条时钟信号线clk连接的接地电阻r的第一接地电阻rl1和第二接地电阻rr1可设计为不同。藉此设计,可有效地改善同一条时钟信号线在显示装置的不同侧的负载差异。

41.如图2和图4所示,显示装置10还包括多个匹配电阻r_pcb,设置在电路板121/122,且每一匹配电阻r_pcb与对应的时钟信号线clk的第一段串联连接。具体来说,与同一条时钟信号线clk连接的匹配电阻r_pcb包含第一匹配电阻rl_pcb和第二匹配电阻rr_pcb。第一匹配电阻rl_pcb设置在第一电路板121上,且与时钟信号线clk的第一子段161连接。第二匹配电阻rr_pcb设置在第二电路板122上,且与时钟信号线clk的第二子段162连接。

42.在显示装置10的制造过程中,先设置接地电阻r,接着再设置匹配电阻r_pcb。具体来说,对显示装置10进行点灯测试以确认画面质量。若画面中出现的水平密集线则对所有时钟信号进行量测,以确定时钟信号线之间的负载差异。接着,通过上述的接地电阻r的设计方案,降低对应时钟信号的高电平的电压值。因此,消除了时钟信号线之间的负载差异,从而消除黑白水平线和提高显示质量。接着,对电路板121/122上的时钟信号线clk的电阻进行基准定位以确认造成暗线的时钟信号线clk,并且对该时钟信号线clk进行串电阻匹配。因此,通过匹配电阻r_pcb的设置可进一步解决黑白水平线的问题。由上可知,通过接地电阻r和匹配电阻r_pcb的设置,可有效减小不同的时钟信号线clk的时钟信号对像素行的充电差异,进而提升各像素行的亮度均一性,消除黑白水平线的问题以及提升画面质量。

43.上述实施例是以采用双栅极驱动技术的显示装置进行说明。应当理解的是,本技术的方案也适用于采用单栅极驱动技术的显示装置,其原理以及接地电阻与匹配电阻的设计方案皆相似于上述双栅极驱动技术的显示装置,在此不加以赘述。

44.综上所述,本技术通过在显示装置的电路板上设置与时钟信号线连接的接地电阻和匹配电阻,可优化时钟信号线的电路设计和消除时钟信号线的负载差异,进而解决显示画面出现非预期的黑白水平线的问题,大幅提升产品的良率和产品质量。

45.以上对本技术实施例所提供的一种显示装置进行了详细介绍。本文中应用了具体实施例对本技术的原理及实施方式进行了阐述。以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想。本领域的普通技术人员应当理解,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。