1.本技术涉及一种驱动电路,特别涉及一种发光元件的驱动电路及其驱动方法。

背景技术:

2.现今的显示器已广泛的使用驱动电流提供驱动电流以驱动发光元件,一般来说,驱动电流是由驱动晶体管的栅极端的电位所决定,若栅极端的电位因漏电流而偏移,则可能导致画面失真。因此,如何降低栅极端的电位因漏电流造成的偏移导致画面失真本领域重要的议题。

技术实现要素:

3.本揭示文件提供一种驱动电路,驱动电路包含发光元件、第一p型晶体管、第二p型晶体管、第三p型晶体管、第一n型晶体管、第二n型晶体管、第三n型晶体管以及第四n型晶体管。第一p型晶体管用以提供驱动电流给发光元件以驱动发光元件发光。第二p型晶体管,其第一端电性耦接系统高电压端,其第二端电性耦接第一p型晶体管的第一端。第三p型晶体管,其第一端电性耦接第一p型晶体管的第二端,其第二端电性耦接发光元件的第一端,其中发光元件的第二端电性耦接系统低电压端。第一n型晶体管,其第一端电性耦接第三p型晶体管的第一端,其第二端电性耦接系统低电压端。第二n型晶体管,其第一端电性耦接第一p型晶体管的第一端,其第二端电性耦接第一p型晶体管的栅极端。第三n型晶体管,其第一端用以接收数据信号,其第二端电性耦接第一p型晶体管的第一端。第四n型晶体管,其第一端电性耦接第一p型晶体管的第二端,其第二端电性耦接第一p型晶体管的栅极端。

4.本揭示文件提供一种驱动方法,用以驱动所述驱动电路。驱动方法依序操作在预充电期间、重置期间、补偿及写入期间以及发光期间,驱动方法包含下列步骤在预充电期间,藉由导通第二p型晶体管以及第二n型晶体管,使系统高电压端的电位经由第二p型晶体管以及第二n型晶体管传送至第一p型晶体管的栅极端。在重置期间,藉由导通第一n型晶体管、第二n型晶体管以及第四n型晶体管,使系统低电压端的电位经由第一n型晶体管、第四n型晶体管以及第二n型晶体管传送至第一p型晶体管的第一端以导通第一p型晶体管。在补偿及写入期间,导通第三n型晶体管以及第四n型晶体管,使数据信号经由第三n型晶体管、第一p型晶体管以及第四n型晶体管传送至第一p型晶体管的栅极端。在发光期间,导通第二p型晶体管以及第三p型晶体管,使第一p型电体提供驱动电流给发光二极管以驱动发光二极管发光。

5.综上所述,本揭示文件将驱动电流的电流路径之外的晶体管以n型晶体管实施,藉以由于漏电造成显示画面失真的问题。

附图说明

6.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,附图的说明如下:

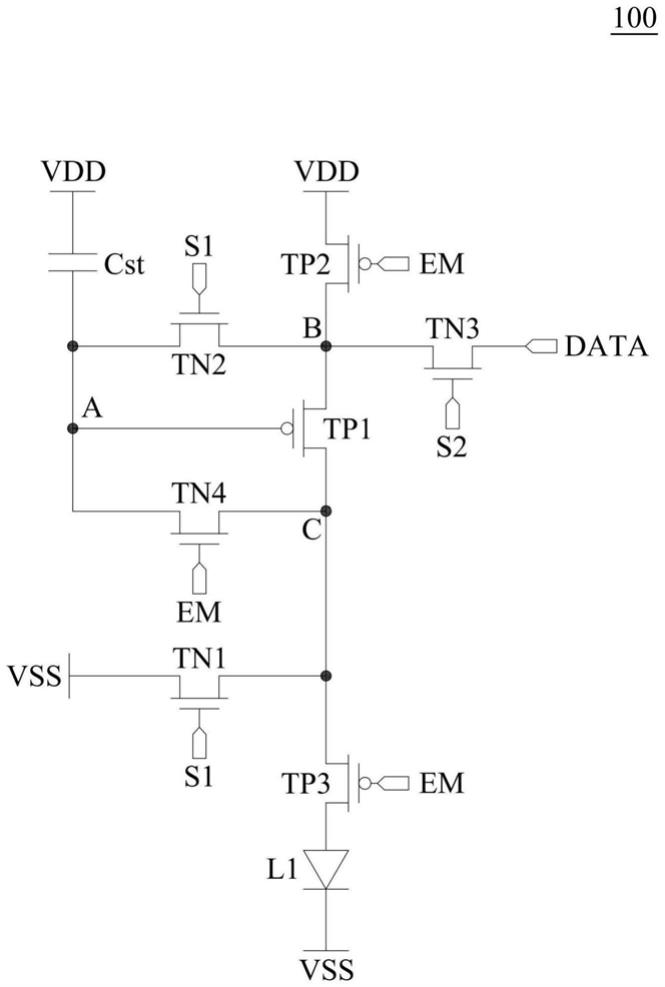

7.图1本公开的实施例的驱动电路的电路架构图。

8.图2为图1中的驱动电路的控制信号的时序图。

9.图3a图1中的驱动电路的在重置期间中的电路状态图。

10.图3b图1中的驱动电路的在补偿及写入期间中的电路状态图。

11.图3c图1中的驱动电路的在发光期间中的电路状态图。

12.图3d为图1中的像素驱动电路在发光期间中的电路状态图。

13.图4a为图1中节点a的电压示意图。

14.图4b为图1中电流误差示意图。

15.【符号说明】

16.为使本公开的上述和其他目的、特征、优点与实施例能更明显易懂,所附符号的说明如下:

17.100:驱动电路

18.l1:发光元件

19.tp1:第一p型晶体管

20.tp2:第二p型晶体管

21.tp3:第三p型晶体管

22.tn1:第一n型晶体管

23.tn2:第二n型晶体管

24.tn3:第三n型晶体管

25.tn4:第四n型晶体管

26.cst:电容

27.a,b,c:节点

28.vdd:系统高电压端

29.vss:系统低电压端

30.s1:第一控制信号

31.s2:第二控制信号

32.em:第三控制信号

33.data:数据信号

34.id:驱动电流

35.p1:预充电期间

36.p2:重置期间

37.p3:补偿及写入期间

38.p4:发光期间

39.vh:高逻辑电平

40.vl:低逻辑电平

具体实施方式

41.下列举实施例配合所附图示做详细说明,但所提供的实施例并非用以限制本公开所涵盖的范围,而结构运作的描述非用以限制其执行顺序,任何由元件重新组合的结构,所

产生具有均等功效的装置,皆为本公开所涵盖的范围。另外,图示仅以说明为目的,并未依照原尺寸作图。为使便于理解,下述说明中相同元件或相似元件将以相同的符号标示来说明。

42.在全篇说明书与权利要求书所使用的用词(terms),除有特别注明除外,通常具有每个用词使用在此领域中、在此公开的内容中与特殊内容中的平常意义。

43.此外,在本文中所使用的用词“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指“包含但不限于”。此外,本文中所使用的“和/或”,包含相关列举项目中一或多个项目的任意一个以及其所有组合。

44.在本文中,当一元件被称为“耦接”或“连接”时,可指“电性耦接”或“电性连接”。“耦接”或“连接”也可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。

45.图1本公开的实施例的驱动电路100的电路架构图。如图1所示,驱动电路100包含发光元件l1、第一p型晶体管tp1、第二p型晶体管tp2、第三p型晶体管tp3、第一n型晶体管tn1、第二n型晶体管tn2、第三n型晶体管tn3、第四n型晶体管tn4以及电容cst。

46.第一p型晶体管tp1用以在发光期间提供驱动电流给发光元件l1以驱动发光元件l1发光。第二p型晶体管tp2以及第三p型晶体管tp3用以防止大电压劣化。第一n型晶体管tn1用以在预充电期间重置发光元件l1的第一端的电位。第二n型晶体管tn2用以在预充电期间将系统高电压端vdd的电位传送该第一p型晶体管以关断第一p型晶体管。第三n型晶体管tn3以及第四n型晶体管tn4用以在补偿及写入期间将数据信号data写传送至第一p型晶体管的栅极端直到第一p型晶体管截止,藉以进行第一p型晶体管的临界电压的补偿。

47.第一p型晶体管tp1、第二p型晶体管tp2、第三p型晶体管tp3以及发光元件l1电性耦接在系统高电压端vdd以及系统低电压端vss之间。也就是说,在流经发光元件l1的驱动电流的电流路径上,皆是由p型晶体管实施,从而增加晶体管的电流驱动能力,以减少所需的驱动电压的范围,进而达到低功耗的效果。进一步而言,前述p型晶体管可以是低温多晶硅薄膜晶体管。

48.前述这些晶体管分别具有第一端、第二端以及栅极端(gate)。当其中一晶体管的第一端为漏极端(源极端)时,该晶体管的第二端则为源极端(漏极端)。另外,前述电容亦分别具有第一端以及第二端。

49.详细而言,第二p型晶体管tp2的第一端电性耦接系统高电压端vdd,第二p型晶体管tp2的第二端电性耦接第一p型晶体管tp1的第一端,第二p型晶体管tp2的栅极端用以接收第三控制信号em。

50.第一p型晶体管tp1的第一端电性耦接第二p型晶体管tp2的第二端,第一p型晶体管tp1的第二端电性耦接第三p型晶体管tp3的第一端,第一p型晶体管tp1的栅极端电性耦接节点a。节点b在第一p型晶体管tp1的第一端以及第二p型晶体管tp2的第二端的连接处。节点c在第一p型晶体管tp1的第二端以及发光元件l1的第一端的连接处。

51.第三p型晶体管tp3的第一端电性耦接第一p型晶体管tp1的第二端,第三p型晶体管tp3的第二端电性耦接发光元件l1的第一端,第三p型晶体管tp3的栅极端用以接收第三控制信号em。发光元件l1的第一端电性耦接第三p型晶体管tp3的第二端,发光元件l1的第

二端电性耦接系统低电压端vss。

52.流经发光元件l1的驱动电流的大小与第一p型晶体管tp1的栅极端的电位正相关,一般来说,数据电压将会写入(或影响)栅极端的电位以决定驱动电流的大小,在显示周期中若第一p型晶体管tp1的栅极端存在漏电路径,使得栅极端电位因漏电而偏移,将可能造成显示器的画面闪烁。为了防止第一p型晶体管tp1的栅极端所在之处(节点a)漏电而造成显示器的画面闪烁,在本揭示文件中,驱动电路100在驱动电流的电流路径之外的路径上的晶体管皆以n型晶体管实施。前述n型晶体管(如第一n型晶体管tn1、第二n型晶体管tn2、第三n型晶体管tn3以及第四n型晶体管tn4)可以是铟镓锌氧化物薄膜晶体管。相较于低温多晶硅薄膜晶体管,铟镓锌氧化物薄膜晶体管在关断时的漏电较小,因此第一p型晶体管tp1的栅极端电位较不易因周围其他晶体管的漏电流所影响,可以维持在稳定的电位,因此在低画面更新频率的显示器中,驱动电路100可以有效改善节点a漏电造成画面失真的问题。

53.详细而言,第一n型晶体管tn1的第一端电性耦接第一p型晶体管tp1的第二端,第一n型晶体管tn1的第二端电性耦接系统低电压端vss,第一n型晶体管tp1的栅极端用以接收第一控制信号。

54.第二n型晶体管tn2的第一端电性耦接第一p型晶体管tp1的第一端,第二n型晶体管tn2的第二端电性耦接第一p型晶体管tp1的栅极端,第二n型晶体管tn2的栅极端用以接收第一控制信号s1。第三n型晶体管tn3的第一端用以接收数据信号data,第三n型晶体管tn3的第二端电性耦接第一p型晶体管tp1的第一端,第三n型晶体管tn3的栅极端用以接收第二控制信号s2。

55.第四n型晶体管tn4的第一端电性耦接第一p型晶体管tp1的第二端,第四n型晶体管tn4的第二端电性耦接第一p型晶体管tp1的栅极端,第四n型晶体管tn4的栅极端用以接收第三控制信号em。

56.电容cst的第一端电性耦接系统高电压端vdd,电容cst的第二端电性耦接第一p型晶体管tp1的栅极端,电容cst用以存储第一p型晶体管tp1的栅极端的电压。

57.图2为依据一实施例,图1中的像素驱动电路100的控制信号的时序图。如图2所示,在像素驱动电路100的控制时序中的一个显示周期可分为四个期间,其分别为预充电期间p1、重置期间p2、补偿及写入期间p3以及发光期间p4。需特别说明的是,图2中的这些期间的时间长度仅用以示例,并非用以限制本公开文件。

58.详细而言,第一控制信号s1在预充电期间p1以及重置期间p2具有第一逻辑电平(例如:高逻辑电平vh);第一控制信号s1在补偿及写入期间p3以及发光期间p4具有第二逻辑电平(例如:低逻辑电平vl)。第二控制信号s2在补偿及写入期间p3具有第一逻辑电平;第二控制信号s2在预充电期间p1、重置期间p2以及发光期间p4具有第二逻辑电平。第三控制信号em在重置期间p2以及补偿及写入期间p3具有第一逻辑电平;第三控制信号em在预充电期间p1以及发光期间p4具有第二逻辑电平。

59.为使像素驱动电路100的整体操作更加清楚易懂,以下请一并参考图1~3c。图3a为图1中的像素驱动电路100在预充电期间p1中的电路状态图。图3b为图1中的像素驱动电路100在重置期间p2中的电路状态图。图3c为图1中的像素驱动电路100在补偿及写入期间p3中的电路状态图。图3d为图1中的像素驱动电路100在发光期间p4中的电路状态图。

60.在预充电期间p1,由于第一控制信号s1具有高逻辑电平vh,因此第一n型晶体管

tn1以及第二n型晶体管tn2会导通。另一方面,由于第二控制信号s2以及第三控制信号em具有低逻辑电平vl,第二p型晶体管tp2以及第三p型晶体管tp3会导通,并且第四n型晶体管tn4以及第三n型晶体管tn3会关断。

61.详细而言,在预充电期间p1,系统高电压端vdd的电压vdd经由第二p型晶体管tp2以及第二n型晶体管tn2传送至第一p型晶体管tp1的栅极端(节点a),以将第一p型晶体管tp1的栅极端的电位上拉至电压vdd,使第一p型晶体管tp1官段。同时,系统低电压端vss的电压vss经由第一n型晶体管tn1以及第三p型晶体管tp3传送至发光元件l1的第一端,以重置发光元件l1的第一端的电位。此时,节点a以及节点b的电位实质上等于系统高电压端vdd的电位vdd,并且节点c的电位实质上等于系统低电压端的电位vss。

62.藉由第一n型晶体管tn1在预充电期间p1将系统低电压端vss的电压vss传送至发光元件l1的阳极端(第一端),使发光元件l1的阳极端的电位可以稳定在电压vss,从而提升画面对比度。

63.在重置期间p2,由于第一控制信号s1以及第三控制信号em具有高逻辑电平vh,因此第一n型晶体管tn1、该第二n型晶体管tn2以及第四n型晶体管tn4会导通,并且第二p型晶体管tp2以及第三p型晶体管tp3会关断。另一方面,由于第二控制信号s2具有低逻辑电平vl,第三n型晶体管tn3会关断。

64.详细而言,在重置期间p2,系统低电压端vss的电压vss经由第一n型晶体管tn1、第四n型晶体管tn4以及第二n型晶体管tn2传送至第一p型晶体管tp1的源极端(第一端),藉以重置第一p型晶体管tp1的源极端(第一端)以及栅极端的电位,并且使第一p型晶体管tp1导通。此时,节点a、b以及c的电位实质上等于系统低电压端vss的电压vss。

65.在补偿及写入期间p3,由于第二控制信号s2以及第三控制信号em具有高逻辑电平vh,因此第三n型晶体管tn3以及第四n型晶体管tn4会导通,并且第二p型晶体管tp2以及第三p型晶体管tp3会关断。另一方面,由于第一控制信号s1具有低逻辑电平vl,因此第一n型晶体管tn1以及第二n型晶体管tn2会关断。

66.详细而言,在补偿及写入期间p3,数据信号data的电压vdata经由第三n型晶体管、第一p型晶体管tp1以及第四n型晶体管tn4传送至第一p型晶体管tp1的栅极端,直到第一p型晶体管tp1截止。也就是说,当节点b(第一p型晶体管tp1的源极端)的电位比节点a(第一p型晶体管tp1的栅极端)的电位大一个第一p型晶体管tp1的临界电压的绝对值|vth|时,第一p型晶体管tp1截止。此时,节点a及c的电位实质上等于(vdata-|vth|),并且节点b的电位实质上等于vdata。

67.在发光期间p4,由于第一控制信号s1、第二控制信号s2以及第三控制信号em具有低逻辑电平vl,因此第二p型晶体管tp2以及第三p型晶体管tp3会导通,并且,第一n型晶体管tn1、第二n型晶体管tn2、第三n型晶体管tn3以及第四n型晶体管tn4会关断。

68.详细而言,由于第一n型晶体管tn1、第二n型晶体管tn2、第三n型晶体管tn3以及第四n型晶体管tn4关断,第一p型晶体管tp1的栅极端的电位仍维持在(vdata-|vth|)。并且系统高电压端vdd的电压vdd经由第二p型晶体管tp2传送至第一p型晶体管tp1的源极端。因此第一p型晶体管tp1的源极端以及栅极端的跨压(vsg)为[vdd-(vdata-|vth|)]。

[0069]

一般而言,p型晶体管所能提供的驱动电流遵守以下公式:id=k(vsg-|vth|)2。其中,k为相关于第二p型晶体管tp2的元件特性的一常数,|vth|为第二p型晶体管tp2的临界

电压的绝对值。

[0070]

将上述第二p型晶体管tp2的源极端与栅极端的跨压(vsg)代入驱动电流id的公式中,驱动电流id如下列计算:

[0071]

id=k(vsg-|vth|)2[0072]

id=k{[vdd-(vdata-|vth|)]-|vth|}2[0073]

id=k(vdd-vdata)2[0074]

在发光期间p4,第一p型晶体管tp1提供驱动电流id=k(vdd-vdata)2给发光元件l1,使发光元件l1依据驱动电流id的幅值发光。

[0075]

举例而言,若在补偿及写入期间p3,驱动电路100被写入的数据信号data的电压vdata较大,则由于前述驱动电流id的公式,发光元件l1在发光期间p4会依据较小的驱动电流id而在较低的亮度(灰阶);另一方面,若驱动电路100被写入的数据信号data的电压vdata较小,则由于前述驱动电流id的公式,发光元件l1在发光期间p4会依据较大的驱动电流id而在较高的亮度(灰阶)。

[0076]

请参阅图4a,图4a为图1中节点a的电压示意图。详细而言,图4a绘示当第一p型晶体管tp1的临界电压vth的变异(δvth)介于0.5~-0.5之中时节点a的电压波形图,其中节点a的电压以va表示。其中,横轴坐标为时间,单位是微秒(μs),纵轴坐标为电压,单位是伏特(v)。在图4a的实施例中是以相同数据信号data的电压vdata作示例。

[0077]

若第一p型晶体管tp1的临界电压vth的变异(δvth)在0.5伏特时,节点a在发光期间p4中的数值会在1.159伏特(v)。

[0078]

若第一p型晶体管tp1的临界电压vth的变异(δvth)在0伏特时,节点a在发光期间p4中的数值会在1.658伏特(v)。

[0079]

若第一p型晶体管tp1的临界电压vth的变异(δvth)在-0.5伏特时,节点a在发光期间p4中的数值会在2.157伏特(v)。

[0080]

可以从图4a看到依据不同的临界电压,节点a的电位会相应变化,也就是说驱动电路100确实可以补偿驱动电路100的临界电压。

[0081]

请参阅图4b,图4b为图1中电流误差模拟图。在图4b所示的实施例中,左斜线填满代表第一p型晶体管tp1的临界电压vth的变异(δvth)在-0.5伏特(v)时驱动电流id的电流误差率,右斜线填满代表第一p型晶体管tp1的临界电压vth的变异(δvth)在0.5伏特(v)时驱动电流id的电流误差率。其中,横轴坐标为电流误差率,单位是百分比(%),纵轴坐标为电压,单位是伏特(v)。值得一提的是,由于驱动电流id=k(vdd-vdata)2,vdata由小至大依序代表灰阶由高至低。如图4b所示,可以看到驱动电流id的电流误差率大致上在4.55%以下。如此,可以验证驱动电路100可有效补偿第一p型晶体管tp1的临界电压vth的变异。

[0082]

在一些常见的做法中,部分的显示器的驱动电路在低、中及高灰阶的驱动电流的电流误差率分别是9.42奈安培(na)、48.55奈安培(na)以及57.85奈安培(na)。在本揭示文件的驱动电路100的架构下,在低、中及高灰阶的驱动电流id的电流误差率分别是0.00奈安培(na)、0.02奈安培(na)以及-0.03奈安培(na),由此可知,在驱动电流id的电流路径外的晶体管皆是采用n型晶体管的驱动电路100的架构下,确实可以减少第一p型晶体管tp1的栅极端的漏电。如此,驱动电路100在低、中及高灰阶的驱动电流id的电流误差皆可明显降低,从而避免显示画面失真。

[0083]

综上所述,本揭示文件的驱动电路100具有补偿临界电压的能力,并且将驱动电流id的电流路径上的晶体管以p型晶体管实施,可以降低导通晶体管时所需的跨压,藉此增加驱动能力,并且将驱动电流id的电流路径之外的晶体管以n型晶体管实施,可以改善节点a因漏电造成显示画面失真的问题。进一步而言,第四n型晶体管tn4与第二p型晶体管tp2以及第三p型晶体管tp3共用第三控制信号em,藉以减少产生控制信号的电路的面积。

[0084]

虽然本公开已以实施方式公开如上,然其并非用以限定本公开,本领域技术人员在不脱离本公开的精神和范围内,当可作各种的更动与润饰,因此本公开的保护范围当视所附权利要求书界定范围为准。