1.本揭示内容涉及一种驱动技术,特别涉及一种驱动装置。

背景技术:

2.在驱动显示器中的像素电路时,会需要具有相同脉冲宽度的正向脉冲及负向脉冲,例如在数据写入期间具有致能电压电平的一脉冲及在数据写入期间具有禁能电压电平的一脉冲。上述脉冲使显示器能够在低频操作下逐列写入数据电压,并补偿薄膜晶体管的临界电压电平的变异,同时重置发光元件的电压以确保发光元件关闭来避免闪烁(flicker)现象的发生,来提升显示器的对比度。因此,要如何发展上述相关技术为本领域重要的课题。

技术实现要素:

3.本发明实施例包含一种驱动装置。驱动装置包括第一启动电路、第二启动电路及输出电路。第一启动电路用以在一第一期间依据一第一驱动信号调整一第一节点的一第一节点电压,且用以在一第二期间依据一第二驱动信号调整第一节点电压。第二启动电路用以在第一期间依据第一驱动信号调整一第二节点的一第二节点电压,且用以在第二期间依据第二驱动信号调整第二节点电压。输出电路用以输出一第三驱动信号,并用以在第一期间依据第一节点电压调整第三驱动信号至一第一电压电平,且用以在一第三期间依据第二节点电压调整第三驱动信号至一第二电压电平。第一期间、第二期间及第三期间依序排列。第一驱动信号在第一期间具有第二电压电平,且在第三期间具有第一电压电平。

4.本发明实施例包含一种显示器。显示器包括一显示装置及用以驱动显示装置的一驱动装置。驱动装置包括第一驱动单元、第二驱动单元及第三驱动单元。第一驱动单元用以依据一第一驱动信号产生一第二驱动信号。第二驱动单元用以依据第一驱动信号产生一第三驱动信号。第三驱动单元包括第一启动电路、第二启动电路及输出电路。第一启动电路用以在一第一期间依据第二驱动信号调整一第一节点的一第一节点电压,且用以在一第二期间依据第三驱动信号调整第一节点电压。第二启动电路用以在第一期间依据第二驱动信号调整一第二节点的一第二节点电压,且用以在第二期间依据第三驱动信号调整第二节点电压。输出电路用以输出一第四驱动信号,并用以在第一期间依据第一节点电压调整第四驱动信号至一第一电压电平,且用以在一第三期间依据第二节点电压调整第四驱动信号至一第二电压电平。第一期间、第二期间及第三期间依序排列。第二驱动信号在第一期间具有第二电压电平,且在第三期间具有第一电压电平。

附图说明

5.图1为根据本技术的一实施例所绘示的显示器的示意图。

6.图2为根据本技术的一实施例所绘示的驱动装置的示意图。

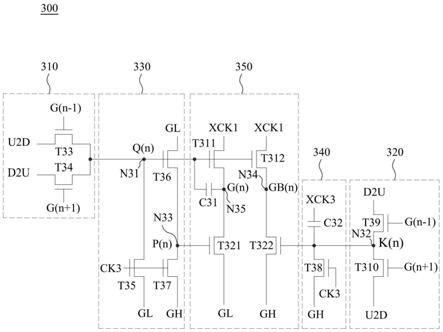

7.图3为根据本技术的一实施例所绘示的驱动装置中的驱动单元的电路图。

8.图4为根据本揭示内容的一实施例中的驱动单元进行驱动操作所绘示的时序图。

9.图5为根据本揭示内容的一实施例中的驱动单元进行驱动操作所绘示的时序图。

10.【符号说明】

11.100:显示器

12.110:显示装置

13.120、200:驱动装置

14.130:数据输入装置

15.140:发光控制装置

16.sl(0)~sl(n):驱动线

17.g(1)~g(n+1)、gb(1)~gb(n+1):驱动信号

18.dl(1)~dl(m):数据线

19.el(1)~el(n):发光线

20.dv(1)~dv(n)、112:像素驱动电路

21.ck1、ck2、ck3、ck4、xck1、xck2、xck3、xck4:时钟信号

22.du(1)~du(n+1)、300:驱动单元

23.st:起始信号

24.rst:重置信号

25.t33~t312、t321、t322:开关

26.c31、c32:电容

27.310、320:启动电路

28.330、340:稳压电路

29.350:输出电路

30.u2d、d2u、gl、gh:电压信号

31.vgh:禁能电压电平

32.vgl:致能电压电平

33.n31~n35:节点

34.p(n)、q(n)、k(n):节点电压

35.p41~p48、p51~p58:期间

[0036]vth33

、v

th37

、v

th38

、v

th310

、v

thltps

:临界电压电平

具体实施方式

[0037]

在本文中,当一元件被称为“连接”或“耦接”时,可指“电性连接”或“电性耦接”。“连接”或“耦接”也可用以表示二或多个元件间相互搭配操作或互动。此外,虽然本文中使用“第一”、“第二”、

…

等用语描述不同元件,该用语仅是用以区别以相同技术用语描述的元件或操作。除非上下文清楚指明,否则该用语并非特别指称或暗示次序或顺位,亦非用以限定本技术。

[0038]

除非另有定义,本文使用的所有术语(包括技术和科学术语)具有与本技术所属领域的普通技术人员通常理解的相同的含义。将进一步理解的是,诸如在通常使用的字典中定义的那些术语应当被解释为具有与它们在相关技术和本技术的上下文中的含义一致的

含义,并且将不被解释为理想化的或过度正式的意义,除非本文中明确地这样定义。

[0039]

这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括复数形式,包括“至少一个”。“或”表示“和/或”。如本文所使用的,术语“和/或”包括一个或多个相关所列项目的任何和所有组合。还应当理解,当在本说明书中使用时,术语“包括”和/或“包含”指定所述特征、区域、整体、步骤、操作、元件的存在和/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件和/或其组合的存在或添加。

[0040]

以下将以附图公开本技术的多个实施方式,为明确说明起见,许多实务上的细节将在以下叙述中一并说明。然而,应了解到,这些实务上的细节不应用以限制本技术。也就是说,在本揭示内容部分实施方式中,这些实务上的细节是非必要的。此外,为简化附图起见,一些已知惯用的结构与元件在附图中将以简单示意的方式绘示之。

[0041]

图1为根据本技术的一实施例所绘示的显示器100的示意图。请参照图1,显示器100包括显示装置110、驱动装置120、数据输入装置130与发光控制装置140。驱动装置120藉由驱动线sl(0)~sl(n)提供多个驱动信号,例如图2所示的驱动信号g(1)~g(n+1)及gb(1)~gb(n+1),至显示装置110。数据输入装置130藉由数据线dl(1)~dl(m)提供多个数据信号至显示装置110。发光控制装置140藉由发光线el(1)~el(n)提供多个发光信号至显示装置110。其中n与m皆为正整数。在一些实施例中,显示器100可以由玻璃基板或塑胶基板所制成,但不限于此。

[0042]

如图1所示,显示装置110包含多级彼此串接的像素驱动电路dv(1)~dv(n),其中包含像素驱动电路112。在一些实施例中,显示装置110中的像素驱动电路112依据驱动装置120、数据输入装置130与发光控制装置140提供的信号进行发光操作。

[0043]

举例来说,驱动装置120产生驱动信号g(n-1)及gb(n)以驱动像素驱动电路112进行数据写入操作及发光操作,使得像素驱动电路112写入由数据输入装置130提供的数据信号,并且依据发光控制装置140提供的发光信号发光。

[0044]

在不同的实施例中,驱动装置120可以提供驱动信号g(1)~g(n+1)及gb(1)~gb(n+1)的不同组合以驱动像素驱动电路112。在一些实施例中,像素驱动电路112包含低温多晶氧化物主动矩阵有机发光二极管(low-temperature polycrystalline oxide active-matrix organic light-emitting diode,ltpo amoled)实施,但本发明实施例不限于此。在其他的实施例中,像素驱动电路112也可以包含其他类型的发光元件。

[0045]

图2为根据本技术的一实施例所绘示的驱动装置200的示意图。请参照图2及图1,驱动装置200为驱动装置120的一种实施例。

[0046]

如图2所示,驱动装置200用以依据时钟信号ck1、ck2、ck3、ck4、xck1、xck2、xck3及xck4产生驱动信号g(1)~g(n+1)及gb(1)~gb(n+1)。在一些实施例中,驱动装置200藉由图1所示的驱动线sl(0)~sl(n)将驱动信号g(1)~g(n+1)及gb(1)~gb(n+1)传输至像素驱动电路dv(1)~dv(n)。在一些实施例中,驱动装置200还用以依据起始信号st及重置信号rst进行控制。

[0047]

如图2所示,驱动装置200包括驱动单元du(1)~du(n+1)。

[0048]

如图2所示,驱动单元du(1)用以依据时钟信号ck3、xck1、xck3及下级驱动信号g(2)产生驱动信号g(1)及gb(1)。驱动单元du(2)用以依据时钟信号ck4、xck2、xck4、上级驱

动信号g(1)及下级驱动信号g(3)产生驱动信号g(2)及gb(2)。驱动单元du(3)用以依据时钟信号ck1、xck3、xck1、上级驱动信号g(2)及下级驱动信号g(4)产生驱动信号g(3)及gb(3)。驱动单元du(4)用以依据时钟信号ck2、xck4、xck2、上级驱动信号g(3)及下级驱动信号g(5)产生驱动信号g(4)及gb(4)。以此类推,驱动单元du(n)用以依据时钟信号ck3、xck1、xck3、上级驱动信号g(n-1)及下级驱动信号g(n+1)产生驱动信号g(n)及gb(n)。驱动单元du(n+1)用以依据时钟信号ck4、xck2、xck4及上级驱动信号g(n)产生驱动信号g(n+1)及gb(n+1)。

[0049]

如图2所示,在一些实施例中,驱动单元du(1)还用以依据起始信号st进行操作,且驱动单元du(n+1)还用以依据重置信号rst进行操作。

[0050]

在一些实施例中,驱动单元du(1)~du(n+1)的每一个具有类似的电路配置,例如图3所示的驱动单元300的电路配置,并依据对应的时钟信号进行操作。

[0051]

举例来说,请参照图3及图2,驱动单元du(n)包含对应驱动单元300中的开关t33~t312、t321及t322的多个开关以及对应电容c31及c32的电容。其中对应开关t311及t312的开关用以接收时钟信号xck1,对应开关t35、t37及t38的开关用以接收时钟信号ck3,对应电容c32的电容用以接收时钟信号xck3。

[0052]

举另一例来说,驱动单元du(2)包含对应驱动单元300中的开关t33~t312、t321及t322的多个开关以及对应电容c31及c32的电容。其中对应开关t311及t312的开关用以接收时钟信号xck2,对应开关t35、t37及t38的开关用以接收时钟信号ck4,对应电容c32的电容用以接收时钟信号xck4。

[0053]

又举另一例来说,驱动单元du(3)包含对应驱动单元300中的开关t33~t312、t321及t322的多个开关以及对应电容c31及c32的电容。其中对应开关t311及t312的开关用以接收时钟信号xck3,对应开关t35、t37及t38的开关用以接收时钟信号ck1,对应电容c32的电容用以接收时钟信号xck1。

[0054]

再举另一例来说,驱动单元du(4)包含对应驱动单元300中的开关t33~t312、t321及t322的多个开关以及对应电容c31及c32的电容。其中对应开关t311及t312的开关用以接收时钟信号xck4,对应开关t35、t37及t38的开关用以接收时钟信号ck2,对应电容c32的电容用以接收时钟信号xck2。

[0055]

驱动单元du(1)~du(n+1)的驱动操作揭示如上,但本发明实施例不限于此,其他藉由时钟信号ck1、ck2、ck3、ck4、xck1、xck2、xck3、xck4、上级驱动信号及下级驱动信号产生驱动信号g(1)~g(n+1)及gb(1)~gb(n+1)的方式亦在本揭示内容思及范围内。

[0056]

图3为根据本技术的一实施例所绘示的驱动装置中的驱动单元300的电路图。请参照图2及图3,驱动单元300为驱动单元du(n)的一种实施例。

[0057]

如图3所示,驱动单元300用以接收时钟信号ck3、xck1、xck3、上级驱动信号g(n-1)及下级驱动信号g(n+1)以产生驱动信号g(n)及gb(n)。驱动单元300包含启动电路310、320、稳压电路330、340及输出电路350。

[0058]

如图3所示,启动电路310用以依据驱动信号g(n-1)、g(n+1)及电压信号u2d、d2u调整节点n31的节点电压q(n)的电压电平。在一些实施例中,启动电路310用以依据驱动信号g(n-1)或g(n+1)导通使得对应的电压信号u2d或d2u写入节点n31。

[0059]

如图3所示,启动电路320用以依据驱动信号g(n-1)、g(n+1)及电压信号u2d、d2u调整节点n32的节点电压k(n)的电压电平。在一些实施例中,启动电路320用以依据驱动信号g

(n-1)或g(n+1)导通使得对应的电压信号u2d或d2u写入节点n32。

[0060]

在一些实施例中,电压信号u2d具有致能电压电平vgh且电压信号d2u具有禁能电压电平vgl,例如对应图4所述的操作的实施例。在一些实施例中,电压信号d2u具有致能电压电平vgh且电压信号u2d具有禁能电压电平vgl,例如对应图5所述的操作的实施例。关于图4及图5的实施例的细节在以下有进一步的叙述。

[0061]

如图3所示,稳压电路330用以依据时钟信号ck3稳压节点n31的节点电压q(n)及节点n33的节点电压p(n),并用以依据节点电压q(n)稳压节点n33的节点电压p(n)。

[0062]

如图3所示,稳压电路340用以依据时钟信号ck3稳压节点n32的节点电压k(n),并用以依据时钟信号xck3调整节点电压k(n)。

[0063]

如图3所示,输出电路350用以依据节点电压q(n)及节点电压k(n)调整节点n34的节点电压,并用以从节点n34输出驱动信号gb(n)。如图3所示,输出电路350还用以依据节点电压q(n)及节点电压p(n)调整节点n35的节点电压,并用以从节点n35输出驱动信号g(n)。

[0064]

驱动单元300之内部电路的运作方式揭示如上,但本发明实施例不限于此,启动电路310、320、稳压电路330、340及输出电路350的其他运作方式亦在本揭示内容思及范围内。

[0065]

如图3所示,启动电路310包括开关t33及t34。开关t33的控制端用以接收驱动信号g(n-1),开关t33的一端耦接节点n31,开关t33的另一端用以接收电压信号u2d。开关t34的控制端用以接收驱动信号g(n+1),开关t34的一端耦接节点n31,开关t34的另一端用以接收电压信号d2u。

[0066]

如图3所示,启动电路320包括开关t310及t39。开关t310的控制端用以接收驱动信号g(n+1),开关t310的一端耦接节点n32,开关t310的另一端用以接收电压信号u2d。开关t39的控制端用以接收驱动信号g(n-1),开关t39的一端耦接节点n32,开关t39的另一端用以接收电压信号d2u。

[0067]

如图3所示,稳压电路330包括开关t35~t37。开关t35的控制端用以接收时钟信号ck3,开关t35的一端耦接节点n31,开关t35的另一端用以接收电压信号gl。开关t36的控制端耦接节点n31,开关t36的一端耦接节点n33,开关t36的另一端用以接收电压信号gl。开关t37的控制端用以接收时钟信号ck3,开关t37的一端耦接节点n33,开关t37的另一端用以接收电压信号gh。

[0068]

如图3所示,稳压电路340包括开关t38及电容c32。开关t38的控制端用以接收时钟信号ck3,开关t38的一端耦接节点n32,开关t38的另一端用以接收电压信号gh。电容c32的一端耦接节点n32,电容c32另一端用以接收时钟信号xck3。

[0069]

如图3所示,输出电路350包括开关t311、t312、t321、t322及电容c31。开关t311的控制端耦接节点n31,开关t311的一端耦接节点n35,开关t311的另一端用以接收时钟信号xck1。开关t312的控制端耦接节点n31,开关t312的一端耦接节点n34,开关t312的另一端用以接收时钟信号xck1。开关t321的控制端耦接节点n33,开关t321的一端耦接节点n35,开关t321的另一端用以接收电压信号gl。开关t322的控制端耦接节点n32,开关t322的一端耦接节点n34,开关t322的另一端用以接收电压信号gh。电容c31的一端耦接节点n31,电容c31另一端耦接节点n35。

[0070]

在一些实施例中,开关t311、t312、t321及t322是以低温多晶硅薄膜晶体管(low temperature poly-silicon thin film transistor,ltps tft)实施。ltps晶体管具有高

电流驱动的特性,驱动功率较高,且可以在所占布局面积较小的情况下驱动较大的电流。在一些实施例中,t33~-t310是以氧化铟镓锌薄膜晶体管(indium gallium zinc oxide thin film transistor,igzo tft)实施。igzo晶体管具有低漏电流的特性,可以防止驱动单元300内部的节点电压在输出驱动信号时受漏电流影响,而影响所输出的驱动信号。在不同实施例中,开关t33~t312、t321及t322也可以藉由不同的开关元件实施。

[0071]

图4为根据本揭示内容的一实施例中的驱动单元300进行驱动操作所绘示的时序图。图4所绘示的时序图依序包括期间p41~p48。在一些实施例中,期间p41~p48对应一个帧时间(frame time)。

[0072]

在一些实施例中,图4所绘示的时序图对应图2及图3所示的不同信号,例如时钟信号ck1、ck2、ck3、ck4、xck1、xck2、xck3、xck4及驱动信号g(n-1)、g(n)、g(n+1)、gb(n)的操作,以及驱动单元300中的节点电压q(n)、p(n)及k(n)的电压电平。

[0073]

如图4所示,在期间p41,驱动信号g(n-1)具有致能电压电平vgh,使得开关t33及t39导通。此时开关t33将具有致能电压电平vgh的电压信号u2d写入至节点n31,使得节点n31的节点电压q(n)具有电压电平(vgh-v

th33

),其中临界电压电平v

th33

为开关t33的临界电压电平。此时开关t39将具有禁能电压电平vgl的电压信号d2u写入至节点n32,使得节点n32的节点电压k(n)具有禁能电压电平vgl,且开关t322关闭。

[0074]

在期间p41,节点电压q(n)的电压电平(vgh-v

th33

)为致能电压电平,使得开关t36、t311及t312依据节点电压q(n)的电压电平(vgh-v

th33

)导通。在一些实施例中,电容c31用以存储节点n31的电荷以在开关t33关闭后维持节点n31的电压电平,使得开关t36、t311及t312在开关t33关闭后(例如在期间p42中)持续导通。

[0075]

在期间p41,开关t36将具有禁能电压电平vgl的电压信号gl写入至节点n33,使得节点n33的节点电压p(n)具有禁能电压电平vgl,且开关t321依据节点电压p(n)关闭。开关t311将具有禁能电压电平vgl的时钟信号xck1写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。开关t312将具有禁能电压电平vgl的时钟信号xck1写入至节点n34,使得节点n34具有禁能电压电平vgl。此时输出电路350从节点n34输出具有禁能电压电平vgl的驱动信号gb(n)。

[0076]

如图4所示,在期间p42,驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。此时电容c31将节点电压q(n)维持在致能电压电平,使得开关t36、t311及t312导通。

[0077]

在期间p42,开关t36将具有禁能电压电平vgl的电压信号gl写入至节点n33,使得节点n33的节点电压p(n)具有禁能电压电平vgl,且开关t321依据节点电压p(n)关闭。

[0078]

在期间p42,开关t311将具有致能电压电平vgh的时钟信号xck1写入至节点n35,使得节点n35具有致能电压电平vgh。此时输出电路350从节点n35输出具有致能电压电平vgh的驱动信号g(n)。电容c21通过电容耦合藉由节点n35的电压调整节点n31的电压,使得节点n31的电压电平被调整至大于电压电平(vgh+v

thltps

)的电压电平vq,其中临界电压电平v

thltps

为开关t311的临界电压电平。在一些实施例中,开关t311以ltps晶体管实施,临界电压电平v

thltps

为ltps晶体管的临界电压电平。

[0079]

在期间p42,开关t312将具有致能电压电平vgh的时钟信号xck1写入至节点n34,使得节点n34具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh

的驱动信号gb(n)。

[0080]

如图4所示,在期间p43,驱动信号g(n+1)具有致能电压电平vgh,使得开关t34及t310导通。时钟信号ck3具有致能电压电平vgh,使得开关t35、t37及t38导通。

[0081]

在期间p43,开关t34将具有禁能电压电平vgl的电压信号d2u写入至节点n31,使得节点n31的节点电压q(n)具有禁能电压电平vgl。开关t35将具有禁能电压电平vgl的电压信号gl写入至节点n31以进一步稳压节点电压q(n)。

[0082]

在期间p43,开关t37将具有致能电压电平vgh的电压信号gh写入至节点n33,使得节点n33的节点电压p(n)具有电压电平(vgh-v

th37

),其中临界电压电平v

th37

为开关t37的临界电压电平。

[0083]

在一些实施例中,在期间p43,电压电平(vgh-v

th37

)为致能电压电平,使得开关t321依据节点电压p(n)的电压电平(vgh-v

th37

)导通。在一些实施例中,节点n33的寄生电容用以存储节点n33的电荷以在开关t37关闭后维持节点n33的电压电平,使得开关t321在开关t37关闭后(例如在期间p44中)持续导通。

[0084]

在期间p43,开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0085]

在期间p43,开关t310将具有致能电压电平vgh的电压信号u2d写入至节点n32,以调整节点n32的节点电压k(n)。开关t38将具有致能电压电平vgh的电压信号gh写入至节点n32以进一步稳压节点电压k(n)。此时节点电压k(n)具有电压电平(vgh-v

th310

)或(vgh-v

th38

),其中临界电压电平v

th38

及v

th310

分别为开关t38及t310的临界电压电平。在一些实施例中,临界电压电平v

th38

及v

th310

实质上等同。以下藉由节点电压k(n)具有电压电平(vgh-v

th38

)的情况进行说明,但节点电压k(n)具有电压电平(vgh-v

th310

)的情况亦在本发明实施例思及范围内。

[0086]

在期间p43,电容c32用以存储电荷以在期间p43之后(例如期间p44中)将节点电压k(n)进一步抬升。

[0087]

在期间p43,节点n34的寄生电容将节点n34的节点电压维持在致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0088]

如图4所示,在期间p44,驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。此时节点n33的寄生电容将节点电压p(n)维持在致能电压电平,使得开关t321导通。开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0089]

从期间p43至期间p44,电容c32将节点电压k(n)维持在致能电压电平。在期间p44,电容c32用以接收具有致能电压电平vgh的时钟信号xck3,并且通过电容耦合进一步抬升节点电压k(n)。此时节点电压k(n)具有高于电压电平(vgh+v

thltps

)的电压电平vk,使得开关t322导通。开关t322将具有致能电压电平vgh的电压信号gh写入节点n34,使得节点n34的具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0090]

如图4所示,在期间p45~p46,开关t33~t312、t321及t322的导通或关闭的状态与期间p44中的状态相同,且具有类似的操作。因此,期间p45~p46的操作与期间p44的操作的

类似之处于此不再赘述。

[0091]

在期间p45~p46,开关t321及t322分别依据节点电压p(n)及k(n)导通,使得开关t321提供具有禁能电压电平vgl的电压信号gl至节点n35,且t322提供具有致能电压电平vgh的电压信号gh至节点n34。对应地,此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n),且输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。换句话说,在期间p45~p46,稳压电路330及340藉由节点电压p(n)及k(n)稳压驱动信号g(n)及gb(n)。

[0092]

如图4所示,在期间p47,时钟信号ck3具有致能电压电平vgh,使得开关t35、t37及t38导通。开关t35将电压信号gl写入至节点n31,使得节点电压q(n)具有禁能电压电平vgl。开关t37将电压信号gh写入至节点n33,使得节点电压p(n)具有电压电平(vgh-v

th37

)。

[0093]

在期间p47,开关t321依据节点电压p(n)的电压电平(vgh-v

th37

)导通,并且将电压信号gl写入至节点n35。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0094]

在期间p47,开关t38将电压信号gh写入至节点n32,且电容c32所接收的时钟信号xck3具有禁能电压电平vgl,使得节点电压k(n)具有电压电平(vgh-v

th38

)。此时节点n34的寄生电容将驱动信号gb(n)的电压电平维持在致能电压电平vgh。

[0095]

如图4所示,在期间p48,时钟信号ck3具有禁能电压电平vgl,使得开关t35、t37及t38关闭。驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。

[0096]

在期间p48,节点电压q(n)具有禁能电压电平vgl,使得开关t36、t311及t312关闭。节点n33的寄生电容将节点电压p(n)维持在(vgh-v

th37

),使得开关t321导通。开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0097]

从期间p47至期间p48,电容c32将节点电压k(n)维持在致能电压电平。在期间p48,电容c32用以接收具有致能电压电平vgh的时钟信号xck3,并且通过电容耦合进一步抬升节点电压k(n)。此时节点电压k(n)具有高于电压电平(vgh+v

thltps

)的电压电平vk,使得开关t322导通。开关t322将具有致能电压电平vgh的电压信号gh写入节点n34,使得节点n34的具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0098]

综上所述,驱动单元300藉由期间p41~p48的操作产生与驱动信号g(n-1)互补的驱动信号gb(n)。如图4所示,在期间p41~p48中,在驱动信号g(n-1)具有致能电压电平vgh时,驱动信号gb(n)具有禁能电压电平vgl,且在驱动信号g(n-1)具有禁能电压电平vgl时,驱动信号gb(n)具有致能电压电平vgh。

[0099]

类似地,驱动单元300藉由期间p41~p48的操作产生与驱动信号gb(n+1)互补的驱动信号g(n)。其中驱动信号gb(n+1)可以藉由图2所示的驱动单元du(n+1)产生。

[0100]

在一些实施例中,图1所示的驱动装置120藉由互补的驱动信号g(n-1)及驱动信号gb(n)驱动像素驱动电路112。

[0101]

图5为根据本揭示内容的一实施例中的驱动单元300进行驱动操作所绘示的时序图。图5所绘示的时序图依序包括期间p51~p58。在一些实施例中,期间p51~p58对应一个

帧时间。

[0102]

在一些实施例中,图5所绘示的时序图对应图2及图3所示的不同信号,例如时钟信号ck1、ck2、ck3、ck4、xck1、xck2、xck3、xck4及驱动信号g(n-1)、g(n)、g(n+1)、gb(n)的操作,以及驱动单元300中的节点电压q(n)、p(n)及k(n)的电压电平。

[0103]

如图5所示,在期间p51,驱动信号g(n+1)具有致能电压电平vgh,使得开关t34及t310导通。此时开关t34将具有致能电压电平vgh的电压信号d2u写入至节点n31,使得节点n31的节点电压q(n)具有电压电平(vgh-v

th34

),其中临界电压电平v

th34

为开关t34的临界电压电平。此时开关t310将具有禁能电压电平vgl的电压信号u2d写入至节点n32,使得节点n32的节点电压k(n)具有禁能电压电平vgl,且开关t322关闭。

[0104]

在期间p51,节点电压q(n)的电压电平(vgh-v

th34

)为致能电压电平,使得开关t36、t311及t312依据节点电压q(n)的电压电平(vgh-v

th34

)导通。在一些实施例中,电容c31用以存储节点n31的电荷以在开关t34关闭后维持节点n31的电压电平,使得开关t36、t311及t312在开关t33关闭后(例如在期间p52中)持续导通。

[0105]

在期间p51,开关t36将具有禁能电压电平vgl的电压信号gl写入至节点n33,使得节点n33的节点电压p(n)具有禁能电压电平vgl,且开关t321依据节点电压p(n)关闭。开关t311将具有禁能电压电平vgl的时钟信号xck1写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。开关t312将具有禁能电压电平vgl的时钟信号xck1写入至节点n34,使得节点n34具有禁能电压电平vgl。此时输出电路350从节点n34输出具有禁能电压电平vgl的驱动信号gb(n)。

[0106]

如图4所示,在期间p52,驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。此时电容c31将节点电压q(n)维持在致能电压电平,使得开关t36、t311及t312导通。

[0107]

在期间p52,开关t36将具有禁能电压电平vgl的电压信号gl写入至节点n33,使得节点n33的节点电压p(n)具有禁能电压电平vgl,且开关t321依据节点电压p(n)关闭。

[0108]

在期间p52,开关t311将具有致能电压电平vgh的时钟信号xck1写入至节点n35,使得节点n35具有致能电压电平vgh。此时输出电路350从节点n35输出具有致能电压电平vgh的驱动信号g(n)。电容c21通过电容耦合藉由节点n35的电压调整节点n31的电压,使得节点n31的电压电平被调整至电压电平vq。

[0109]

在期间p52,开关t312将具有致能电压电平vgh的时钟信号xck1写入至节点n34,使得节点n34具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0110]

如图5所示,在期间p53,驱动信号g(n-1)具有致能电压电平vgh,使得开关t33及t39导通。时钟信号ck3具有致能电压电平vgh,使得开关t35、t37及t38导通。

[0111]

在期间p53,开关t34将具有禁能电压电平vgl的电压信号u2d写入至节点n31,使得节点n31的节点电压q(n)具有禁能电压电平vgl。开关t35将具有禁能电压电平vgl的电压信号gl写入至节点n31以进一步稳压节点电压q(n)。

[0112]

在期间p53,开关t37将具有致能电压电平vgh的电压信号gh写入至节点n33,使得节点n33的节点电压p(n)具有电压电平(vgh-v

th37

)。

[0113]

在期间p53,节点电压p(n)的电压电平(vgh-v

th37

)为致能电压电平,使得开关t321

导通。在一些实施例中,节点n33的寄生电容用以存储节点n33的电荷以在开关t37关闭后维持节点n33的电压电平,使得开关t321在开关t37关闭后(例如在期间p54中)持续导通。

[0114]

在期间p53,开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0115]

在期间p53,开关t39将具有致能电压电平vgh的电压信号d2u写入至节点n32,以调整节点n32的节点电压k(n)。开关t38将具有致能电压电平vgh的电压信号gh写入至节点n32以进一步稳压节点电压k(n)。此时节点电压k(n)具有电压电平(vgh-v

th39

)或(vgh-v

th38

),其中临界电压电平v

th39

为开关t39的临界电压电平。在一些实施例中,临界电压电平v

th38

及v

th39

实质上等同。以下藉由节点电压k(n)具有电压电平(vgh-v

th38

)的情况进行说明,但节点电压k(n)具有电压电平(vgh-v

th39

)的情况亦在本发明实施例思及范围内。

[0116]

在期间p53,电容c32用以存储电荷以在期间p53之后(例如期间p54中)将节点电压k(n)进一步抬升。

[0117]

在期间p53,节点n34的寄生电容将节点n34的节点电压维持在致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0118]

如图5所示,在期间p54,驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。此时节点n33的寄生电容将节点电压p(n)维持在致能电压电平,使得开关t321导通。开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0119]

从期间p53至期间p54,电容c32将节点电压k(n)维持在致能电压电平。在期间p54,电容c32用以接收具有致能电压电平vgh的时钟信号xck3,并且通过电容耦合进一步抬升节点电压k(n)。此时节点电压k(n)具有高于电压电平(vgh+v

thltps

)的电压电平vk,使得开关t322导通。开关t322将具有致能电压电平vgh的电压信号gh写入节点n34,使得节点n34的具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0120]

如图5所示,在期间p55~p56,开关t33~t312、t321及t322的导通或关闭的状态与期间p54中的状态相同,且具有类似的操作。因此,期间p55~p56的操作与期间p54的操作的类似之处于此不再赘述。

[0121]

在期间p55~p56,开关t321及t322分别依据节点电压p(n)及k(n)导通,使得开关t321提供具有禁能电压电平vgl的电压信号gl至节点n35,且t322提供具有致能电压电平vgh的电压信号gh至节点n34。对应地,此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n),且输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。换句话说,在期间p55~p56,稳压电路330及340藉由节点电压p(n)及k(n)稳压驱动信号g(n)及gb(n)。

[0122]

如图5所示,在期间p57,时钟信号ck3具有致能电压电平vgh,使得开关t35、t37及t38导通。开关t35将电压信号gl写入至节点n31,使得节点电压q(n)具有禁能电压电平vgl。开关t37将电压信号gh写入至节点n33,使得节点电压p(n)具有电压电平(vgh-v

th37

)。

[0123]

在期间p57,开关t321依据节点电压p(n)的电压电平(vgh-v

th37

)导通,并且将电压信号gl写入至节点n35。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号

g(n)。

[0124]

在期间p57,开关t38将电压信号gh写入至节点n32,且电容c32所接收的时钟信号xck3具有禁能电压电平vgl,使得节点电压k(n)具有电压电平(vgh-v

th38

)。此时节点n34的寄生电容将驱动信号gb(n)的电压电平维持在致能电压电平vgh。

[0125]

如图4所示,在期间p58,时钟信号ck3具有禁能电压电平vgl,使得开关t35、t37及t38关闭。驱动信号g(n-1)及g(n+1)具有禁能电压电平vgl,使得启动电路310及320中的开关t33、t34、t310及t39关闭。

[0126]

在期间p58,节点电压q(n)具有禁能电压电平vgl,使得开关t36、t311及t312关闭。节点n33的寄生电容将节点电压p(n)维持在(vgh-v

th37

),使得开关t321导通。开关t321将具有禁能电压电平vgl的电压信号gl写入至节点n35,使得节点n35具有禁能电压电平vgl。此时输出电路350从节点n35输出具有禁能电压电平vgl的驱动信号g(n)。

[0127]

从期间p57至期间p58,电容c32将节点电压k(n)维持在致能电压电平。在期间p58,电容c32用以接收具有致能电压电平vgh的时钟信号xck3,并且通过电容耦合进一步抬升节点电压k(n)。此时节点电压k(n)具有高于电压电平(vgh+v

thltps

)的电压电平vk,使得开关t322导通。开关t322将具有致能电压电平vgh的电压信号gh写入节点n34,使得节点n34的具有致能电压电平vgh。此时输出电路350从节点n34输出具有致能电压电平vgh的驱动信号gb(n)。

[0128]

综上所述,驱动单元300藉由期间p51~p58的操作产生与驱动信号g(n+1)互补的驱动信号gb(n)。如图5所示,在期间p51~p58中,在驱动信号g(n+1)具有致能电压电平vgh时,驱动信号gb(n)具有禁能电压电平vgl,且在驱动信号g(n+1)具有禁能电压电平vgl时,驱动信号gb(n)具有致能电压电平vgh。

[0129]

类似地,驱动单元300藉由期间p51~p58的操作产生与驱动信号gb(n-1)互补的驱动信号g(n)。其中驱动信号gb(n-1)可以藉由图2所示的驱动装置200中的驱动单元du(n-1)产生。

[0130]

请参照图4及图5,在期间p41~p44中,时钟信号ck1~ck4依序被拉至致能电压电平vgh,且时钟信号xck1~xck4依序被拉至禁能电压电平vgl。对应地,在图4对应的实施例中,驱动信号g(n-1)、g(n)及g(n+1)依序被拉至致能电压电平vgh。在一些实施例中,图4所示的操作被称为驱动装置(例如图2所示的驱动装置200)的正向传输。

[0131]

反之,在期间p51~p54中,时钟信号ck1、ck4、ck3、ck2依序被拉至致能电压电平vgh,且时钟信号xck1、xck4、xck3、xck2依序被拉至禁能电压电平vgl。对应地,在图5对应的实施例中,驱动信号g(n+1)、g(n)及g(n-1)依序被拉至致能电压电平vgh。在一些实施例中,图5所示的操作被称为驱动装置(例如图2所示的驱动装置200)的反向传输。

[0132]

在一些先前的作法中,栅极驱动装置只有单向传输功能,只能进行正向传输或反向传输的其中一个。

[0133]

相较于上述的作法,在本发明实施例中,图2及图3所示的驱动装置200及驱动单元300可以藉由图4及图5所示的操作进行正向传输及反向传输。

[0134]

本技术前述各种驱动方式及传输方式用于说明,其他各种驱动方式及传输方式都在本技术思及的范围中。

[0135]

综上所述,在本发明实施例中,可以藉由调整驱动单元300所接收的电压信号u2d

及d2u的电压电平进行正向传输或反向传输。此外,电容c32的配置藉由时钟信号xck3定期抬升节点电压k(n)以导通开关t322稳压驱动信号gb(n),稳压时间长达75%的帧时间。藉由节点电压p(n)及q(n)的配置在期间p43~p48及p53~p58中导通开关t321以长时间稳压驱动信号g(n)。另外,ltps晶体管及igzo晶体管对应开关t33~t312、t321及t322的配置可以降低漏电流并且同时驱动较大的电流且降低所占布局面积。

[0136]

虽然本发明已以实施例公开如上,然其并非用以限定本发明,本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,故本发明的保护范围当视所附权利要求书界定范围为准。