1.本技术涉及显示面板驱动领域,具体涉及一种拼接屏驱动架构。

背景技术:

2.在显示面板行业中,商用拼接屏越来越受欢迎,拼接屏广泛应用于会场,商场等场所,其灵活的拼接方式,可以满足不同大小会议场所对高清显示的需求。裸眼3d作为近些年发展起来的潮流技术,给观众带来更加真实震撼的视觉效果,吸引了大众对裸眼3d的热情。

3.随着8k产品的广泛应用,8k拼接屏逐渐进入显示行业视野,但目前业界驱动8k拼接屏的方案少之又少,常见的电路驱动方案仅可以支持到拼接后的图片显示完整的4k或者8k分辨率。现有的裸眼3d方案也主要集中在8k及以下分辨率;无法实现更高分辨率的3d画面显示;且驱动架构复杂,成本较高。

技术实现要素:

4.本技术旨在提供一种拼接屏驱动架构及驱动方法,旨在解决现有技术中的3d8k画面驱动架构复杂,成本较高的问题。

5.第一方面,本技术实施例提供一种拼接屏驱动架构,所述拼接屏包括m*n块子显示屏,所述拼接屏驱动架构包括:

6.多个信号转换单元和多个用于转换接口的接口转换单元,所述多个信号转换单元与所述多个接口转换单元电连接;所述m*n块子显示屏中每个子显示屏包括至少一个子显示屏驱动电路;其中,所述m和n均为大于或等于一的正整数。

7.所述多个信号转换单元中每个信号转换单元用于接收外部驱动信号,且将所述驱动信号发送至所述接口转换单元;所述接口转换单元用于接收所述信号转换单元发出的外部驱动信号,且将所述外部驱动信号发送至所述子显示屏驱动电路。

8.在一种可能的实施例中,所述接口转换单元的数量和所述子显示屏驱动电路的数量相同。

9.在一种可能的实施例中,所述信号转换单元的数量与所述接口转换单元的数量相同。

10.在一种可能的实施例中,任意一个信号转换单元通过自身的多个信号输出接口与任意一个接口转换单元连接。

11.在一种可能的实施例中,所述信号转换单元的数量小于所述接口转换单元的数量。

12.在一种可能的实施例中,任意一个信号转换单元通过自身的多个信号输出接口同时与多个接口转换单元连接。

13.在一种可能的实施例中,所述拼接屏驱动架构还包括同步模块,所述同步模块用于同步所述多个信号转换单元输出的驱动信号。

14.在一种可能的实施例中,所述多个接口转换单元利用同轴线实现时序同步。

的含义是两个或两个以上,除非另有明确具体的限定。

26.在本技术中,“示例性”一词用来表示“用作例子、例证或说明”。本技术中被描述为“示例性”的任何实施例不一定被解释为比其它实施例更优选或更具优势。为了使本领域任何技术人员能够实现和使用本技术,给出了以下描述。在以下描述中,为了解释的目的而列出了细节。应当明白的是,本领域普通技术人员可以认识到,在不使用这些特定细节的情况下也可以实现本技术。在其它实例中,不会对公知的结构和过程进行详细阐述,以避免不必要的细节使本技术的描述变得晦涩。因此,本技术并非旨在限于所示的实施例,而是与符合本技术所公开的原理和特征的最广范围相一致。

27.需要说明的是,本技术实施例方法由于是在电子设备中执行,各电子设备的处理对象均以数据或信息的形式存在,例如时间,实质为时间信息,可以理解的是,后续实施例中若提及尺寸、数量、位置等,均为对应的数据存在,以便电子设备进行处理,具体此处不作赘述。

28.本技术实施例提供一种拼接屏驱动架构及驱动方法,以下分别进行详细说明。

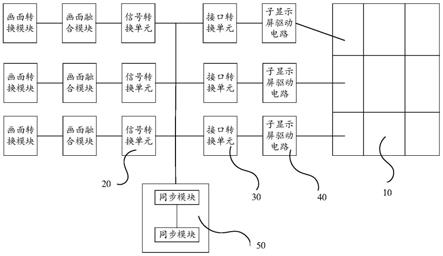

29.请参阅图1,图1为本技术实施例提供的拼接屏驱动架构一实施例示意图。在图1中,拼接屏包括m*n块子显示屏10,m*n块子显示屏各自显示的画面拼接后形成一个完整的画面。而拼接屏驱动架构可以包括多个信号转换单元20、多个用于转换接口的接口转换单元30,多个信号转换单元20与多个接口转换单元30电连接;而m*n块子显示屏10中每个子显示屏10中包括至少一个子显示屏驱动电路40。

30.而多个信号转换单元20中每个信号转换单元20用于接收外部驱动信号,且将驱动信号发送至接口转换单元30。接口转换单元30用于接收信号转换单元发出的外部驱动信号,且将外部驱动信号发送至子显示屏驱动电路40。

31.本技术提供一种拼接屏驱动架构,该拼接屏驱动架构仅包括多个信号转换单元和多个用于转换接口的接口转换单元,以及多个子显示屏驱动电路;所述多个信号转换单元中每个信号转换单元用于接收外部驱动信号,且将所述驱动信号发送至所述接口转换单元;所述接口转换单元用于接收所述信号转换单元发出的外部驱动信号,且将所述外部驱动信号发送至所述子显示屏驱动电路,使得子显示屏显示画面。整个拼接屏驱动架构仅包括信号转换单元、接口转换单元、子显示屏驱动电路和子显示屏,驱动架构简单,用少量的电路板即可实现拼接屏的驱动,大大降低成本。

32.在本技术的实施例中,信号转换单元20主要是将外部驱动信号转换为显示屏可以显示的驱动信号。而接口转换单元实际上是考虑到实际的驱动场景,不同的硬件设备包括多个不同的硬件接口(hardware interface),其中硬件接口指的是两个硬件设备之间的连接方式;硬件接口既包括物理上的接口,还包括逻辑上的数据传输协议。

33.因此不同的硬件接口之间既需要物理连接,还需要两个接口对应的数据传输协议匹配,才能够利用物理接口传输数据。而硬件设备可以同时包括多个信号输入接口和多个信号输出接口,多个信号输入接口和多个信号输出接口的对应的数据传输协议可以不匹配。本技术实施例中提供的接口转换单元30也包括信号输入接口和信号输出接口,且接口转换单元30中的信号输入接口和信号输出接口对应的数据传输协议不匹配。而接口转换单元30的信号输入接口对应的数据传输协议,与信号转换单元20的信号输出接口对应的信号传输协议匹配;信号转换单元20可以利用自身的信号输出接口将信号发送给接口转换单元

30的信号输入接口。

34.同理,本技术实施例中接口转换单元30的信号输出接口对应的数据传输协议,与子显示屏驱动电路40的信号输入接口对应的传输协议匹配;接口转换单元30可以利用自身的信号输出接口将信号发送给子显示屏驱动电路40的信号输入接口。而本技术实施例中,信号转换单元20的信号输出接口对应的信号传输协议,与子显示屏驱动电路40的信号输入接口对应的传输协议不匹配;信号无法直接从信号转换单元20的信号输出接口发送到子显示屏驱动电路40的信号输入接口。因此需要接口转换单元30进行接口的转换;接口转换单路30主要起到接口中转的作用。

35.需要说明的是,在上述实施例中,信号传输协议匹配可以是信号传输协议相同,也可以是信号传输协议不同。对于某些信号传输协议来说,即使两个硬件接口对应的信号传输协议不同,两者之间同样可以传输信号;这是信号传输协议本身的特性。

36.在本技术的一些实施例中,当m*n块子显示屏为多个时,多个子显示屏对应的子显示屏驱动电路40也同样为多个。而在一些实施例中,多个接口转换单元30和多个子显示屏驱动电路40的数量可以相同;一个接口转换单元30与唯一一个确定的子显示屏驱动电路40连接。即一个接口转换单路30与唯一一个确定的子显示屏连接。

37.而当多个接口转换单元30和多个子显示屏驱动电路40的数量相同时,多个信号转换单元20的数量也可以与多个接口转换单元30的数量相同。同样地,一个接口转换单元30与唯一确定的信号转换单元20连接。

38.在上述实施例中,多个信号转换单元20、多个接口转换单元30和多个子显示屏驱动电路40的数量均相同;且一个信号转换单元20连接唯一确定的接口转换单元30,一个接口转换单元30连接唯一确定的子显示屏驱动电路40。

39.需要说明的是,在实际的驱动场景中,包括但不限于信号转换单元20、接口转换单元30和子显示屏驱动电路40等硬件设备中,通常均包括多个输入与输出接口。例如,在本技术的实施例中,任意一个信号转换单元20均包括多个信号输入接口和多个信号输出接口;而任意一个信号转换单元20通过自身的多个信号输出接口与任意一个接口转换单元30连接。即一个信号转换单元20仅与一个接口转换单元30连接。

40.在另一些实施例中,多个信号转换单元20的数量可以小于多个接口转换单元30的数量。此时,任意一个信号转换单元20通过自身的多个信号输出接口同时与多个接口转化电路30连接。即一个信号转换单元20同时连接多个接口转换单元30。

41.而考虑到实际的成本等问题,通常情况下也是一个信号转换单元20同时连接多个接口转换单元30,这样同样可以实现驱动功能,且节省成本。

42.请参考图1,在图1所示的实施例中,该拼接屏驱动架构还可以包括同步模块50;而同步模块50主要是用于同步多个信号转换单元20输出的驱动信号。即由于需要保持m*n个子显示屏上显示的画面可以拼接为一个完整的画面,因此需要保证输入每个子显示屏中的画面保持同步。

43.而在本技术的实施例中,同步模块50通常同时控制多个信号转换单元20,以控制多个信号转换单元20输出的驱动信号保持同步。而当有多个同步模块50时,多个同步模块50之间也需要保持同步。在实际的驱动场景中,若是有多个同步模块50,则多个同步模块50之间通常利用网线实现物理连接而保持同步。

44.需要说明的是,不仅多个信号转换单元20输出的驱动信号需要保持同步,多个接口转换单元30输出的驱动信号也需要保持同步。在本技术的一些实施例中,多个接口转换单元30之间可以利用同轴线实现时序同步;即多个接口转换单元30之间也利用网线等实现物理连接而保持同步。

45.由于本技术实施例中的拼接屏显示的通常为3d画面,需要将普通的2d画面进行处理转换为3d画面,才能在拼接屏上显示为3d画面。因此在本技术的一些实施例中,拼接屏驱动架构还可以包括画面转换模块,画转换模块主要用于将初始驱动信号对应的画面转换为3d画面,并生成与3d画面对应的驱动信号以将驱动信号发送给多个信号转换单元。

46.又由于本技术中拼接屏中每个子显示屏显示画面的一部分,所有子显示屏对应的显示画面结合在一起才是一个完整的3d画面,因此需要将所有子显示屏对应的显示画面进行拼接。因此在本技术的实施例中,需要对拼缝处的画面进行处理,避免在拼缝处出现画面错位模糊等问题。

47.即本技术实施例所提供的拼接屏驱动架构还包括画面融合模块,画面融合模块主要用于对拼缝处的画面进行处理,保证画面在拼缝处过渡均匀。且在本技术的实施例中,初始驱动信号线输入至画面转换模块,将画面转换为3d画面后,再输入至画面融合模块中。画面融合模块接收到3d画面对应的驱动信号后,对驱动信号进行处理,保证拼接屏上拼缝处的画面过渡均匀。而经画面融合模块处理过的驱动信号继续输入至信号转换单元20;信号转换单元20主要是将驱动信号转换为显示屏可以显示的信号。

48.在实际的拼接屏驱动场景中,通常是利用计算机等硬件设备来控制多个子显示屏的画面;因此信号转换单元20、接口转换单元30和子显示屏驱动电路40等可以为安装在计算机设备或子显示屏中的硬件设备。而画面转换模块可以为装载在计算机等硬件设备内部的软件工具,如3d转换软件等;画面融合模块可以为装载在计算机等硬件设备内部的软件工具,如画面处理软件等。

49.在实际的拼接屏驱动场景中,拼接屏中的多个子显示屏中通常为v-by-one(vbo)接口,vbo接口是显示屏和系统芯片之间普遍应用的接口。子显示屏利用vbo接口接收驱动信号,以显示驱动信号对应的3d画面实现3d显示。因此,在本技术的实施例中,与子显示屏vbo接口物理连接的模块也需要是vbo接口。

50.实际的子显示屏通常包括多个不同的单元模块,才能接收外部信号实现画面显示。而本技术实施例中的子显示屏驱动电路实际上是子显示屏内部的一个电路模块,即显示屏实际上也是包括多个不同的电路的;显示屏想要显示画面,实际上是利用自身的多个电路接收外部驱动信号,外部驱动信号驱动电路正常工作以驱动电路中的薄膜晶体管等结构发光,从而显示画面。

51.因此,驱动信号输入子显示屏,实际上是输入子显示屏中的子显示屏驱动电路40中;且子显示屏的输入接口为vbo接口,实际上也是子显示驱动电路40的输入接口为vbo接口。

52.又由于接口转换单元30与子显示屏驱动电路40连接,同样类型的接口才能连接,因此接口转换单元的输出接口同样为vbo接口。这样接口转换单元对应的vbo输出接口,才能和子显示屏驱动电路40的vbo输入接口连接。

53.在本技术的实施例中,信号转换单元20可以为计算机等硬件设备中的显卡,主要

用于处理计算机接收的图像;即显卡将接收到的图像信号经过转换后输出到显示屏上实现显示。因此本技术实施例中,外部的驱动信号实际上是先经过显卡处理后,再由显卡发送到接口转换单元30,再由接口转换单元30发送到子显示屏驱动电路40中。

54.由于显卡对应的输出接口通常为display port(dp)接口,若是信号转换单元20(即显卡)通过信号输入输出接口与接口转换单元30连接,则接口转换单元30对应的信号输入接口与信号转换单元20对应的信号输出接口匹配。即接口转换单元30对应的信号输入接口也为dp输入接口;此时本技术实施例中提供的接口转换单元30对应的信号输入接口为dp输入接口,而对应的信号输出接口为vbo输出接口。

55.如图2所示,为本技术实施例提供的拼接屏驱动架构另一实施例示意图。在图2中,pc即为计算机,而p4000显卡即为信号转换单元20;而a10为arria10电路,即为接口转换单元30;cb为control board电路板,即为子显示屏驱动电路40。

56.在图2中,p4000显卡是设置在计算机pc内部的架构,而a10电路和cb电路可以为设置在子显示屏内部的架构。且在图2中,每个计算机pc上还装载有3d软件和画面融合软件,3d软件和画面融合软件均是对外部初始驱动信号进行处理的软件工具。同时在图2所示的实施例中,拼接屏可以为3*3的结构;且由于cb电路板通常为子显示屏的部分电路结构,因此图2中利用cb直接代表子显示屏。

57.在图2中,计算机可以为五个,分别为pc1-pc5,而每个计算机pc中均包括一个对画面进行处理的3d软件和画面融合软件;且每个计算机pc中均包括一个p4000显卡。而3*3块子显示屏中,每个子显示屏均包括一个a10电路和一个cb电路;且相同子显示屏中的一个a10电路和一个cb电路连接。

58.在图2所示的实施例中,信号转换单元20(即p4000显卡)的数量小于接口转换单元30(即a10电路)的数量;而接口转换单元30(即a10电路)的数量与子显示屏驱动电路40(即cb)的数量相同。此时,一个信号转换单元20可以同时与多个接口转换单元30连接,即一个信号转换单元20可以同时控制多个不同的子显示屏。

59.具体地,一个信号转换单元20可以包括四个dp接口(即4dp),而四个dp接口中任意两个dp接口(即2dp)分别与两个不同的接口转换单元30连接;这样一个信号转换单元20可以同时控制多个不同的子显示屏,节省硬件成本。

60.在本技术的一些实施例中,一个信号转换单元20中的四个dp接口也可以为任意三个dp接口与一个接口转换单元30连接。或是一个信号转换单元20中的四个dp接口全都与同一个接口转换单元连接。

61.需要说明的是,考虑到实际硬件接口的信息传输速率,在本技术的实施例中,对于同一个信号转换单元20来说,信号转换单元20上至少有两个信号输出接口(即两个dp接口)同时与一个接口转换单元30连接。且在本技术的实施例中,一个信号转换单元20为通常为偶数个信号输出接口(即dp接口)同时与同一个接口转换单元30连接。

62.且在上述实施例中,在偶数个信号输出接口(即dp接口)同时与同一个接口转换单元30连接的同时,还需要保证7680/接口数能够整除。这是因为本技术实施例拼接屏显示的是8k及以上分辨率的3d画面,而7680则是8k画面对应的像素数量。

63.在本技术的实施例中,拼接屏显示的是8k及以上分辨率的3d画面,信号转换单元20中具体需要利用多少个信号输出接口,取决于视频画面的带宽以及信号输出接口的信号

传输速率。

64.在一个具体实施例中,一般来说,当dp接口的传输速率为8.1gbps时,两个dp接口就可以传输8k60hz信号;而当dp接口的传输速率为5.4gbps时,四个dp接口才能传输8k60hz信号。

65.通常来说,视频画面的带宽越大,传输视频信号所需的dp接口越多。而dp接口的传输速率越低,传输视频信号所需的dp接口越多。

66.在本技术的一个具体实施例中,信号转换单元20(即p4000)显卡包括四个dp输出接口,且每个dp输出接口的信号传输速率为8.1gbps,此时任意两个dp输出接口与同一个接口转换单元30连接即可。

67.而同一个接口转换单元30(即a10电路)中包括两个第二信号输入接口,即两个dp输入接口。信号转换单元20中的两个dp输出接口,同时与同一个接口转换单元30中的两个dp输入接口连接;同一个接口转换单元30中的两个dp输入接口的信号传输速率同样为8.1gbps。

68.而接口转换单元30(即a10电路)的输出为32lane v-by-one接口,每个lane v-by-one接口的信号传输速率为2.97gbps。当接口转换单元(即a10电路)的输入接口为32lane v-by-one接口时,对应的子显示屏驱动电路40(即cb电路)的输入接口也为32lane v-by-one接口。

69.需要说明的是,在上述实施例中,dp接口、32lane v-by-one是实际的驱动场景中常见的接口;而8.1gbps、5.4gbps、2.97gbps也是比较常规的信号传输速率。

70.在图2所示的拼接屏驱动架构中,拼接屏驱动架构还包括有3d软件(即画面转换模块),而3d软件主要是用于对视频数据进行编解码,将视频信号转换为3d视频信号。同时还包括画面融合软件(即画面融合模块),画面融合软件将进行3d软件编解码之后的rgb原始数据进行处理,对任意子显示屏与周围其他子显示屏的拼缝数据进行处理,保证数据在拼缝处过渡均匀,避免出现模糊错位等现象。

71.需要说明的是,在本技术的一些实施例中,画面转换模块和画面融合模块可以分别为上述实施例所述的3d软件和画面融合软件等装载在计算机内部的软件工具;也可以为其他可以实现相同功能的硬件模块。而为了节省硬件成本,通常利用类型3d软件和画面融合软件等软件工具实现画面转换和融合等功能,

72.在图2所示的实施例中,拼接屏驱动架构还包括同步模块。具体的,同步模块可以为nvidiasync ii卡,而nvidia sync ii卡是p4000显卡中的一部分功能模块;因此nvidiasync ii卡控制的是p4000显卡输出的驱动信号。

73.即在本技术的实施例中,同步模块与信号转换模块连接,同步模块控制信号转换模块输出的驱动信号实现同步。

74.在图2所示的实施例中,同步模块(即nvidia sync ii卡)为两个,而两个同步模块中,一个同步模块控制pc1-pc4,即一个同步模块同时控制多个信号转换模块20;而另一个同步模块控制单独控制pc5。由于同步模块为多个,因此还需要控制多个同步模块之间保持同步。具体地,可以利用网线连接多个同步模块,利用物理方法使得多个同步模块之间保持同步。

75.本技术实施例还提供一种拼接屏驱动方法,利用如上任一项所述的拼接屏驱动架

构进行驱动。具体的,拼接屏包括m*n块子显示屏,拼接屏驱动架构包括:多个信号转换单元和多个用于转换接口的接口转换单元,多个信号转换单元与多个接口转换单元电连接;m*n块子显示屏中每个子显示屏包括至少一个子显示屏驱动电路;

76.多个信号转换单元中每个信号转换单元用于接收外部驱动信号,且将驱动信号发送至所述接口转换单元;接口转换单元用于接收信号转换单元发出的外部驱动信号,且将外部驱动信号发送至子显示屏驱动电路。

77.其中,m和n均为大于或等于一的正整数。

78.本技术实施例提供的拼接屏驱动方法包括:

79.所述信号转换单元接收初始驱动信号,并将所述初始驱动信号转换为所述拼接屏可以显示的驱动信号;

80.所述信号转换单元将所述驱动信号发送至所述接口转换单元,以利用所述接口转换单元实现接口转换;

81.所述接口转换单元将所述驱动信号发送至所述子显示屏驱动电路,以利用所述子显示屏驱动线路控制所述拼接屏显示画面。

82.本技术实施例提供的拼接屏驱动方法,拼接屏驱动架构仅包括多个信号转换单元和多个用于转换接口的接口转换单元,以及多个子显示屏驱动电路;所述多个信号转换单元中每个信号转换单元用于接收外部驱动信号,且将所述驱动信号发送至所述接口转换单元;所述接口转换单元用于接收所述信号转换单元发出的外部驱动信号,且将所述外部驱动信号发送至所述子显示屏驱动电路,使得子显示屏显示画面。整个拼接屏驱动架构仅包括信号转换单元、接口转换单元、子显示屏驱动电路和子显示屏,驱动架构简单,用少量的电路板即可实现拼接屏的驱动,大大降低成本。

83.在本技术的实施例中,由于拼接屏主要显示的是3d画面,所以拼接屏驱动架构还包括画面转换模块,画面转换模块主要用于将初始驱动信号对应的画面转换为3d画面。因此该拼接屏驱动方法还可以包括:画面转换模块接收初始驱动信号,并生成与3d画面对应的驱动信号以将驱动信号发送至信号转换单元。

84.在本技术的另一些实施例中,由于拼接屏是由m*n块子显示屏拼接而成,每一个子显示屏显示的画面拼接后才是完整的画面,因此需要对拼缝处的图像进行处理,使得拼缝处的图像过渡更均匀。本技术实施例提供的拼接屏驱动架构还包括融合模块,因此本技术实施例提供的拼接屏驱动方法还可以包括:融合模块接收来自画面转换模块的驱动信号,并对所述驱动信号对应的画面进行融合处理,使得拼缝处画面过渡均匀,避免出现错位模糊的问题。

85.需要说明的是,外部的驱动信号先发送到画面转换模块转换为3d画面后,再进行融合处理。

86.以下结合图2具体描述本技术实施例中的拼接屏驱动方法。在图2所示的拼接屏驱动架构中包括五个计算机设备pc1-pc5,而每个pc中均包括一个p4000显卡、3d软件、融合软件。此外还包括3*3块子显示屏(图中未示出),而每个子显示屏中均包括一个a10电路和cb电路,分别为a101-a109以及cb1-cb9。

87.且任意一个计算机设备例如pc5中还额外装有两个sync ii同步卡用于同步,且两个sync ii同步卡利用网线连接;两个sync ii同步之间也实现同步。

88.对于图2所示的拼接屏驱动架构来说,以cb1对应的显示屏为例,3d软件接收外部的初始驱动信号,并将初始驱动信号转换为3d的rgb的视频原始数据。而融合软件接收3d软件发出的rgb视频原始数据并进行处理,对cb1拼接屏与周围其他显示屏的拼缝处的数据信息处理,保证视频数据在拼缝处过渡均匀。

89.而融合处理完成后的驱动信号发送至p4000显卡,p4000显卡对驱动信号进行处理,将驱动信号转换为拼接屏可以显示的驱动信号。而转换后的驱动信号通过p4000显卡中的两个dp接口输出到a10电路中。

90.而a101电路的通过自身的dp接口接收到p4000显卡输出的驱动信号,又通过自身的vbo接口发送给cb1电路。a10电路本身并不处理驱动信号,a10电路主要是起到接口转换的作用。而cb1通过自身的vbo接口接收到a101电路驱动信号后,将驱动信号输出到子显示屏中实现显示。

91.对于cb2-cb9来说,均利用上述方法接收到驱动信号并实现显示。

92.需要说明的是,在本技术的实施例中,pc1-pc5接收到的驱动信号通常需要保持同步。且利用两个nvidia sync ii卡进一步控制驱动信号保持同步。

93.在本技术的实施例中,nvidia sync ii card1同时控制pc1-pc4输出的驱动信号保持同步,而nvidia sync ii card2单独控制pc5输出的信号;又由于nvidia sync ii card1和nvidia sync ii card2之间保持同步,因此使得pc1-pc5输出的驱动信号均可以保持同步。

94.上述实施例仅仅是保证了不同显卡输出的驱动信号之间保持同步,在驱动信号后续传输的过程中仍要保持同步。具体的,需要a101-a109输出的驱动信号之间保持同步。

95.在本技术的实施例中,可以为a101电路输出同步信号,而a102-a109接收a101发出的同步信号,并根据该同步信号调整自身的驱动信号的时序,使得不同a10电路中的驱动信号保持同步。

96.具体的,a101电路输出vsync信号,而a102-a109接收a101发出的vsync信号用于帧同步;a101-a109基于vsync信号在一帧画面中的非显示时段(vblank区域),重新生成并输出当前帧画面的时序信号de,而视频信号与新的实训信号de对齐并同时输出。

97.在本技术的实施例中,拼接屏不仅显示3d画面,还可以显示8k及以上分辨率的3d画面。请结合图2,对于图2所示的拼接屏驱动架构来说,若3*3的子显示屏均显示8k3d画面,则对于pc1来说,接收到的外部驱动信号为两路8k60hz的信号,即3d软件处理的是2*8k60hz的信号。而3d软件处理后发给融合软件的同样为2*8k60hz的信号;融合软件又将处理后的2*8k60hz的信号发送给p4000显卡。由于一个p4000显卡同时控制两个子显示屏,此时2*8k60hz的信号分别输入两个接口转换单元30中,每一个接口转换单元30接收到的信号为8k60hz的信号。

98.对于本技术提供的实施例来说,若是每个子显示屏均可以接收并显示8k信号,实际上子显示屏接收并显示的8k4k分辨率的画面。而当拼接屏为3*3的结构时,整个拼接屏水平与垂直方向的子显示屏的数量各为3,拼接屏整体显示的画面为(8k*3)(4k*3),即拼接后的画面整体分辨率为24k12k。

99.具体的,由于每条视频链路只驱动一个8k4k的信号,3x3共9条视频链路同时输出,就可以输出(8k*3)(4k*3)共24k12k的数据。而若是m*n块子显示屏为其他的数量,也可以对

应显示其他不同分辨率的3d画面。

100.在上述实施例中,由于每个pc最多只能支持2个sync ii同步卡,如果子显示屏的数量超过两个sync ii同步卡支持的系统,就需要在其他的pc上额外增加sync ii同步卡和显卡。

101.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见上文针对其他实施例的详细描述,此处不再赘述。

102.具体实施时,以上各个单元或结构可以作为独立的实体来实现,也可以进行任意组合,作为同一或若干个实体来实现,以上各个单元或结构的具体实施可参见前面的方法实施例,在此不再赘述。

103.以上各个操作的具体实施可参见前面的实施例,在此不再赘述。

104.以上对本技术实施例所提供的一种拼接屏驱动架构及驱动方法进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上,本说明书内容不应理解为对本技术的限制。