1.本发明属于粘结片领域,具体涉及一种包含中空陶瓷粉的低介电常数粘结片及制备方法。

背景技术:

2.随着集成电路的广泛应用,电子产品向小型化、多功能和高性能发展,pcb作为电路互连不可缺少的组成元件,必然面临向高频、高速特性转变。因此,以往的单层电路板以无法满足需求,多层电路板是必然产物。粘结片结合了ptfe(聚四氟乙烯)基片介质损耗正切较低,环氧等热固树脂的半固化片粘结性较好的优势,这保证了多层电路板的在信号传输方面的稳定性与可靠性。

3.中国专利cn112538184a公开了一种粘结片的制备方法及其应用,在等离子体处理后的ptfe基片的上下表面分别辊涂介电树脂胶液的得到粘结片,该粘结片流动性好,粘结稳定性高。但是,该粘结片的ptfe基片采用玻璃纤维布浸渍ptfe乳液得到,玻璃纤维布增强材料存在经纬编织密度的差异,得到的粘结片也会严重影响高频电路信号传输的一致性和稳定性。

4.中国专利cn102206399a和cn110698112a均公开了一种低介电常数复合介质基板的制备方法,低介电常数复合介质基板有利于信号的高速、低延迟、无损耗传输,其在实现多层化使用过程中必须选择合适介电常数的粘结片共同使用。因此,获得一种综合性能优异,介电常数可与低介电常数微波复合介质基板相匹配的多层板用层间粘结材料,对整个电路基板行业的发展都至关重要。

技术实现要素:

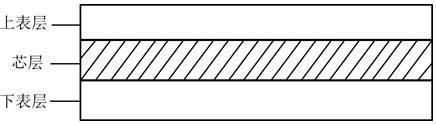

5.针对现有技术的不足,本发明所要解决的技术问题是提供一种包含中空陶瓷粉的低介电常数粘结片及制备方法,粘结片包括芯层、上表层和下表层;芯层为ptfe基片;ptfe基片为涂布工艺得到的芯层薄膜;上表层和下表层为含中空填料的碳氢树脂层;碳氢树脂层采用浸渍工艺形成,厚度均匀,孔隙率低,效率较高。该粘结片具有致密度高、介电性能均匀稳定、粘结强度高等特性,可以满足多层板信号高频化需求及稳定性和可靠性要求。

6.本发明采用的技术方案是:一种包含中空陶瓷粉的低介电常数粘结片,所述粘结片包括芯层、上表层和下表层,所述芯层厚度为40um~150um;所述上表层和下表层的厚度均为40um~150um;所述芯层,由以下质量百分比的原料组成:无机填料:45~85wt.%;含氟树脂:10~45wt.%;偶联剂:1~5wt.%;表面活性剂:0.5~5wt.%;所述上表层和下表层,由以下质量百分比的原料组成:

中空填料:40~65wt.%;碳氢树脂:30~55wt.%;有机过氧化物引发剂:0.1~5wt.%。

7.所述的无机填料为氢氧化铝、二氧化硅、二氧化钛、钛酸钡、滑石粉、云母、硅微粉或浮石粉中的任意一种或几种的混合物。

8.所述的含氟树脂为聚四氟乙烯、乙烯

‑

四氟乙烯共聚物、乙烯

‑

三氟氯乙烯共聚物、聚三氟氯乙烯、聚偏氟乙烯、聚氟乙烯中任意一种或者至少两种的混合物。

9.所述的偶联剂可为硅烷偶联剂、钛酸酯偶联剂、锆酸酯偶联剂中的一种或几种的混合物。

10.所述的中空填料为空心结构的二氧化硅、二氧化钛、二氧化铝、钙钛矿型陶瓷粉的单一物质或两种及两种以上的混合物,平均粒径小于20um。

11.所述的碳氢树脂为聚丁二烯、聚异戊二烯、丁二烯

‑

苯乙烯共聚物、聚苯醚或乙丙橡胶中的一种或几种的混合物。

12.所述有机过氧化物引发剂为氧化苯甲酰、氧化十二酰、过氧化二异丙苯或过氧化苯甲酸叔乙酯任意一种或几种的混合物。

13.一种包含中空陶瓷粉的低介电常数粘结片的制备方法,步骤如下:所述芯层制备工艺过程:步骤1:将表面活性剂与去离子水混合,在20r/min~300r/min转速条件下搅拌5min~30min,然后加入偶联剂,在20r/min~300r/min转速条件下搅拌5min~30min,再加入无机填料,在200r/min~1000r/min转速条件下搅拌20min~60min,在此完成对无机填料的改性,最后加入含氟树脂,在200r/min~800r/min转速条件下搅拌10min~60min,得到混合浆料;步骤2:将步骤1得到的混合浆料涂覆在可剥离的支撑载体上,通过控制涂覆速度、炉温制得ptfe薄膜,然后通过隧道窑200℃~400℃进行烧结30min~100min得到ptfe芯层薄膜;步骤3:将得到的ptfe芯层薄膜进行表面活化处理,得到表面活化处理后的ptfe芯层薄膜;所述上表层和下表层制备工艺过程:步骤4:将中空填料、碳氢树脂、有机过氧化物引发剂分别加入二甲苯溶剂中,在转速50r/min

‑

500r/min条件下充分搅拌30min

‑

480min得到混合胶液;步骤5:将步骤4得到的混合胶液通过浸渍烘干工艺在步骤3得到的表面活化处理后的ptfe芯层薄膜上、下表面以0.1m/min~10m/min浸渍,烘道温度为50℃~400℃,最后在50℃~260℃下对其进行固化30min~100min得到粘结片,最终得到包含中空陶瓷粉的低介电常数粘结片,介电常数低于2.20,介电损耗低于0.0021。

14.本发明的有益效果是:1)本发明制备的粘结片是在非玻璃纤维编织布上涂布得到芯层,这有利于信号传输的稳定性与一致性,避免了信号传输过程中的“玻纤效应”;然后在芯层上浸渍得到上下表层,该方法制备工艺简单,环境友好,生产效率较高,有利于实现工业化连续生产。

15.2)本发明通过向碳氢树脂体系中引入中空填料,降低了粘结片的介电常数,使粘结片的介电常数低于2.20,介质损耗低于0.0021。该粘结片具有较高且稳定的粘结强度,综

合性格优异,可以满足多层板的使用和性能需求。

附图说明

16.图1为本发明粘结片的结构示意图。

具体实施方式

17.实施例1一种包含中空陶瓷粉的低介电常数粘结片,粘结片包括芯层、上表层和下表层,其中芯层厚度为55um;上表层和下表层的厚度均为130um。

18.粘结片的芯层由以下质量百分比的原料组成:65wt.%二氧化硅填料、30wt.%聚四氟乙烯、1.5wt.%硅烷偶联剂、3.5wt.%表面活性剂。

19.粘结片的表层由以下质量百分比的原料组成:65wt.%空心结构的二氧化硅、30wt.%聚丁二烯、5wt.%氧化十二酰。

20.一种包含中空陶瓷粉的低介电常数粘结片的制备方法,步骤如下:芯层制备工艺过程:步骤1:将表面活性剂与去离子水混合,在50r/min转速条件下搅拌15min,然后加入偶联剂,在50r/min转速条件下搅拌15min,再加入二氧化硅填料,在400r/min转速条件下搅拌40min,在此完成对二氧化硅填料的改性,最后加入聚四氟乙烯,在250r/min转速条件下搅拌20min,得到混合浆料。

21.步骤2:芯层薄膜的形成:将步骤1得到的混合浆料涂覆在可剥离的支撑载体上,通过控制涂覆速度、炉温制得ptfe薄膜,然后通过隧道窑360℃进行烧结,60min,得到ptfe芯层薄膜。

22.步骤3:将得到的ptfe芯层薄膜进行表面活化处理,得到表面活化处理后的ptfe芯层薄膜。

23.表层制备工艺过程:步骤4:混合浆料的制备:将空心结构的二氧化硅、聚丁二烯、氧化十二酰分别加入二甲苯溶剂中,在转速150r/min条件下充分搅拌100min,得到混合胶液。

24.步骤5:将步骤4得到的混合胶液通过浸渍烘干工艺在步骤3得到的表面活化处理后的ptfe芯层薄膜上、下表面以0.5m/min浸渍,烘道温度为120℃,最后在220℃下对其进行固化40min,得到粘结片最终得到包含中空陶瓷粉的低介电常数粘结片,介电常数为2.16,介电损耗为0.0032,剥离强度为1.05 n/mm。

25.实施例2一种包含中空陶瓷粉的低介电常数粘结片,粘结片包括芯层、上表层和下表层,其中芯层厚度为80um;上表层和下表层厚度均为80um。

26.粘结片的芯层由以下质量百分比的原料组成:54wt.%二氧化硅填料、42wt.%聚四氟乙烯和聚三氟氯乙烯、1.5wt.%硅烷偶联剂、2.5wt.%表面活性剂。

27.粘结片的表层由以下质量百分比的原料组成:

48wt.%空心结构的二氧化钛、50wt.%聚丁二烯和聚异戊二烯、2wt%的氧化苯甲酰。

28.一种包含中空陶瓷粉的低介电常数粘结片的制备方法,步骤如下:芯层制备工艺过程:步骤1:将表面活性剂与去离子水混合,在100r/min转速条件下搅拌30min,然后加入偶联剂,在160r/min转速条件下搅拌25min,再加入二氧化硅填料,在600r/min转速条件下搅拌30min,在此完成对无机填料的改性,最后加入聚四氟乙烯、聚三氟氯乙烯,在500r/min转速条件下搅拌30min,得到混合浆料。

29.步骤2:将步骤1得到的混合浆料涂覆在可剥离的支撑载体上,通过控制涂覆速度、炉温制得ptfe薄膜,然后通过隧道窑340℃进行烧结70min得到ptfe芯层薄膜。

30.步骤3:将得到的ptfe芯层薄膜进行表面活化处理,得到表面活化处理后的ptfe芯层薄膜。

31.表层制备工艺过程:步骤4:将空心结构的二氧化钛、聚丁二烯和聚异戊二烯、氧化苯甲酰分别加入二甲苯溶剂中,在转速250r/min条件下充分搅拌150min,得到混合胶液;步骤5:将步骤4得到的混合胶液通过浸渍烘干工艺在步骤3得到的表面活化处理后的ptfe芯层薄膜上、下表面以2m/min浸渍,烘道温度为180℃,最后在260℃下对其进行固化30min,得到粘结片,最终得到包含中空陶瓷粉的低介电常数粘结片,介电常数为2.00,介电损耗为0.0018,剥离强度为1.42n/mm。

32.实施例3一种包含中空陶瓷粉的低介电常数粘结片,粘结片包括芯层、上表层和下表层,其中芯层厚度为120um;上表层和下表层厚度均为45um。

33.粘结片的芯层由以下质量百分比的原料组成:80wt.%二氧化硅填料、15wt.%聚四氟乙烯和乙烯

‑

三氟氯乙烯共聚物、2.0wt.%硅烷偶联剂、3.0wt.%表面活性剂。

34.粘结片的表层由以下质量百分比的原料组成:34wt.% 空心结构的二氧化硅、65wt.%聚异戊二烯和聚丁二烯、1wt%的过氧化二异丙苯。

35.一种包含中空陶瓷粉的低介电常数粘结片的制备方法,步骤如下:芯层制备工艺过程:步骤1:将表面活性剂与去离子水混合,在120r/min转速条件下搅拌30min,然后加入偶联剂,在200r/min转速条件下搅拌25min,再加入二氧化硅填料,在600r/min转速条件下搅拌30min,在此完成对无机填料的改性,最后加入乙烯

‑

三氟氯乙烯共聚物,在350r/min转速条件下搅拌45min,得到混合浆料。

36.步骤2:将步骤1得到的混合浆料涂覆在可剥离的支撑载体上,通过控制涂覆速度、炉温制得ptfe薄膜,然后通过隧道窑330℃进行烧结60min得到ptfe芯层薄膜。

37.步骤3:将步骤2得到的ptfe芯层薄膜进行表面活化处理,得到表面活化处理后的ptfe芯层薄膜。

38.表层制备工艺过程:步骤4:将空心结构的二氧化硅、聚异戊二烯和过氧化二异丙苯分别加入二甲苯溶

剂中,在转速300r/min条件下充分搅拌120min,得到混合胶液;步骤5:将步骤4得到的混合胶液通过浸渍烘干工艺在步骤3得到的表面活化处理后的ptfe芯层薄膜上、下表面以2m/min浸渍,烘道温度为160℃,最后在280℃下对其进行固化45min,得到粘结片,最终得到包含中空陶瓷粉的低介电常数粘结片,介电常数为2.28,介电损耗为0.0032,剥离强度为0.86n/mm。

39.表1为实施例1

‑

3对比及测试结果

表1特性测试方法如下:介电dk和介电损耗df:按照ipc

‑

tm

‑

6502.5.6.2方法中的“接受态”实验条件测定板材的电气性能。

40.剥离强度:按照ipc

‑

tm

‑

6502.4.8方法中的“热应力后”实验条件测定板材的剥离强度。

41.由表1可以看出,实施例1到实施例3制备的板材,实施例2具有更好的电气性能和更高的剥离强度,表明提高中空填料比例至65%可使介电材料具有较低的介电常数。

42.综上可知,本发明的介电材料可以达到低介电常数、高剥离强度等,可以满足低介电材料的性能要求。